Nanoelec has developed groundbreaking research in the area of micro and nanoelectronics since its inception in 2012, resulting in state of the art demonstrators and technology platforms. Mentor, a Siemens business, as the sole EDA (Electronics Design Automation) partner of Nanoelec, is providing design & verification tools for the benefit of the research institute’s IRT Nanoelec designer community. In addition to providing this valuable support, Mentor also uses the community’s feedback to improve continually its design tools in the context of their performance in use on IntAct sophisticated demonstrators. Juan Rey, VP Engineering at Mentor Design2Silicon Division, focuses on accurate physical verification of innovative 3D-IC designs.

How has Mentor’s Calibre 3DSTACK been an essential tool for the architecture design of Intact, the 3D manycore circuit partitioned using an active interposer presented Nanoelec last year?

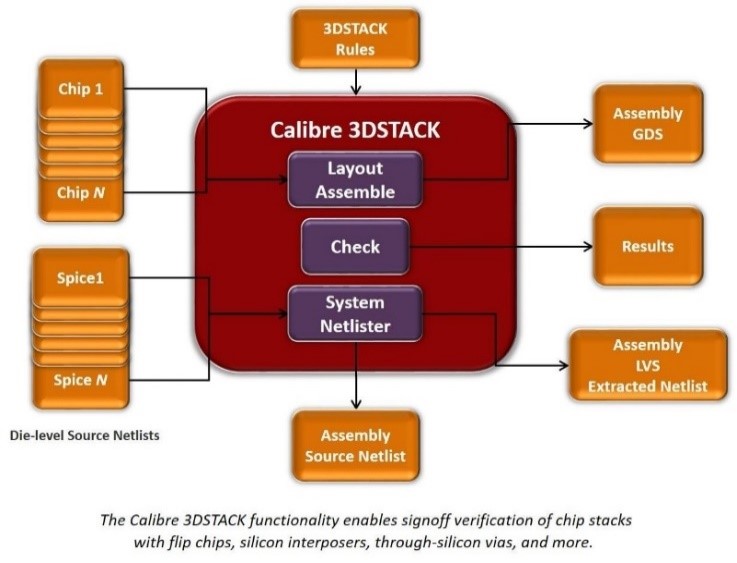

The accurate Physical Verification of such highly complex demonstrators requires efficient and high performance engines made available through a leading edge product suite. A fundamental tool in the signoff verification of 2.5D/3D-IC designs is Calibre 3DSTACK. Calibre 3DSTACK extends Calibre die-level signoff verification to enable complete signoff verification of a wide variety of 2.5D and 3D stacked die assemblies. With Calibre 3DSTACK, designers can perform signoff DRC and LVS checking of complete multi-die systems at any process node without breaking current tool flows or requiring new data formats, significantly reducing time to tapeout.

How does Mentor’s Calibre 3DSTACK benefit the Nanoelec IntAct demonstrator?

Calibre 3DSTACK was used extensively during the IntAct demonstrator signoff/final verification (before manufacturing), allowing for the capture of errors that traditional ‘2D’ tools would have missed given the complexity of such design. The consequences of failing to capture these errors during the verification stage could have been substantial, resulting in either a functionality/specification limitation or even worse, a complete chip failure.

Does Mentor also provide innovative tools for reliability and physical stress analysis?

In addition to providing this signoff ‘stamp’ to IRT Nanoelec demonstrators, Mentor is also proposing innovative prototype tools for IRT Nanoelec partners. Thermal analysis for 2.5D/3D has been one strong research axis over the past years, allowing CEA-Leti to perform architectural studies for their future demonstrators. 2.5D/3D Reliability and physical stress analysis are other topics of interest that Mentor and Nanoelec partners will continue to study over the coming months.