# Scientific & technical highlights

2024 EDITION

# AGENDA

### P. 17 From 3D integration to images

### Smart imager

# Displed

P.32

### **Photonic** sensors

P.44

#### Innovation in silicon photonics: from design tools to mass production processes

P.46 A photonic sensor to titrate ethanol

P.48 Design kits and model libraries for photonics process

P. 48 Verilog-A language to simulate photonic integrated circuits

P.49 Large-scale lidar

P.49 Operating at 1550nm wavelenght

P.50 Low-power low-loss phase modulators for Lidars

**P.53** Taking photonic integration technologies further

P.55 Microleds based on III-V materials

P.56 Packaging and Testing of Photonic Integrated Circuits (PICs)

**P.4 Identity of** the institute Exploring the future of electronics

#### **P.6 Trends** notes on Nanoelec

P. 6 Towards heterogeneous integration

P.7 Proven economic impact

P.8 Moving forward together to give meaning to our industry

P.10 18 months of highlights

#### **Three-layer** integration breakthrough for Al-embedded **CMOS** image sensors

P.20 New products being manufactured

P.20 A frugal neuromorphic sensor for the IoT

P. 21 Lightweight event stream classification

P.23 Efficient in-sensor processing based on advanced 3D technologies

P.23 Infrared opting for 300mm

P. 24 Hybrid bonding pitch reduction

P.26 Achieving 3-layer stacking integration for future smart imagers

P.29 An imager built on a disruptive 3-layer architecture

P.30 Bridging the gap between neural network exploration and hardware implementation

Towards a renewal of display

technology in Europe

P.34 Smart-pixel life cycle analysis

P.34 Hybridizing GaN microleds and CMOS circuits

P.35 The move to flexible displays

P.37 Picking and placina dies on a substrate

P.40 New tool for advanced hybrid bonding

P.42 RGB pixels work

### Pulse

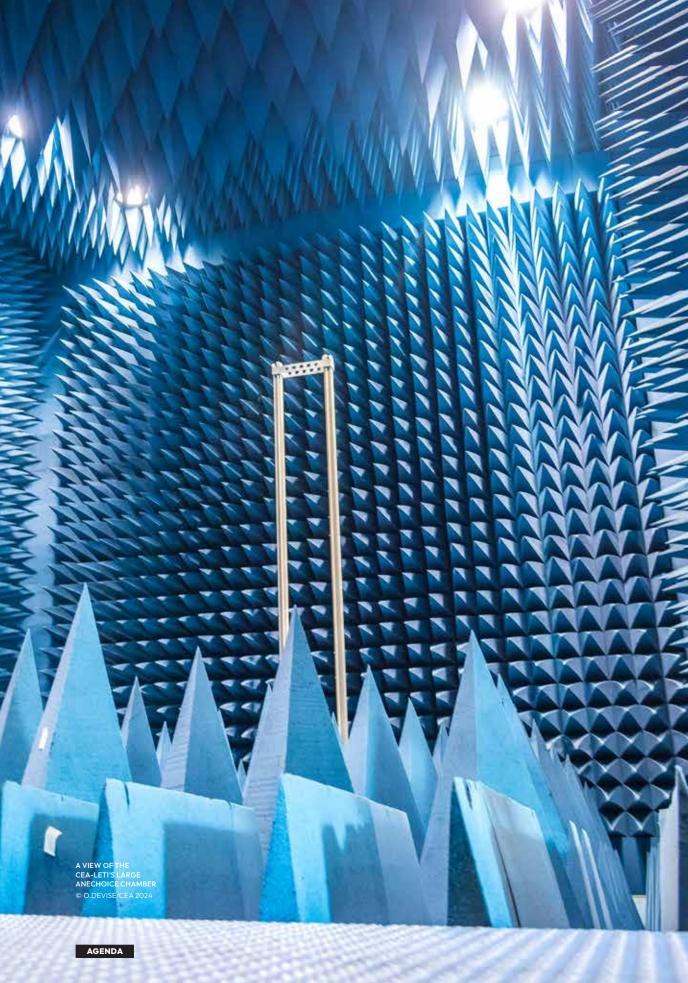

### **Characterisation**

### Technology

### Human capital & training design

#### **P.58**

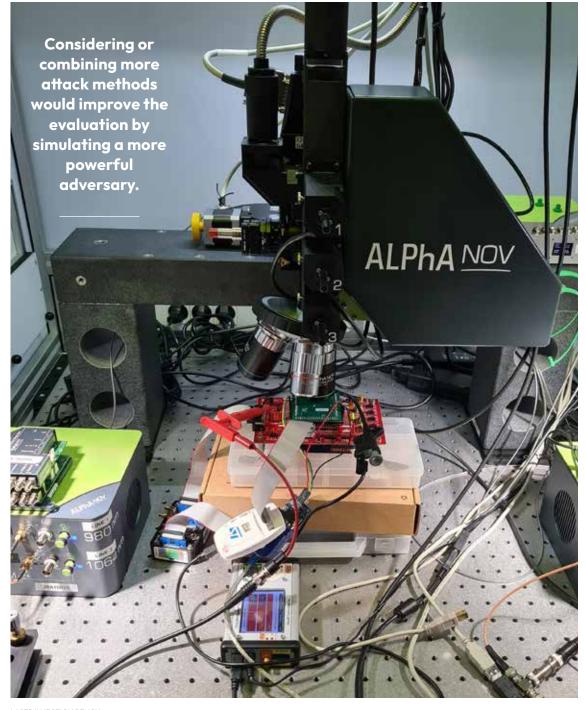

#### Solutions for more secure digital components

P.60 Secure implementation of AI in embedded systems

P.62 Automatic generation of test mahine

P.63 A new open-source hardware processor standard

P.64 Increasing the security of data streams in the IOTP

P.65 An intrinsically secure processor

P.66 Safe and autonomous overhead crane

P.68 Perception solutions for autonomous vehicles

P.69 Secure hardware implementation of Blockchain

P.70 Ultra-secure critical IoT

P.71 Secure implementation of postquantum encryption

P. 73 Simulating cyberattacks on industrial control systems

P. 73 Microprocessor security

P. 74 Digitalizing products and services for SMEs

P. 75 Pulse at international events

#### **P.78**

### Correlative microscopy

P.80 Resistance to irradiation of electronic components and circuits

P.82 Defects in SiC epitaxial wafers

P.84 Investigating defects in diamond

P.86 Single-event upsets induced by thermal neutrons in SRAMs

P.89 Challenging the reliability of Commercial-Off-The-Shelf items for the New Space

P.90 A national symposium on characterisation

P.91 A european workshop on irradiation

P.92 French reliability center

P.92 A gateway to large-scale instruments dedicated to electronics industry needs

P.93 Injection of system faults

P.94 In Europe. characterisation platforms complement each other

### P.96

Responsible integration of digital devices in SME processes & products

#### P.98 Eaysytech

P.98 Automatic detection of buried networks

P.100 Predictive maintenance for industrial microwave ovens

P. 100 Designedin electronic circuit optimization

P.102 Predictive maintenance of mechanical parts

P.104 A frugal thermal detector to warn of abnormal heating in industrial processes

P.105 System Lab/ Addvisia

P.107 Displaying strata in the snowpack

P.108 Revealing thermoregulation by vascularization of the skin

P.109 Umpiring & movement analysis in tennis

**Sustainable** development as a driver of innovation

P.114 Electronics industry attractiveness

P.115 Rational eco-design of electronics

P.118 Eco-design for **Power Electronics**

P.118 Building digital trust

P.119 Innovative business models

P.120 Anticipate the introduction of digital product passport

P.122 A new sustainable electronics magazine

P.126 Interactive screens and the rebound effect

P.128 A data-driven approach for comprehensive LCA and effective eco-design of the IOT

P.130 Sustainable development / P.134 Artificial intelligence / P.137 International & Europe / P.142 Graphic designers sketch our industry / P.144 Governance / P.145 Operational committee / P.146 Scientific council

# Exploring the future of electronics

# IRT Nanoelec runs multi-partner programs to make the electronics industry more competitive and greener, and thus contribute to the sustainable development of society.

The Nanoelec technological research institute (IRT) is a consortium of private and public sector players, hold by CEA. Our mission is to help companies create value and enable their products to stand out on the digital transition stage.

Nanoelec contributes to the competitiveness of the electronics industry, particularly in France. Based in Grenoble, the institute is a world-class hub for research, innovation and production in its field.

Our R&D programs are built jointly by representatives from the academic and industrial worlds. They deal with the design and development of new processes, systems and components in the following fields:

- → photons & imaging: photonic sensors, new-generation displays and smart image sensors,

- → digital trust: cybersecurity for connected objects, and characterization of components and systems by means of large instruments.

Nanoelec also runs engineering and technological dissemination training programs for SMEs with the support of the territorial public authorities. We implement open innovation techniques as well as more conventional technological development methods.

Given the pervasive nature of digital technologies, Nanoelec is in contact with actors from all sectors ranging from goods to services, industry, infrastructures, and consumer products, as well as transportation, environment and health.

Nanoelec is a member of FIT, a hub of technological research institutes (IRTs) and energy transition institutes (ITEs) set up by the French Government and financed by the invest plan for future (France 2030). The network of institutes was created to pool academic and industrial players who could run collaborative R&D and innovation projects aimed at boosting the competitiveness of the French economy. ◊

Photo TEST OF A NEW COATING ON A SILICON WAFER A.HAVRET/CEA

# Microelectronics innovation

→ Carry out world-class collaborative R&D in selected areas to produce innovative components and embedded systems: imagers, displays, photonic on Si and digital trust & security

→ Develop and transfer these technologies to create the electronic circuits and components of the future

→ Give industry players access to development, prototyping and advanced characterization resources

## Technology dissemination

→ Help businesses in the field of information and communication technologies meet the challenges of IoT through digital trust and security

- → Provide expertise to help SMEs from various industrial sectors build new products and services with innovative components and embedded software

- → Promote cooperation between SMEs, mid-caps and large companies

- → Unveil new applications comprising environmental and social impact assessments by collaborative innovation

# Development of human capital

- → Attract young people to jobs in electronics that contribute to sustainable development

- → Work with partners on parity and workplace equality

- → Design training courses to meet current needs

- → Anticipate future skill requirements in the sector: sustainability, cross-skills, social and professional communities for innovation

### NANOELEC AT A GLANCE

A consortium of **22** public & private members as of December 2023

€52M average annual budget Yearly average 2015-2023 247 patents and 57 software filed since 2012

324 associated partners including 245 SMEs since 2012 704 scientific or technical publications & communications

since 201

**213** full-time jobs Yearly average 2015-2023

# Trends notes on Nanoelec

by Sébastien Dauvé, Hughes Metras and Sandrine Maubert.

#### SÉBASTIEN DAUVÉ

DIRECTOR OF CEA-LETI AND PRESIDENT OF THE NANOELEC STEERING COMMITTEE

© C.TRESCA/CEA

# Towards heterogeneous integration

By Sébastien Dauvé, President of the Nanoelec Steering Committee

Nanoelec has been active in the Grenoble ecosystem since 2012, and is your partner for boosting the competitiveness of reference players in the electronics sector. It represents an invaluable asset at a time when sovereignty and excellence are more than ever on the agenda in Europe.

The institute brings a strong capacity for acceleration on a selection of technological developments addressing highly specific medium-term challenges of interest to a large number of industrial partners. In so doing, Nanoelec supplements other France 2030 investments which notably addresses the development of FD-SOI technology, whether in Crolles for the industrial capability ramp-up, or at CEA-Leti for the FD10nm future generation.

For its future programs, the institute is thus actively positioned on heterogeneous integration, with the ability to contribute to a variety of applications markets, whether in the field of embedded computing, high performance computing, imagers, displays and telecommunications.

$\rightarrow$

7

"Highly differentiating solutions for Nanoelec partners, on the road towards more responsible electronics." Heterogeneous integration is a technological solution that opens the door to efficiently embedding AI components. It is also possible to envisage more frugal manufacturing technologies and more repairable, recyclable and reusable components. This will enable highly differentiating technologies for Nanoelec partners on the road towards more responsible electronics. This trend in the sector will require ambitious developments to meet the needs of industry and market. At stake are the sovereignty of the ecosystem, to ensure that Europe and France have the expertise needed for essential components and systems. ◊

HUGHES METRAS, DIRECTOR OF NANOELEC © P.JAYET/CEA

1. Under the France 2030 investment plan, the "First plant" call for projects aims to speed up the construction of pilot sites and/or industrial production by innovative start-ups, SMEs and mid-caps.

# Proven economic impact

By Hugues Metras, Director of Nanoelec

In 2023, IRT Nanoelec continued to deploy the roadmaps defined for the period 2021-2025. We are expecting significant technological advances: hardware and software technology bricks for imagers, in particular with an event-based imager demonstrator, a technology demonstration to validate the feasibility of a novel concept for displays including tools for mass transfer of microleds, functional components for lidars using silicon photonic technologies, advances in the field of postquantum cryptology, and security of neural networks embedded in components and systems.

In terms of economic impact, our partners move forward. STMicroelectronics is continuing to deploy its 3D integration technologies with new imager products; Prophesee has launched a new imager this year; Aledia has started to install its production lines in its plant near Grenoble and four companies accompanied by the Easytech initiative won first plant project awards<sup>(1)</sup>: Limatech, Dracula, CIXI and BeFC; these projects have all raised significant funds.

Our mission is to contribute to the competitiveness of the electronics sector. Beyond our technological R&D milestones, we are intensifying our commitment to questions related to human capital and to the responsibility of the sector. Since 2023, we have regularly taken part in the thematic working groups of the national industry's strategic committee on employment, training and eco-innovation. We are also continuing our commitment to debate and exert influence over questions of gender and professional equality. The institute is also moving forwards on the road to sustainable electronics: in 2024. our commitment to the Convention des Entreprises pour le Climat (Convention of businesses for the climate) will contribute to structuring roadmaps for the 2030 time-frame.

FIRST TOOLS FOR MICROLED MASS TRANSFER UNDER THE NANOELEC/DISPLED PROGRAM © A.HAVRET/CEA 2024

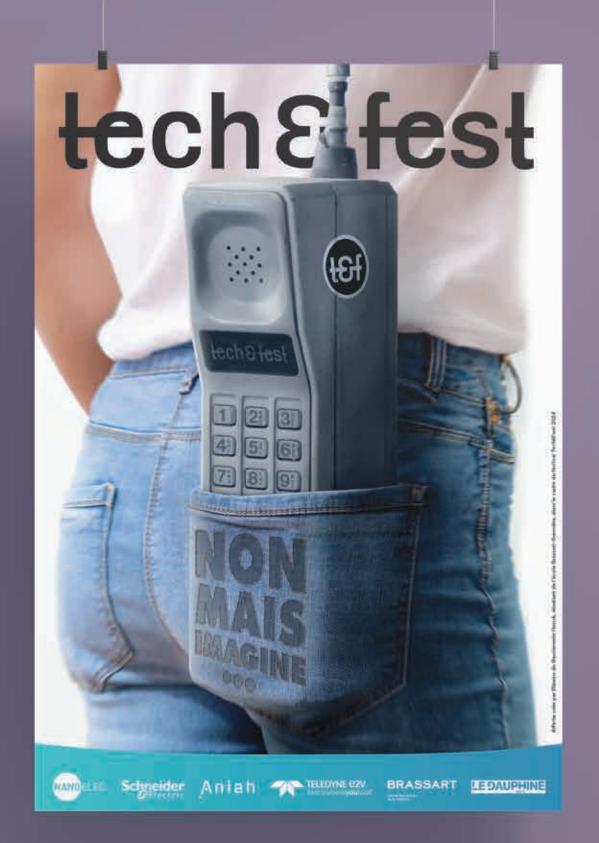

2. Creations from students of the Brassart school with Schneider Electric, Teledyne E2V, Aniah, and the Dauphiné libéré newspaper, for the Tech&Fest 2024 festival. Publications and communications were presented at high-profile conferences, including Display Week, Date, Risc-V EU, ECTC. Nanoelec was also behind the nationwide deployment of the Carac23 conference in close partnership with five other FIT institutes: Saint-Exupéry Railenium Supergrid, IPVF and Ines.2S.

Finally, to promote the image of our industry and make it more visible, Nanoelec was behind the *"Microelectronics for living in a better world"*<sup>(2)</sup> poster competition, with some entries being visible on the cover and throughout the chapters of this report. ◊ "We are firmly expecting significant technological advances: Embedded Al imagers, new concepts for displays, lidars using silicon photonic technologies, post-quantum cryptology, and secured Al embedded in components and systems."

SANDRINE MAUBERT, DEPUTY DIRECTOR OF NANOELEC © P.JAYET/CEA

# Moving forward together to give meaning to our industry

Sandrine Maubert, Deputy director of Nanoelec

At the request of its industrial partners and further to a recommendation by the Government, Nanoelec is undertaking a large number of actions which fall under the United Nations sustainable development goals. We are aiming to combine our mission of technological innovation for competitiveness with the search for relevant and meaningful initiatives with our stakeholders in the light of the planet's finite resources.

The work of life cycle assesment in the R&D phase within the Displed project, the aim of which is to lay the groundwork for relocation of a display manufacturing industry to Europe, was the subject of a publication during Display Week 2023, a major event for the displays sector.

Eco-innovation assessments at the beginning of projects are being rolled out within the Easytech system with Minalogic. In this report, we present a selection of four of the most recent Easytech projects.

Through various European initiatives, we are looking at reducing electronic waste by addressing product end-of-life issues as of the design stage (EECONE project), the attractiveness of the industry for green electronics (GreenChip) and an ethical and sustainable approach to hardware technologies, whether for police investigations (Poliiice) or labor (Earashi).

9

Addressing challenges of sustainable development are among the key factors for the attractiveness of the industry. In 2023, Nanoelec and Minalogic co-organized the very first regional attractiveness forum for the electronic sector, which brought together 130 professionals from the industry, from training and from the institutional world, this was a way of answering the questions from students and young professionals in the sector. **◊**

# Four work areas for sustainable development in 2023

IRT Nanoelec launched a number of cross-cutting work actions in sustainable development, in response to the recommendations of our stakeholders. The IRT Nanoelec Sustainable Development action plan comprises four work areas.

#### 2 OF THEM CONCERN ECO-INNOVATION FOR R&D PROJECTS:

→ A quick and inexpensive diagnosis solution for companies looking to run a project within the Easytech framework;

→ An eco-innovation tool in the R&D phase for the production sector of next-generation displays, currently under development with Aledia as part of the Displed program.

Arra - Dimites Statistic Immediate & Process

#### OF THESE WORK AREAS CONCERN MANAGEMENT, SKILLS AND GOVERNANCE:

2

→ Events to promote greater gender equality in the electronics sector;

→ Design of training courses for sustainable electronics, through the Human Capital and Training Design program.

"A competitive sector is one that satisfactorily manages its environmental and societal impact."

REGIONAL FORUM FOR THE ATTRACTIVENESS OF THE ELECTRONICS SECTOR, ORGANIZED BY NANOELEC AND MINALOGIC, ON MAY 11, 2023 IN GRENOBLE, UNDER THE AUSPICES OF SAMY SISAÏD, SUB-PREFECT AND COORDINATOR OF FRANCE 2030 AND THE INDUSTRIAL PROJECTS ACCELERATION PROGRAM © P.JAYET/CEA 2023

# Highlights

### **JANUARY 2023**

# Sustainable Electronics

JANUARY 27 | Nanoelec/Human Capital & Training Design program conducted a seminar: "Technology usages: how does sustainable development influence decisionmaking?"

With contributions from Schneider Electric, Grenoble-Ecole de management, Grenoble-INP and CEA.

#

**FEBRUARY 2023**

**Photonics West**

**FEBRUARY 1** | During his talk on next-gen photonics platforms

Photonics Program Manager @

CEA-Leti, presented III-V material

platforms through direct bonding

(wafer-to-wafer & die-to-wafer).

As part of a Nanoelec initiative,

200- and 300-mm wafers. It is CMOS-compatible and ready for large-scale integration.

for emerging applications,

Bertrand Szelag, Integrated

integration on Si photonics

the process is available for

# Attractiveness

FEBRUARY 3 | Webinar on the ninth-grade internships: How to spark interest in technology jobs with Schneider Electric and CEA. © UTOPIKPHOTO

# Smart Electronic for youth

**FEBRUARY 9** | Webinar on the Smart Electronique platform, a learning kit for jobs in electronics developed for the CFS Electronique, with CEA and Acsiel.

### **MARCH 2023**

# On our business attractiveness

MARCH 2 | Seminar on the attractiveness of the microelectronics industry. Forty representatives from Nanoelec's core partners met for an initial collective discussion on commitment, education and recruitment.

# **Photonic Sensors**

MARCH 8 | CEA-Leti & Nanoelec booth at international Optical Fiber Communication conference (OFC), USA.

© DR

# International Women's Day

MARCH 7 | In association with Y.Spot and CEA, Nanoelec conducted a round table: "How to attract innovative female talent?" Participants included high-ranking women managers from CEA, GEM, HP France, Lynred, UGA & Nanoelec. © P.JAYET/CEA

### Territorial issues of attractiveness for the microelectronics

**MARCH 17** | Webinar on the attractiveness of our region for the microelectronics industry, with Grenoble Alpes Métropole.

# Women in Engineering

MARCH 27 | Nanoelec exhibition Women in Technological Research was presented at the Laue-Langevin Institute from March 27 to April 14.

WELCOME TO THE SCIENCE BUILDING

### **APRIL 2023**

# Nanoelec ambassadors

**APRIL 18** | Nanoelec exhibition Women in Technological Research was presented at the La Casemate, the center for scientific culture in Grenoble, from April 18 to May 30, as part of the 50 Audacieuses event.

# 3D integration: design & architecture

**APRIL 19** | Annual workshop at the DATE international conference. Event-camera Dichotomy and the associated perspectives for Event-Graph Neural Networks.

# System Lab

**APRIL 26** | Colloquium on imagers, sports and health at CEA/Y.Spot (Grenoble).

# MAY 23

# Industry attractiveness

MAY 11 | Local forum on the attractiveness of the microelectronics industry organized by Minalogic and Nanoelec. © P. JAYET/CEA

# TSV for an imager

MAY 30 | Test vehicle for recent progress in high-density TSV for 3-Layers CMOS image sensors presented at ECTC/IEEE Conference.

### JUNE 23

# European Risc-V conference

JUNE 5 | Co-organization of European Risc-V conference (Barcelona). Intrinsically secure application processors and notably the CEA ScrambleCache demonstrator.

RISC-V

RISC-V Summit Europ

# Nanoelec Ambassadors at La Casemate

MAY 30 | Portraits of Nanoelec women ambassadors by students from Pablo Picasso Middle School (Echirolles) were presented at La Casemate, the center for scientific culture in Grenoble.

# Addvisia

**JUNE 6** | Webinar: Innovation Noon/CEA.

# Observatory of Women Engineers

JUNE 23 | On the occasion of International Women Engineers Day, webinar on the Observatory of Women Engineers.

# Leti Innovation Days

JUNE 27-29 | Three sessions of pitch forum for deeptech SMEs and startups.

### JULY 23

# Searching for talents

**JULY 6** | Preview of the film "Microelectronics in search of talent" produced by DDETS.

### **SEPTEMBER 23**

# Sido Lyon

**SEPTEMBER 20** | Partner with Minalogic at Sido Lyon; Addvisia demo on Captronic stand.

# NANO ELEC.

### OCTOBER 2023

# Addvisia at CCSTI La Casemate

**OCTOBER 2** | Presentation/ demonstration of Addvisia at CCSTI La Casemate, on the occasion of the National Science Festival.

# A view to a job in microelectronics

**OCTOBER 19** | Round table at the Grenoble Career Forum, by the Grenoble Alpes Métropole regional authority, with Lynred, Soitec, SET, CEA, and the National Education authority.

#### **NOVEMBER 2023**

# Irradiation

**NOVEMBER 8** | Partner of G-RADNExt (Carac program).

# A worldwide contest of hackers

**NOVEMBER 10** | Partner of CSAW (the world's most comprehensive student-run cybersecurity event).

# General Assembly

**NOVEMBER 14** | General Assembly of Nanoelec (no-public).

# Characterisation

**NOVEMBER 21** | co-organization of a national workshop with the Railenium and Saint Exupéry IRT and the IPVF, Supergrid Institute and Ines.2S ITE, on the occasion of the FIT annual press conference.

# Orientation Night

**NOVEMBER 24** | Orientation Night of the Grenoble Chamber of Commerce and Industry, with UGA, Aledia, CEA, Grenoble INP-UGA, Siemens EDA.

# Quantum Computing at the High-Level Forum

**NOVEMBER 26** | Partner of the High-Level Forum (non-public); participation in the round-table on quantum computing.

### DECEMBER 2023

# The Convention of Companies for Climate

**DECEMBER 5** | Webinar presenting the Convention of Companies for Climate, in the context of the microelectronics sector.

### **JANUARY 2024**

# Nanoelec at the Grenoble City Center

JANUARY 19 | Exhibition of the Nanoelec Ambassadors at the Grenoble Alpes Tourist Office.

# International Women's Day

#IWD2024 #InspireInclusion

### **FEBRUARY 2024**

# Tech&Fest

**FEBRUARY 1** | Poster Contest: Microelectronics for a better World with Schneider Electric, Aniah & Teledyne E2V.

#### **MARCH 2024**

# More women in the electronics industry

**MARCH 8** | Round-table on International Women's Day.

### **APRIL 2024**

# Nanoelec ambassadors at STMicroelectronics

FROM APRIL 2 TO MAY 24 | Nanoelec exhibition at STMicroelectronics Crolles and STMicroelectronics Grenoble.

MAY 2024

# 3-layer integration

MAY 27 | Wafer level Face-To-Back (F2B) 3D integration and operational 3-layer test vehicle presente at ECTC/IEEE Conference.

# From 3D integration to images

A view to a single chip with small form factor and enhanced electrical performance.

Progress in the semiconductor industry is divided into two classes: Moore's Law, where chips are manufactured with advanced technologies of 16 nanometers and smaller (this is the case for the processors at the heart of smartphones, tablets, PCs, and servers), and the More than Moore's approach, which uses mature manufacturing technologies of 20 nanometers and larger (this is the case for most components such as microcontrollers, power management circuits, sensors, power electronics, and radiofrequency circuits).

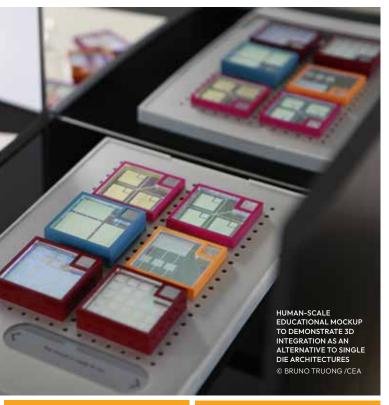

As the microelectronics industry continues to face challenges to further miniaturize components, according to Moore's Law, the More than Moore approach is also becoming more widespread. 3D integration technology has emerged in the last decade as a key process to combine multifunctional and technological integrated circuit devices to produce a single chip with small form factor and enhanced electrical performance.

1. Ayoub, B. (2023). Electrical and morphological characterizations of the hybrid bonding level down to submicron pitches. Bordeaux.

#### AN OVERALL APPROACH COMBINING TECHNOLOGY AND DESIGN

At CEA-Leti, through Nanoelec, we are building on 10 years of R&D on three-dimensional architectures, which now enables us to address very ambitious applications prospects. 3D integration, which consists in interconnecting electronic chips in three dimensions, is a promising solution for addressing the growing need for functionality, density and performance in future integrated circuits.

However, to allow the rapid emergence of this technology in industry, an overall approach is needed, taking account of technological development and the design of new circuit architectures, the development of design and testing tools, as well as reliability.

#### CHALLENGES IN HYBRID BONDING

From 2012 to 2020, the academic and industrial teams working under the Nanoelec/3D Integration program focused on developing a comprehensive platform compatible with the full design cycle of new products. They dealt with technology for wafer-to-wafer or die-to-wafer hybrid bonding, but also design, electronic design automation (EDA) tools, testing and reliability.

"The hybrid bonding technology, one of the various 3D stacking options, is suited to advanced device miniaturization with the possibility of reducing the hybrid bonding pitch below one micrometer", says Bassel Ayoub introducing his thesis report prepared at STMicroelectronics and CEA-Leti within Nanoelec<sup>(1)</sup>. He considered the impact of such aggressive interconnection pitch scaling on the thermomechanical stability, the electrical performance and the reliability of the hybrid bonding level applied to the domain of Smart Image Sensors. In particular he led Laue-microdiffraction studies with the unique synchrotron beam at the ESRF for Cu/SiO2 hybrid bonding integration. Highlighting a profound understanding of the interface robustness and reliability, he demonstrated -in the frame of Nanoelec- high reliable Cu/SiO2 hybrid bonding integration for pitch down to 0.8 µm as well as for hybrid bonding pad width reduced to 0.35µm, in the case of consumer application. New architectures allowing enhanced electrical performances with pitch reduction are now available. ♦

#### Smart imager

# Three-layer integration breakthrough for Al-embedded CMOS image sensors

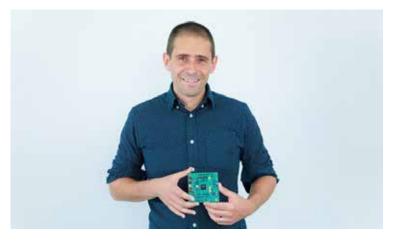

ERIC OLLIER PROJECT MANAGER AT CEA-LETI AND DIRECTOR OF NANOELEC/SMART IMAGER PROGRAM

© P.JAYET/CEA

In the frame of Nanoelec, CEA-Leti scientists reported a series of successes in three related projects that are key steps to enabling a new generation of CMOS image sensors (CIS) embedding AI from imaging to vision. The aim of IRT Nanoelec's Smart Imager program is to develop the technologies needed for the next generation of imagers, which will allow the transition from image generation to analysis of the information included in these images, on the very sensor itself, in order to perceive a scene, understand the situation and intervene on it. This transition represents a very real disruption and a paradigm shift, with computing and memory issues becoming preponderant, in addition to image generation. This revolution implies the use of artificial intelligence on the image sensor itself.

The consortium's goal is to develop 3D stacking technologies in order to implement artificial intelligence functions on the sensor itself. This is why we are working both on the components and on the software, to transition our image sensor concepts from image generation to data generation, enabling a situation to be analyzed.

In 2023, work continued on the development of key technological building blocks: hybrid bonding, high density TSV (HD-TSV), heterogeneous integration and specific technologies for infrared applications. The main result is the very first demontration of the 3-layer stacking integration at CEA-Leti, through a functional test vehicle combining hybrid bonding in face-to-face & face-toback configurations and HD-TSV, with functionality being verified via morphological and electrical characterizations. In addition, innovative architectures have been proposed for future visible & eventbased smart image sensors.

Our program is very close to two other activities at Nanoelec: the System Lab initiative, searching for new multispectrum imaging applications, and Displed. We work on simulation & design tools for hybrid bonding components and technologies for 3D architectures. TEST CHIPS ARE PREPARED FOR TRANSFERT © A.HAVRET/CEA

### SMART IMAGER PROGRAM AT A GLANCE

#### → VISION

The transition from imagers to vision sensors is generating new market opportunities

#### → AMBITION

To provide key hardware and software building blocks, to validate them through demonstrations ranging from test vehicles and proofs of concept to the prototyping of a smart, multi-layer imager

#### → MISSION

Stacking/3D technologies, embedded AI and data management, New architectures

#### → PARTNERS

CEA Grenoble INP-UGA Lynred Prophesee Siemens EDA STMicroelectronics

AGENDA

#### STMICROELECTRONICS

# New products being manufactured

Four new products designed in 2023 and based on 3D stacking technologies could rapidly be appearing on the image sensors market.

"The benefits of the approach developed by the teams involved in Nanoelec are still reduction in chip size, performance and consumption gains", says Eric Mazaleyrat, Technology watch and innovation director at STMicroelectronics. ◊

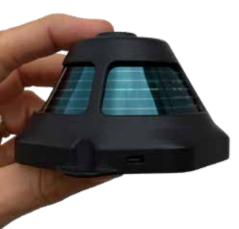

# A frugal neuromorphic sensor for the loT

PROPHESEE

(()())

The industrial version of the GenX320 product was officially launched in October 2023. "This is our fifth generation sensor", says Luca Verre, co-founder of Prophesee. "It is both highly efficient in terms of energy consumption and the smallest neuromorphic sensor<sup>(1)</sup> in the world." This sensor is being used in AR/VR, for example in ultra high-speed, low energy eye tracking or hand tracking applications for headsets. "With this new product, which features some of the work led with our partners from the Nanoelec/Smart Imager program, Prophesee intends to expand its market to more mass consumer markets such as IoT after having already demonstrated significant traction in the industrial automation market", explains Luca Verre.

GENX320, which already received 4 Award, including at CES 2024, "opens the door to integration of this technology into connected devices, whether or not portable, used in low-light environments and incorporates artificial intelligence algorithms", notes the specialist site L'Embarqué. ◊

Above, to the left TRINAMIX, VISIONOX AND STMICROELECTRONICS PRESENT COST-EFFICIENT, SECURE FACE AUTHENTICATION SYSTEM FOR BEHIND-OLED INTEGRATION IN SMARTPHONES © STMICROELECTRONICS

#### Above, to the right A NEW GENERATION OF EVENT-BASED SENSOR FEATUREING SOME OF THE WORK LED IN THE FRAME OF NANOELEC/ SMART IMAGER PROGRAM © PROPHESEE

Event-based sensors, also known as neuromorphic vision sensors, consist of asynchronous pixels which react to changes in brightness with a far higher temporal dynamic than conventional imagers.

#### **ARCHITECTURE & APPLICATIONS**

# Lightweight event stream classification

81% REDUCTION IN THE NUMBER OF CALCULATION OPERATIONS PER SECOND COMPARED TO THE STATE-OF-THE-ART.

Event camera pixels efficiently encode visual information through triggered events, offering advantages in temporal resolution, dynamic range, and data sparsity. In 2023, several results produced within the framework of Nanoelec supported Prophesee's core technology, while the company received an award for its 5th generation sensor at CES 2024. "However, the optimal machine learning method for leveraging these characteristics remains unclear", said Thomas Mesquida, as first author of a study bringing together scientists from CEA and

Prophesee presented at the 34<sup>th</sup> British Machine Vision Conference<sup>(2)</sup>. *"Existing approaches often convert events into 2D frames, losing crucial time-domain information"*, adds Thomas.

A promising alternative is eventgraph neural networks. However, they suffer from computational intensity and limited temporal dependencies. As a solution, the study proposes combining the recent method of the HUGNet lightweight event-graph neural network with gated recurrent units to model temporal dependencies

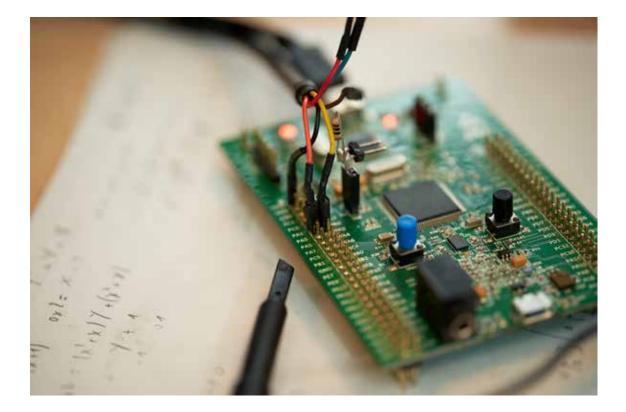

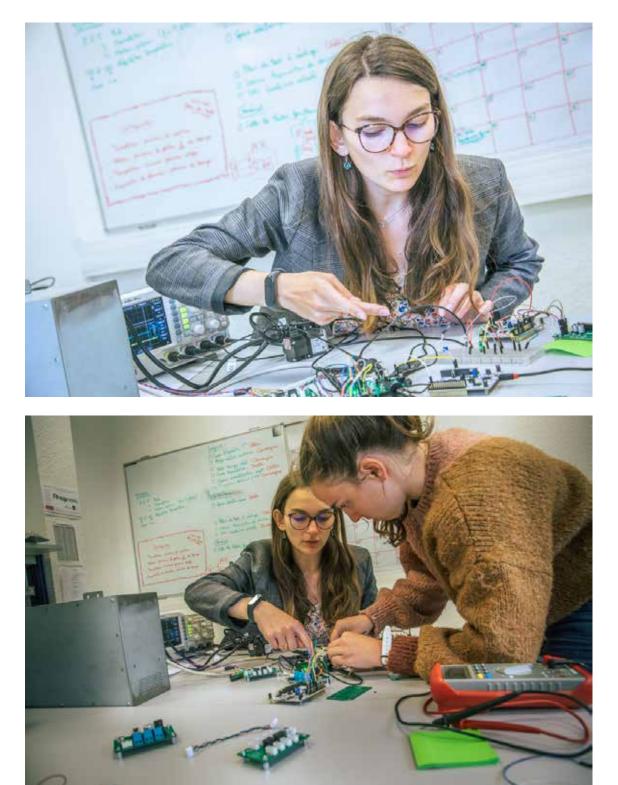

Below and next page, THOMAS MESQUIDA & SÉBASTIEN THURIES, ENGINEERS AT CEA-LIST, DURING A CREATIVE SESSION FOR OPTIMIZATION OF THE 3 LAYERS ARCHITECTURE FOR THE SMART IMAGER © O.DEVISE/CEA 2024

#### 2. Mesquida, T.,

Dampfhoffer, M, Dalgaty, T., Vivet, P., Sironi, A., & Posch, C. (s. d.). G2N2: Lightweight Event Stream Classification with GRU Graph Neural Networks. BMCV, Aberdeen, UK A new event-data augmentation technique that boosts the performance of both event-graph and convolutional neural networks.

3. Dalgaty, T., Mesquida, T., Joubert, D., Sironi, A., Vivet, P., & Posch, C. (2023). HUGNet : Hemi-Spherical Update Graph Neural Network applied to low-latency event-based optical flow. 2023 IEE/CVF Conference on Computer Vision and Pattern Recognition Workshops (CVPRW), 3953-3962. https://doi.org/10.1109/ CVPRW59228.2023.00411

4. The GRU (Gated Recurrent Units) are parts of neural networks. The first part of the network (the backbone) extracts and analyses information, while the end of the network (the task head) creates a dedicated application using the extracted data.

5. Dalgaty, T., Mesquida, T., Joubert, D., Sironi, A., Soubeyrat, C., Vivet, P., & Posch, C. (2023). The CNN vs. SNN Eventcamera Dichotomy and Perspectives For Event-Graph Neural Networks. 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE)

between the features extracted by HUGNet. "Relative to the previous state-of-the-art in event-graphs, we reduce event-graph update latency by more than four orders of magnitude and reduce the number of neural network calculations per second by 70× while predicting optical flow more accurately<sup>(4)</sup>. In some cases, we also find that, relative to convolutional models, the number of operations per second was reduced by 81%", says Christoph Posch, Co-Founder and CTO at Prophesee.

Furthermore, the team introduced a new event-data augmentation technique that boosts the performance of both event-graph and convolutional neural networks on this task by up to 7.4%. "Future work will focus on exploring alternatives to GRU task heads<sup>(3)</sup> to achieve lightweight and ultra-low latency implementation without relying on frame buffering", Thomas says.

At the DATE Conference 2023 in Antwerp (BE), the same team discussed the CNN vs. SNN Event-camera Dichotomy and the associated perspectives for Event-Graph Neural Networks<sup>(5)</sup> to again enhance performance and frequency response and reduce energy consumption. *"The latter is of particular importance since these algorithms will typically be employed near or inside the sensor at the edge where the power supply may be heavily constrained"*, points out Christoph Posch. ♦

#### **ARCHITECTURE & DESIGN**

# Efficient in-sensor processing based on advanced 3D technologies

A CEA-LIST TEAM INVOLVED IN THE NANOELEC/SMART IMAGER PROGRAM MAKES A YEARLY CONTRIBUTION TO THE ORGANIZATION AND CONTENT OF AN INTERNATIONAL WORKSHOP ON THE CHALLENGES OF HETEROGENEOUS 3D ARCHITECTURES AND SENSORS, AT THE DATE CONFERENCE.

"The 2023 edition attracted close to 50 experts in Antwerp (BE). AI, Quantum Computing as well as the Risc-V open standard instruction set architecture were discussed", says Pascal Vivet (CEA-List), as first member of the workshop organizing committee, and contributor to the Nanoelec/Smart Imager program.

"3D integration is THE technology for highly integrated image sensors", Sébastien Thuries (CEA-List), who also works at the Nanoelec/Smart Imager program, stated at the workshop. During the presentation at DATE, he pointed out two breakthroughs thanks to 3D heterogeneous integration: "First, we can stack the backside Imager; secondly, we can combine a 3-layer imager with a CNN near sensor and an event-based sensor", he explains.

The 2024 edition of the DATE workshop focused on heterogeneous integration which *"enables larger system level integration and improves PPAC figure of merit "*, as pointed by Tony Mastroianni, Advanced Packaging Solutions Director at Siemens Digital Industries Software, in his talk.

Starting from the design & verification challenges of the Active Interposer 96-core Architecture developed by CEA within Nanoelec, Tony Mastroianni detailed a System Technology Co-Optimization strategy. "3D IC ecosystem requires open standards and formats, support for multi-domain design, as well as marketplace including a rich library of reusable chiplet components and broad industry & government adoption", he concludes. ◊

#### TARGETING NEW MARKETS

# Infrared opting for 300mm

3D STACKING TECHNOLOGIES COMBINED WITH THE POSSIBILITY OF FABRICATION ON 300MM SILICON WAFERS ENABLES THE INFRARED IMAGING MARKETS TO BE EXPANDED, FOR EXAMPLE TO PEDESTRIAN DETECTION FOR THE AUTOMOTIVE INDUSTRY.

Infrared represents a broad technological spectrum and numerous applications in highly diverse industrial sectors, from space imaging to thermography, to defense and autonomous vehicles. As a specialist in this field, Lynred is involved in two Nanoelec programs. *"With Smart Imager, we are addressing major* technological challenges for the medium/long term: we envisage that 3D stacking technology and the associated architectures will appear in our products by the 2030-2035 timeframe."

For that purpose, Nanoelec/ Smart Imager will first investigate different technological options for infrared to access 300mm CMOS nodes, explains Sébastien Cortial, Senior Expert at Lynred. *"In addition, the Nanoelec/System*  Lab initiative enables us to continue the process with research opening up new applications possibilities, which these technological advances are making possible."

"A number of Nanoelec/Smart Imager program results in 2023 are contributing to strengthening our roadmap", explains Xavier Brenière, head of the application laboratory at Lynred. ◊

### With hybrid bonding (HB) pitch reduction, many challenges are arising.

SILICON TECHNOLOGICAL DEVELOPMENTS

# Hybrid bonding pitch reduction

IN ADDITION OF BASSEL AYOUB'S PHD, A TEAM FROM STMICROELECTRONICS AND CEA-LETI GATHERED IN NANOELEC/ SMART IMAGER PROGRAM, PUBLISHED NOT LESS THAN SEVEN PAPERS IN 2023 ON RELIABILITY OF THE CU/SIO<sub>2</sub> HYBRID BONDING INTERFACE.

With hybrid bonding (HB) pitch reduction, many challenges are arising. One of them is related to the reliability of HB-based interconnects and in particular the thermomechanical stability of the Cu/SiO, hybrid bonding interface and its electromigration performances as electromigration (EM)-related degradation is intimately linked to the electrical current in addition to temperature and mechanical stresses. During 2023, at four IEEE International Conferences<sup>(6)</sup>. Sandrine Lhostis (STMicroelectronics) and Stéphane Moreau (CEA-Leti) together with scientist from IMS Laboratory (University of Bordeaux), reported recent advances on gualification and reliability of Cu/SiO, to Cu/

SiO<sub>2</sub> hybrid bonds for 3D ICs. "High robustness is validated to all the standard reliability tests within the specifications for consumer applications for bonding pitch down to 0.81 µm. Compared to standard BEoL interconnects, few differences are observed: modification of the TTF dependency behaviour at low electrical field, and new failure mode in electromigration for small bonding pads width" says Sandrine Lhostis, engineer at STMicroelectronics.

"For EM-related failures in HB-based interconnects when decreasing the interconnect pitch from 6.84 down to 1.44μm, the weakest link moves from the BEOL levels to hybrid bonding

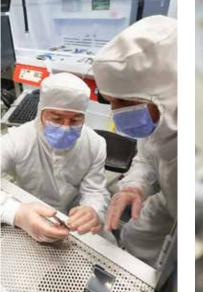

Photos of the double page,

IN THE CEA-LETI CLEAN ROOM, PIERRE MONTMEAT ET MÉLANIE VACON, ENGINEERS AT CEA, BEING ABOUT TO START AN HYBRID BOUNDING PROCESS ON EVG TOOL © A.HAVRET/CEA 2024

International Interconnect Technology Conference (IITC), the Reliability Physics Symposium (IRPS), European Symposium on Reliability of Electron Devices, Failure Physics and Analysis (ESREF) and Electronics Packaging Technology Conference (EPTC).

ones, without affecting the projected performance under use conditions. Additional studies done on design aspects do not evidence any negative impact on the electromigration resistance of the HB brick", explains Stéphane Moreau, research engineer at CEA-Leti.

"As pitch reduction tends to submicronic size pads, their microstructure moves from a polycrystalline one to a monocrystalline one", underlines Bassel Ayoub, co-author of the four communications, now engineer at STMicroelectronics. As a teaser for future studies, their talks at IRPS and IITC-MAM pointed out few hot questions that "have to be investigated in a near future as dimension shrinkage", like : "is there any new failure mechanisms, especially EM-related below 1 µm pitch? Is there any additional effects stress for die-to-wafer integration"? ◊

We reached 100% connection yield through hybrid bonding and TSV.

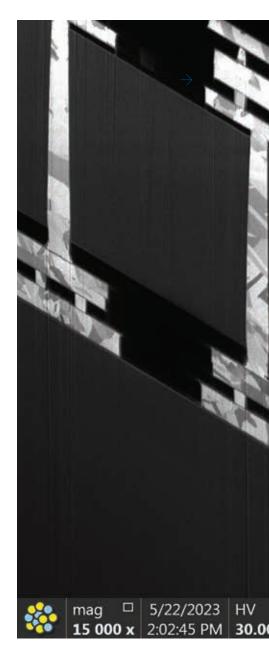

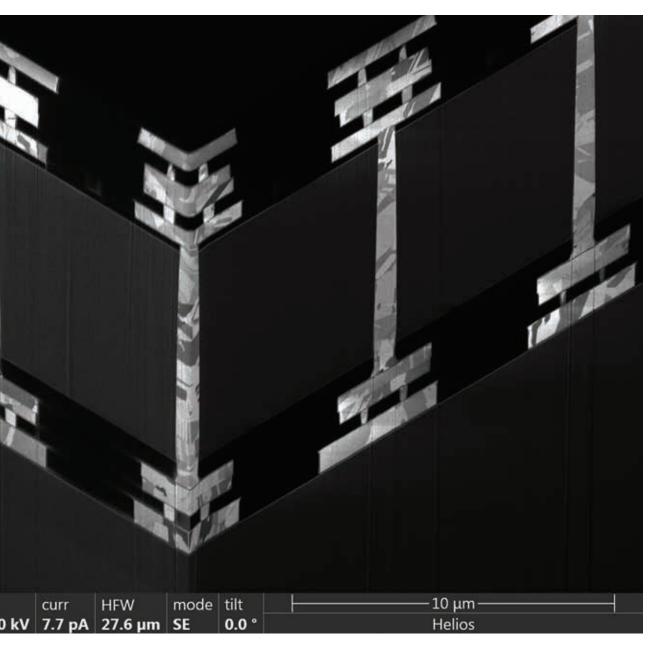

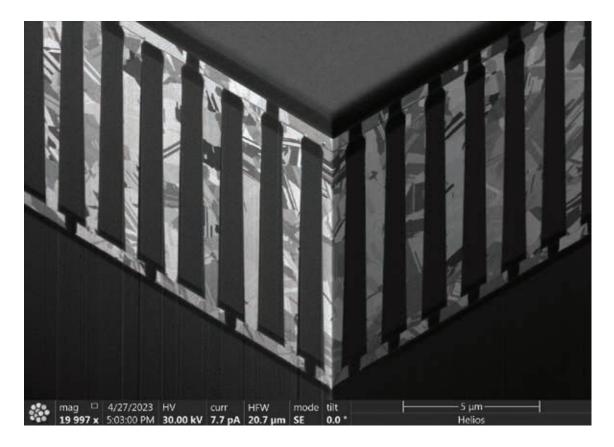

On the right, AT THE IEEE 74TH ELECTRONIC COMPONENTS AND TECHNOLOGY CONFERENCE (ECTC 2024, DENVER, COLORADO, MAY 28 - 31, 2024), CEA-LETI DEMONSTRATES FEASIBILITY OF COMBINING HYBRID BONDING AND HIGH-DENSITY THROUGH-SILICON VIAS, THESE DEVELOPMENT ARE CONDUCTED TO MEET THE NEEDS OF THE NANOELEC/SMART IMAGE PROGRAM. FIB-SEM 3D CROSS-SECTION OF THE 3L TV STRUCTURE: THE PITCH IS 68M FOR THE BONDING PADS; AND THE HD TSVS DIMENSIONS ARE 1X108M © CEA

7. "Low Resistance and High Isolation HD TSV for 3-Layer CMOS Image Sensors", S. Borel & al., ECTC 2024 TO BE PUBLISHED

#### **TEST CHIPS & PERFORMANCE ASSESSMENT**

# Achieving 3-layer stacking integration for future smart imagers

FOR THE NEEDS OF THE NANOELEC/SMART IMAGER PROGRAM, A CEA-LETI TEAM DEMONSTRATES WAFER LEVEL FACE-TO-BACK (F2B) 3D INTEGRATION. YEAR ON YEAR, THEY IMPROVE THEIR PERFORMANCE IN COMBINING FINE PITCH CU-CU HYBRID BONDING WITH HIGH-DENSITY CONNECTORS UP TO AN OPERATIONAL 3-LAYER TEST VEHICLE.

3D stacks offer multiple advantages for advanced components such as smart imagers and their assembly in a wafer-to-wafer (W2W) approach opens up access to very fine pitch interconnections. While hybrid bonding is commonly used to connect the layers, high-density (HD) TSV are mandatory for the signals to be transmitted through them.

For several years now, a CEA-Leti team has focused on the key enabling technology of TSV for the 3-Layer CMOS image sensors under development at Nanoelec, and every year publish several papers to report on their progress at the international ECTC conference.

"HD TSV technology was transposed from a stack with a 9 µm-thick substrate to a thinner stack with only 5 µm of silicon", reports Stephan Borel<sup>(7)</sup>. The improvement of the thinning process by using a more recent and more efficient grinding tool reduced the TTV (Total Thickness Variation) around 1 µm. "We reached 100% connection yield through hybrid bonding and TSV. At the same time, we optimized the TSV by upgrading the materials and processes for even higher performance", he adds.

AGENDA

AGENDA

Below, CROSS-SECTIONAL SEM MICROGRAPHS OF HD TSV IN A DENSE ENVIRONMENT. HD TSV DIMENSIONS ARE 1µm IN DIAMETER AND 10µm IN

# © CEA

On the right, AT CEA-LETI CLEANROOM, THE MACHINE USE FOR CMP PLANARIZATION © AUBERT/CEA

8. "Backside Thinning Process Development for High-Density TSV in a 3-Layer Integration", R. Bouis & al. ECTC 2024 TO BE PUBLISHED

9. 3-layer Fine Pitch Cu-Cu Hybrid Bonding Demonstrator With High Density TSV For Advanced CMOS Image Sensor Applications, S. Nicolas & al., R. Bouis & al. ECTC 2024 T0 BE PUBLISHED The HD TSV technology roadmap entails lower silicon thickness to improve performance. Focusing on the backside thinning flow (grinding, CMP, metrology) for TSV depths of 6µm or less, the same team implemented stringent process control from grinding to CMP finishing, to obtain remarkably low silicon total thickness variations below 1µm. "Our work opens up prospects for lesser silicon thicknesses (<5µm) and paves the way for industrial implementation", says Renan Bouis<sup>(8)</sup>.

By means of gradual progress, the team presented a 2-Layer Face-To-Back (F2B) test vehicle (TV) at the ECTC 2023 Conference that they had already demonstrated the previous year. "And now, we unveil the next level of integration by achieving a 3-layer TV with fine-pitch Cu-Cu hybrid bonding (HB) technology and

high density (HD)", says Stéphane Nicolas<sup>(9)</sup> at the ECTC 2024 edition. Their most recent TV has hybrid bonding pad dimensions of  $3\mu$ m and  $2 \mu$ m along with standard pitch (6  $\mu$ m) and fine pitch (4 $\mu$ m) respectively.

HD TSV dimensions are 1µm in diameter and 10µm in height.

"Our next step will be to implement this 3D technology in a functional advanced CMOS image sensor", adds Stéphane. ◊

#### **DESIGN TOOLS**

# An imager built on a disruptive 3-layer architecture

ONE OF THE MAIN CHALLENGES OF THE NANOELEC/SMART IMAGER PROGRAM IS TO EMBED THE POWER OF AN AI ALGORITHM DIRECTLY UNDER AN IMAGE SENSOR IN A CONSTRAINED, LOWPOWER ENVIRONMENT.

The Nanoelec/Smart imager sensor architecture has been defined this year: it includes a layer of imagesensitive pixels, a layer combining analog reading of the image and pre-processing of the digitized pixels, and a third layer dedicated to the hardware and software deployment of artificial intelligence (AI) functions.

To speed up the design, simulations and functional verification of the Al layer and the entire architecture, Siemens EDA teams have implemented four of their software tools: Catapult, Questa, Symphony and Tessent.

In a communication at the Chiplet Summit (January 2023, USA), scientists from Siemens EDA and CEA-Leti presented a warpage simulation methodology for assessing chip-package interaction in chiplet-based 3D stacks<sup>(10)</sup>. "Combining simulations with layout analysis capabilities allows obtaining Chip-Package Interaction stresses with any desired resolution, by applying multi-scale simulation technique. The study demonstrates that, for the purpose of mechanical failure analysis in the early stage of a package design, the warpage measurements can be used for the tool's calibration", summarizes Jun-Ho Choy, engineer at Siemens EDA in Fremont (CA, USA) as the first author of the study rolled out for the needs of Nanoelec.

Data from simulations from a recently proposed methodology for electromigration (EM) assessment in an on-chip power/ground grid of integrated circuits were compared with physical measurements on dedicated test grids, through Nanoelec<sup>(11)</sup>. "We set two different test vehicles on electrical and temperature characterization protocols. The existing current distributions resulted in different behavior of electromigrationinduced failures in these nets: a gradual voltage evolution in the power net, and sharp changes in the ground net were observed in the experiment, and successfully reproduced in simulations", reports Armen Kteyan, engineer at Siemens EDA in Yerevan (Armenia). ◊

10. Choy, J.-H., Sukharev, V., Kteyan, A., Moreau, S., & Brunet-Manquat, C. (2023, January 24). Warpage simulation methodology for assessing chip-package interaction in chipletbased 3D stacks. Chiplet Summit, San Jose, California. US

11. Kteyan, A., Sukharev, V., Volkov, A., Choy, J. H., Najm, F. N., Yi, Y. H., Kim, C. H., & Moreau, S. (2023). Electromigration Assessment in Power Grids with Account of Redundancy and Non-Uniform Temperature Distribution. Proceedings of the 2023 International Symposium on Physical Design, 124-132.

#### **DESIGN TOOLS**

# Bridging the gap between neural network exploration and hardware implementation

AT THE  $60^{TH}$  DESIGN AUTOMATION CONFERENCE (DAC 2023), A TEAM FROM SIEMENS EDA AND CEA-LIST UNDERLINED THE ISSUES OF THE HARDWARE DESIGN CYCLE IN THE FAST GROWING RESEARCH TOPIC OF AI DEEP LEARNING<sup>(12)</sup>.

"Hardware designers struggle to master all algorithmic optimizations", points out Nermine Ali, research engineer in embedded Al at CEA-List, as contributor to the Nanoelec/Smart Imager program. "We have to cope with the increasing complexity of the design cycle and multiplying constraints like real-time constraints, memory and power constraints, etc.", she adds. The team proposed a new N2D2 Catapult-Stream export that has the potential to become a leading high level synthesis generator for large CNN networks. *"Fully automatic generation is ongoing, for full compatibility of C++ export with Catapult",* underlines Ronan Poirier, Application Engineer at Siemens EDA, also involved in the program. ◊

Below, RONAN POIRIER (SIEMENS EDA) & NERMINE ALI (CEA-LIST) PRESENTING THEIR COLLABORATION AT NANOELEC GENERAL ASSEMBLY 2023 © P.JAYET/CEA 2023

12. Ali, N., Szczepanski, M., Pajaniradja, S., & Vivet, P. (2023, June 9). Bridging The Gap Between Neural Network Exploration And Hardware Implementation with N2D2 & HLS. 60<sup>th</sup> Design Automation Conference (DAC 2023), San Francisco, USA.

$\checkmark$

ONE OF THE EIGHT POSTERS ON THE TOPIC **"LA MICROELECTRONIQUE POUR VIVRE** DANS UN MONDE MEILLEUR" (MICROELECTRONICS FOR LIVING IN A BETTER WORLD) CREATED BY THE STUDENTS OF THE BRASSART-GRENOBLE SCHOOL FOR TECH&FEST 2024. POSTER BY AMBRE FENIX, "GRAPHIC CREATION" STUDENT © BRASSART

#### Displed

# Towards a renewal of display technology in Europe

#### **FRANÇOIS TEMPLIER**

PROGRAM MANAGER FOR DISPLAYS AT CEA AND DIRECTOR OF THE NANOELEC/ DISPLED PROGRAM

© P.JAYET/CEA

MicroLED technology is bringing about a revolution in the field of displays, by providing outstanding image quality and immersion capability, for display sizes ranging from smartphones to large TVs.

The IRT Nanoelec Displed project is based on the Smart-Pixel concept, a patented key enabling technology that paves the way for the manufacture of new display concepts in Europe. The first goal of the project is to develop the Smart-Pixel concept through proof-of-concept demonstrations and the second is to develop new concepts for display features (light field multiviews, sensor display, flexible display...). In 2023, we obtained the very first results from our pilot initiative on life cycle analysis as applied to the early R&D phase on Smart-Pixel. We achieved the very first full-integration 3D-LED Smart-Pixel technology, as well as the first RGB (Green-Red-Blue) pixel proof-of-concept in three colors.

A new-generation 2D-LED Smart-Pixel demonstrator has been delivered. It consists of a PCB with a matrix of 8x8 smart pixels, that is fully operational. EVGroup and SET provided new tools for advanced hybrid bonding. Aledia has completed the construction of its production site and the pilot line will be fully equipped in 2024. FRÉDERIC BERGER (CEA-LETI) IS SETTING THE SET MACHINE FOR TESTING A NEW KIND OF TOOL FOR THE MASS TRANSFERT OF MICROLED FOR NANOELE/DISPLED PROGRAM © A.HAVRET/CEA 2024

#### **DISPLED PROGRAM AT A GLANCE**

#### → VISION

A unique opportunity for a French & European ecosystem on large display technologies for immersive applications

#### → AMBITION

To design and demonstrate key microLED technologies for high-end, immersive displays

#### → MISSION

To develop process flows for microLED, Smart-Pixel fabrication and mass transfer onto the display

### → PARTNERS

Aledia CEA EVGroup SET

#### SUSTAINABILITY

# Smart-pixel life cycle analysis

LOOKING FOR THE KEY PARAMETERS TO OPTIMIZE THE ENVIRONMENTAL FOOTPRINT OF THE SMART-PIXEL PROCESS FLOW.

Environmental impacts must be taken into account when developing any new technology. This applies to the display industry design work carried out in the Nanoelec/Displed program.

In 2022 and 2023, a Life Cycle Assessment (LCA) of the Smart-Pixel was conducted on R&D work (for the very first time in the World), as well as the study of a tool dedicated to identifying the key parameters of the environmental footprint of the associated process flow. "The overall objective of this study is to assess the environmental impacts of this kind of display manufacturing, considering not only climate change but also all the sixteen environmental impacts recommended by the Product Environmental Footprint method (PEF). Hence, the aim of this study is to propose a methodology based on LCA for the first time", explains

1. Holo, Antonin, Dubarry, C., Lopes, J.-C., Dupont, M., Chabaud, S., & Templier, F. (12-17 may). MicroLED Display Life Cycle Assessment. Display Week, San Jose, USA.

Nouha Gazbourg "Systemic integration of Eco-design in photovoltaic technologies R&D", PhD Report UGA on a doctoral thesis prepared at CEA-Liten, Feb. 2019.

3. Templier, F. (2023, August 16). Integration technologies for hybridizing GaN microleds and CMOS circuits. K-Display 2023 Conference & Exhibition, Seoul, Korea Antonin Holo, LCA engineer at CEA-Leti, which carried out the study.

An initial set of results has been obtained, for all sixteen environmental impact categories of the PEF 3.0 method recommended by the European Commission.

"For example, the contribution of the epitaxy step could be seen with regard to every environmental impact. Etching, deposition and stripping process-family contributions were also underlined, given their large contribution to each of the selected environmental impacts", Antonin Holo reports<sup>(1)</sup>. He presented the study at the Display Week, in San Jose (US), on May 2023.

Since there are no databases for microelectronics at the component scale, or the literature is outdated and does not reflect current trends, this LCA will provide new and previously unseen results. These new LCA results are used on an in-house eco-design tool, allowing comparison of new technologies with reference technology. It relies on a similar tool designed by CEA-Liten for photovoltaic R&D<sup>(2)</sup>. The fabrication flow parameters can be easily altered in order to obtain an overview of how this changes the sixteen environmental impacts addressed.

Among other results of interest is demonstration of the impact of the type of electricity (carbonated vs. nuclear) on CO<sub>2</sub> generation for Smart-Pixel fabrication. *"In fact, the* biggest factor impacting our carbon footprint in this process is the contribution of CMOS. If we source it from Asia, the impact on the climate is high; if we buy it from a country with a low-carbon energy mix, the balance is more favorable", explains Sandrine Chabaud, Safety and Environment Manager at Aledia. ◊

#### **TECHNOLOGY STATE OF THE ART**

# Hybridizing GaN microleds and CMOS circuits

REVIEWING HYBRID BONDING POSSIBILITIES FOR HETEROGENEOUS INTEGRATION.

At the K-Display Conference in Seoul, Korea, François Templier reviewed the challenges for the factoring of MicroLED arrays driven by CMOS circuits<sup>(3)</sup>: *"Such devices are needed for GaN microdisplays and large area displays"*, he underlines. Several technologies may be used to hybridize the two parts, and Smart-Pixel should be the one to enhance throughput. "It is promising for mass production for displays as demonstrated with recent results in hybrid bonding by the Nanoelec/Displed program", suggests François. ◊

#### A STEP AHEAD

# The move to flexible displays

#### FIRST RESULTS FOR THE TRANSFER OF MULTIPLE DIES ON NON-RIGID SUBSTRATES.

As part of the Nanoelec/Displed program, CEA-Leti and Aledia teams are investigating how to open up the application of MicroLED Smart-Pixels to flexible displays, or to new functionality based on the addition of sensors, or to multiview displays.

Thus in 2023, design and development of a Smart-Pixel flexible display started at Nanoelec.

"An important step towards the flexible demo is to evaluate how multiple, very small dies (<500µm) can be transferred with high accuracy onto foldable or rollable plastic substrates", explains Aurélie Beaumont, leading the study at CEA- Leti, together with Hugues Lebrun, Display Engineering at Aledia. "Our test vehicle showed how flexible and conformable displays of various dimensions (from a few cm<sup>2</sup> to a full 200mm surface) can be fabricated and successfully populated with multiple Si bare dies – coarse pitch in this case".

15 flex wafers were produced and the fabrication of a fine-pitch test chip was run in parallel *"in order to define the best configurations regarding die assembly"*, Aurélie Beaumont adds. The next step is now to develop the assembly of the flexible substrates with the finepitch test chip, and then with the functional Smart-Pixel Chips. Today's flexible or foldable displays use TFT (thin-film transistor) driving devices (active matrix backplanes) with thin-film OLED emitters, which are themselves flexible. Both TFTs and OLEDs are suffuring mechanical stress during folding. MicroLED Smart-Pixels make it possible to get around the difficulty of making the whole technology flexible. "In our case, only the support circuit, which is totally passive (no transistors), is flexible due to the pixelation of the microLEDs", underlines Hugues Lebrun. "The flexibility is then only limited by the surface occupied by the LED in the pixel area." **◊**

Below, CHIP TEST ON FLEXIBLE SUBSTRATE (WITH TOP POLYMER) © DR Abdenacer Aitmani, engineer at CEA-Leti, receiving a firt set of tools for mass transfert of dies, for a new concept of displays including microleds on smart pixels.

© A.HAVRET/CEA

LIOK JO LIF #75 240×40

1

#### MANUFACTURING TOOLS FOR HETEROGENEOUS INTEGRATION

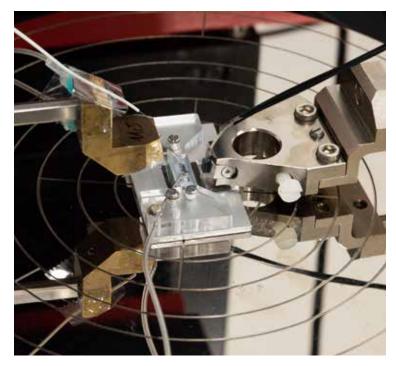

## Picking and placing dies on a substrate

#### NEW MACHINES WILL ACCELERATE THE DEPLOYMENT OF A MASS PRODUCTION LINE OF DISPLAYS.

"In the previous phase of the Displed program, we already demonstrated the use of dedicated micro-tools mounted on our flipchip bonder machine to pick up small dies individually and several of them collectively", says Pascal Metzger, CEO of SET. This year, SET and CEA teams did the same successfully but with much smaller dies, picking them up individually and placing them on a substrate. SET is also investigating the possibility of flipping the dies. "To meet the accurate placement requirement set in the Nanoelec/ Displed program, we have decided to completely redesign the motorization chain including motors, guidance systems and encoders to improve the precision of the movements of our robot", adds Pascal Metzger.

#### Below,

ASSEMBLY ROOM AT SET, A CORE PARTNER OF NANOELEC. SET IS A FRENCH TOOL SUPPLIER FOR ELECTRONICS VALUE CHAIN, SPECIALIZED IN FLIP-CHIP BONDING, A PROCESS TO ASSEMBLE TWO COMPONENTS TOGETHER, MECHANICALLY AND ELECTRICALLY.

© SE

With regard to the mass transfer of microLEDs, SET is working with the other Nanoelec/Displed partners on the feasibility of a concept, which is a prerequisite for an industrial machine that will be essential for the deployment of a screen production line in France and Europe. "With the Nanoelec ecosystem, we feel we have a good lead in the field of direct bonding, particularly in terms of assembly precision and yield", Pascal Metzger adds. ◊

Side right, SET EQUIPMENTS UNDER TESTING IN CEA-LETI CLEANROOM © A.HAVRET/CEA

Beyond the Nanoelec/Displed program, SET teams are also taking part in transverse actions set by Nanoelec to boost the attractiveness of the electronics business. *"As a supplier for the development of the microelectronics and digital industry, we have to find ways to attract, hire and keep top-skilled collaborators, even if we are a small company based in the heart of the Alps"*, Pascal Metzger says. He is in the center of the above picture, as one of the guest speakers at the Territorial forum on the attractiveness of the electronics industry, May 11, 2023 in Grenoble, with Stéphane Berthier, Head of HR Dev at ST Microelectronics – Business Coach (left) and Jean-Philippe Gene, Director for Business & Equity at Linksium (right).

#### **INDUSTRIAL RAMP-UP**

## New tool for advanced hybrid bonding

WITHIN THE FRAMEWORK OF IRT NANOELEC, EV GROUP DELIVERED A DIE DIE-TO-WAFER SELF-ASSEMBLY EQUIPMENT TO CEA-LETI'S CLEAN ROOM.

This innovative technique enables high throughput collective die-towafer bonding with high accuracy alignment.

Access to state-of-the-art samples through a program like Nanoelec/ Displed is crucial for developing and advancing this technology. EVG bridges the gap between CEA-Leti's cutting-edge process development and the industry. Initial results pave the way for high-volume manufacturing, and the ability to reach new markets is growing as die-to-wafer bonding gains traction in heterogeneous and hybrid integration. "In addition, we completed a new manufacturing building in 2023. This facility is the latest in a series of expansion phases and investments driven by continued strong demand for EVG's hybrid bonding and other process solutions and process development services to support the rapidly growing advanced packaging and 3D/heterogeneous integration market" emphasizes Markus Wimplinger, Corporate Technology Development & IP Director of EV Group. ◊

PIERRE MONTMEAT AND MÉLANIE VACON, CEA-LETI ENGINEERS, PREPARING A 3D CHIP BONDING FOR NANOELEC ON EVG 8100 A LOW TEMPERATURE PLASMA ACTIVATION SYSTEM © A.HAVRET/CEA 2024

Photo.

Below,

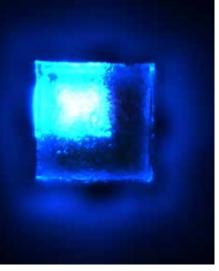

DEMONSTRATION OF A FULL-COLOR UNIT BY ALEDIA: BLUE EMISSION COMES FROM THE NANOWIRES AND GREEN AND RED EMISSION BASED ON QD CONVERSION @ AI FDIA

**4.** For high resolution displays with small pixel pitch

#### SMART-PIXEL DEMONSTRATORS

### **RGB pixels work**

WHILE ALEDIA COMPLETES THE CONSTRUCTION OF ITS FUTURE FACILITY, TECHNICAL RESULTS ENABLE THE DESIGN OF THE PRODUCTION FLOW TO CONTINUE FOR THE DISPLED PROGRAM.

"3D-LED Smart-Pixel development<sup>(4)</sup> has reached an important step this year with successful Smart-Pixel process integration, involving two metal levels, hybrid bonding and backside grinding", says Muriel Dupont, R&D partnership manager at Aledia.

For the demonstration of fullcolor units, the test vehicle implemented by Aledia teams showed blue emission coming from the nanowires and green and red emission based on QD conversion. "This is the first proof-of-concept of RGB Smart-Pixel in three colors", highlighted Muriel. At the same time, a demonstrator including a matrix of a new generation of 2D-LED Smart-Pixels on a PCB has been fully operational and major improvements have been obtained on the roadmap towards 300mm microLED production. LED growth on the 300mm MOCVD system installed at Aledia/ Echirolles showed an emission wavelength centered on 446.4nm with very low standard deviation among the LEDs. "We are achieving very good uniformity and this is promising for further developments of 300mm Smart-Pixel integration", reports Jérome Napierala, epitaxy expert at Aledia. ◊

ONE OF THE EIGHT POSTERS CREATED BY THE STUDENTS OF THE BRASSART-GRENOBLE SCHOOL ON THE TOPIC **"LA MICROÉLECTRONIQUE POUR VIVRE DANS UN MONDE MEILLEUR"** (MICROELECTRONICS FOR LIVING IN A BETTER WORLD) FOR THE TECH&FEST 2024 FESTIVAL. **POSTER BY ERIC DECOUD, "GRAPHIC DESIGN" STUDENT**

#### Photonic sensors

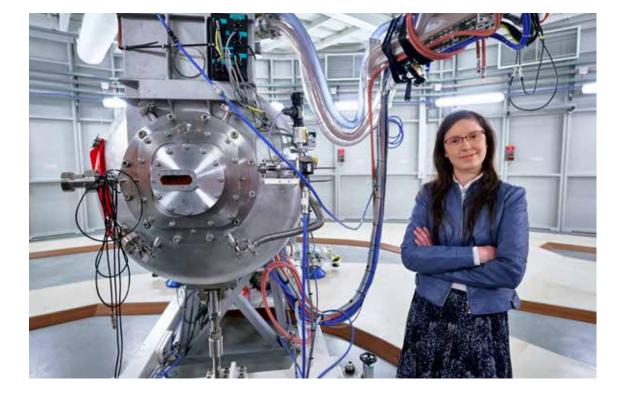

## Innovation in silicon photonics: from design tools to mass production processes

#### STÉPHANIE GAUGIRAN HEAD OF THE NEW PHOTONIC APPLICATIONS SECTION AT CEA-LETI & DIRECTOR OF THE NANOELEC/PHOTONIC

© UTOPIKPHOTO/CEA

According to the Yole "Silicon Photonics" report in 2023. The growing number of products under development for various applications sectors, including the flourishing Al sector, is driving the largest industrial foundries to invest in the development or even the creation of photonics platforms on their sites. Most of them around the world are already including co-packaged optics solutions in their rannes The partners in the Nanoelec/ Photonic Sensors program are preparing to be competitive on the emerging photonics on silicon chips market. This market should enjoy an annual growth rate of 44%, reaching more than 600 millions US dollars in 2027<sup>(1)</sup>.

Our aim is to provide the Nanoelec partners with a complete chain of solutions – from EDA to mass production – designed to facilitate the adoption of photonics on silicon by new applications requiring complex detection functions such as 3D detection in mobile phones, autonomous vehicles, or biochemical detection for health care and environmental surveillance.

In 2023, we studied new waveguide antenna array architectures with very low divergence at a wavelength of 1550nm. With regard to simulation and design tools, we worked on Process Design Kits tailored to the design of III-V components such as lasers and modulators and compatible with industrial standards, along with a numerical model of the gain function in a III-V materials laser. Work on hybrid lasers is continuing with two new designs and initial study on producing tunable lasers. Finally, we are beginning development of a photonic sensor for titrating ethanol, liable to be of interest to a number of large industrial

HYBRIDATION OF III-V MATERIALS ON A 300-MM INDUSTRIAL STANDARD WAFER © A.HAVRET/CEA

#### **PHOTONICS SENSORS AT A GLANCE**

#### → VISION

New sensor opportunities based on large-scale 300mm silicon photonic industrial technologies

#### → AMBITION

Provide the Nanoelec partners with a complete chain of solutions - from EDA to mass production designed to facilitate the adoption of photonics on silicon by new applications requiring complex detection functions such as 3D detection in mobile phones, autonomous vehicles, or biochemical detection for health care and environmental surveillance

#### → MISSION

5 -

Our main technological challenges for such sensors are measurement precision, miniaturization, data processing and transfer, and also compatibility with mass production. The unique properties and performance of integrated photonics are essential in being able to meet these demands and these challenges

→ PARTNERS Almae CEA CNRS Siemens EDA STMicroelectronics

(

#### **EMERGING APPLICATION**

### A photonic sensor to titrate ethanol

CEA-LETI IS DEVELOPING AN INTERFEROMETER TO DIRECTLY MEASURE THE CONCENTRATION OF ETHANOL IN VERY SMALL QUANTITIES OF LIQUIDS. THE APPLICATION COULD BE OF INTEREST FOR THE AGRI-FOOD INDUSTRY AND THE HEALTH SECTOR.

Titration of ethanol is of interest to numerous industrial players, for example in the field of paints, solvents and petrochemistry, as well as in the agri-food industry and the health sector. CEA-Leti's photonic platform, developed by the industrial and academic partners within Nanoelec, will act as the basis for development of a very low-cost sensor which can titrate ethanol in a volume of a few microliters of liquid. "We have chosen a photonics approach based on Mach-Zehnder interferometers (MZI) in the near-infrared band: a laser beam illuminates two channels, one of which contains a

micro-cavity for the liquid. The two beams are recombined and their phase shift depends directly on the quantity of alcohol in the liquid", explains Pierre Labeye, engineer at CEA-Leti.

Proof of concept was carried out in 2022 on the existing MZIs used to measure the absorption of colored inks in different concentrations. The etching process used to obtain a specific cavity for the liquid sample above the waveguides was developed in 2023. "The first operating tests performed with alcohol in early 2024 are promising", says Pierre Labeyre. ◊

Above, PIERRE LABEYE (CEA-LETI) IS DEVELOPPING A SENSOR FOR ALCOHOL DOSE TITRATION © O.DEVISE/CEA 2024

Top, MICROSCOPE VIEW OF THE PHOTONIC MZI CIRCUIT DESIGNED AND PRODUCED AT CEA-LETI FOR ALCOHOL DOSE TITRATION

© O.DEVISE/CEA 2024

On the right, DATA SCREEN FOR THE CIRCUIT DEDICATED TO ALCOHOL DOSE

© O.DEVISE/CEA 2024

Above right,

TESTING THE VERY FIRST PROTOTYPE OF A PHOTONIC SENSOR FOR ALCOHOL DOSE TITRATION © O.DEVISE/CEA

AGENDA

#### **CIRCUIT DESIGN**

### Design kits and model libraries for photonics process

THE CIRCUITS DESIGN AND MODELING SOFTWARE RESOURCES USED WITHIN NANOELEC NOW INCLUDE III-V COMPONENTS AND MODELLING OF A MACH-ZENDER INTERFEROMETER (MZI).

Within the Nanoelec consortium, Siemens EDA<sup>(a)</sup> and CEA are establishing reference flows for the design and verification of integrated circuits, and are developing process design kits (PDK) and verification software tools, as well as component model libraries (PMS).

"A PDK<sup>(5)</sup> provides a standardized methodology for the design and manufacture of integrated circuits, which is essential to guarantee their correct operation", says Jean-Marc Talbot, Head of Solutions & Strategic Partnerships at Siemens EDA.

The PDK generally comprises information about the

4. Siemens Electronic Design Automation SARL – Siemens EDA, world leader in design, verification and manufacturing assistance tools for integrated circuits, packages and PCBs, is one of the founding members of IRT Nanoelec. It is the only IRT Nanoelec partner in electronics and microelectronics CAD

**5.** Set of tools, data files and documentation supporting the design tools used to develop integrated circuits (IC)

**6.** SPICE (Simulation Program with Integrated Circuit Emphasis) is a free general-purpose simulation software for analog PCBs. It can be used to simulate the individual components (resistors, capacitors, transistors)

7. De Foucauld, E., Rozeau, O., Myko, A., Fowler, D., Virot, L., & Gays, F. (2023). Compact modeling of photonic devices in Verilog-A for integrated circuit design. Solid-State Electronics, 200 manufacturing process for integrated circuits, such as stacking, the steps in the process and the materials used. It also includes design rules which specify the constraints regarding the layout of the integrated circuit.

#### LASERS AND MODULATORS

In 2023, an extension module for the Siemens software suite was specifically developed to validate architectures of III-V components such as lasers and modulators. *"This new module can be superposed on various 300 or 200mm Photonic Core PDKs and on Si310 or SOI220 photonic technologies"*, explains Fabien Gays, in charge of the project at CEA-Leti. "It contains all the necessary levels for backside or frontside III-V integration and rule set for Siemens verification tool."

#### VALUE PROPOSAL FOR INDUSTRY

"On Spice<sup>(6)</sup> simulators, we are working with the other Nanoelec partners to determine the use cases and methodology associated with the use of PMS (Photonic Model Suite) libraries for actual industrial applications and the related circuits, in order to rapidly identify the value proposal", adds Jean-Marc Talbot. ◊

#### A FULL SILICON PHOTONICS PROCESS FLOW

## Verilog-A language to simulate photonic integrated circuits

SIMULATION OF A MACH-ZENDER INTERFEROMETER (MZI).

In a paper published in Solid-State Electronics Review<sup>(7)</sup>, scientists from CEA-Leti, working within Nanoelec, put forward a methodology to simulate photonic integrated circuits (PIC) using commercial IC simulators. "For this, all photonic devices are modelled using Verilog-A language including transmission and reflection of light", states Emeric De Foucauld, as first author of the study. "For each model, both polarizations, transverse electric (TE) and transverse magnetic (TM) polarized waves, are considered. The methodology is able to simulate resonant and interference effects

and we demonstrated waveguide and ring resonator simulations." The extraction of a Mach-Zender Interferometer (MZI) illustrates the modeling based on measurements with Nanoelec silicon technology developed by CEA-Leti: despite only being passive structures, these MZI were fabricated using a full silicon photonics process flow including active devices with ion implantation steps and two levels of Back-End-Of-Line (BEOL). "Simulations of attenuation and reflection demonstrate the advantages of this Verilog modeling", concludes Emeric De Foucauld.

#### APPLICATIONS

### Large-scale lidar

AN OPA INTEGRATION SCHEME HAS BEEN DRAWN UP WITH A VIEW TO INTEGRATION ON AN INDUSTRIAL PRODUCTION PLATFORM.

With a view to developing large-scale production of Lidars at low unit cost, Nanoelec supported Cyrille Barrera's thesis, prepared at STMicroelectronics<sup>(8)</sup>.

This work led to the definition of an integration scheme for an Optical Phased Array<sup>(9)</sup> on STMicroelectronics' PIC50G photonic platform. The scheme includes 256 photonic antennas, each being phasemodulated by an individual phase-modulator, and separated by 2 microns to generate a laser beam with 0.18° angular divergence, which can be repositioned in less than a microsecond for an average power consumption of less than 1mW.

Eleven scientists from CNRS, STMicroelectronics and CEA (including M. Barrera) working together in the Nanoelec/ Photonic Sensor Program reported<sup>(10)</sup> the demonstration of a 256-channel 1D optical phased-array (OPA) based on plasma-dispersion effect. "Our system exhibits ultra-low power consumption (~1mW) revealing the potential of a carrier depletion scheme at low doping dose for solid-state Lidar applications", comments Louise-Eugénie Bataille, as first author of the study. "All in all, our work indicates that the low-doped carrier-depletion-based OPAs have great prospects as ultralow power solid-state Lidar", she said. ◊

#### **OPTICAL PHASED ARRAY**

Operating at 1550nm wavelenght STMICROELECTRONICS AND CEA ARE DEVELOPING NEW SLOTTED WAVEGUIDE ANTENNA ARRAYS.

Obstacle detection with a Lidar requires a focused beam to ensure precise sweep, with the preference thus being for arrays with long diffraction and low diffraction force based on a low index contrast. "In this context, within Nanoelec, we were this year able to demonstrate a BIC (Bound state In the Continuum)

effect slotted waveguide antenna (SWGA) array one millimeter long, so as dual layers Si-SiN antennas, both designed to achieve divergence of less than 0.08° operating at 1550nm wavelenght", says Stéphane Monfray, Engineer, manager of the action at STMicrolectronics. ◊

#### 8. Design,

characterization and integration of a laser scanning system in silicon photonics for Lidar detection applications at 1.55 µm, PhD thesis defended on March 24, 2024 at Université Paris-Saclay

9. An Optical Phased Array (OPA) allows an optical beam to be directed at very high speed, without any mechanical movement, to scan a scene over ranges of several tens of meters

10. Bataille, L.-E., Barrera, C., Guerber, S., Monfray, S., Grosse, P., Fowler, D., Brision, S., Charlet, I., Vivien, L., Dagens, B., & Boeuf, F. (2023). Ultra-low power 256 channels optical phased-array based on low-doped carrierdepletion modulators. 2023 CLEO (2023, San Jose, CA, United States)

Low-doped

depletion-

based OPAs have great

prospects

as ultralow

power solid-

state Lidar.

#### **EMERGING CONCEPTS**

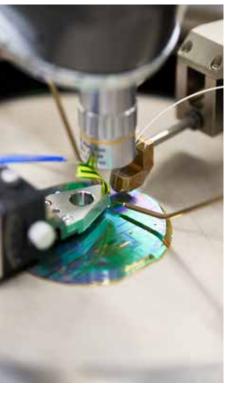

## Low-power low-loss phase modulators for Lidars

HYBRID InGaAsP/Si CAPACITIVE MODULATORS WERE DEMONSTRATED BY CEA FROM 300MM STMICROELECTRONICS PHOTONIC WAFERS.

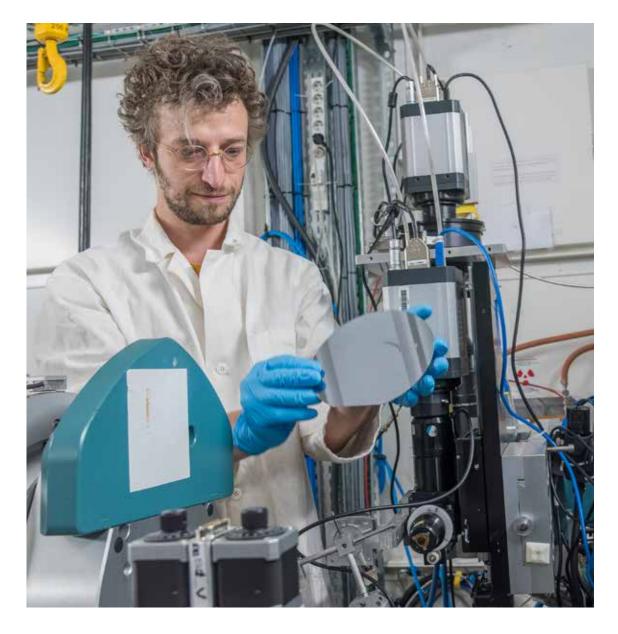

To control the beam scan in a Lidar based on optical phased array (OPA) circuits, a phase modulator in each arm of the OPA is needed. Since 2021, scientists working within the Nanoelec/Photonic program, from STMicroelectronics, CEA and Almae, have been developping a low-loss low-power phase shifter based on a III-V/Si hybrid capacitor integrated on standard silicon photonic circuits from STMicroelectronics. *"In 2023, we have realized and measured our first prototypes of hybrid*  modulators, based on the transfer of an InGaAsP layer onto a gate oxide of the order of 10nm. Dephasing up to 250°/mm have been measured on our first prototypes", explains Yohan Désières, in charge of the project at CEA-Leti. The following picture gallery shows the different steps in the fabrication and test of the demonstrator at CEA-Leti from photonics wafers made at STMicroelectronics and III-V epiwafer from Almae. ◊

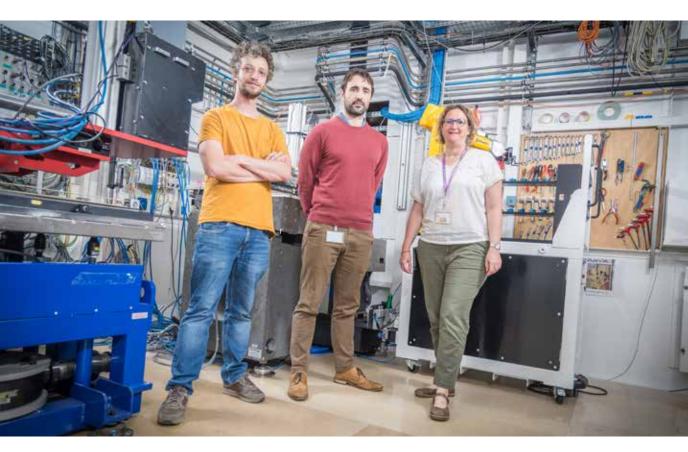

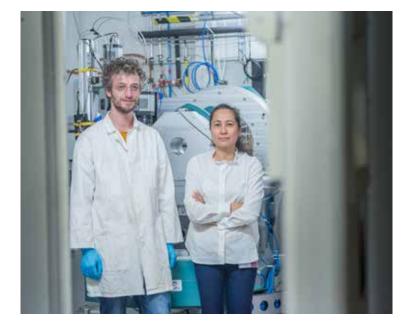

#### DEMONSTRATOR OF THE CAPACITIVE MODULATOR FOR LIDAR UNDER DEVELOPMENT AT CEA-LETI, WITH STMICROELECTRONICS AND ALMAE, IN THE FRAME OF THE NANOELEC/PHOTONIC SENSORS PROGRAM © A.HAVRET/CEA 2024

#### To the right,

Below.

TRISTAN FAURE, TECHNICIAN AT CEA-LETI, SUPERVISES THE III-V MATERIALS LITHOGRAPHY STEP FOR THE CAPACITIVE MODULATOR DEMONSTRATOR @ A.HAVRET/CEA 2024

#### To the right,

LOIC SANCHEZ, ENGINEER AT CEA-LETI, PERFORMING MOLECULAR BONDING OF WAFERS ON JOING OF WAFERS SUPPLIED BY ALMAE ON 300MM PHOTONICS WAFERS SUPPLIED BY STMICROELECTRONICS © A.HAVRET/CEA 2024

#### Below,

ELECTRO-OPTICAL MEASUREMENTS ON INGGASP/SI MODULATORS BY YOHAN DÉSIÈRES, PHOTONICS ENGINEER IN CHARGE OF THE CAPACITIVE MODULATOR PROJECT AT CEA-LETI © O.DEVISE/CEA 2024

Clément Castan, CMP (chemical & mechanical polishing) engineer at CEA-Leti, loads 300mm silicon wafers into the machine which is used for planarizing before molecular bonding of the III-V materials.

© A.HAVRET/CEA 2024

#### **UPCOMING TECHNOLOGIES**