# Scientific & technical highlights

# 04 Exploring the future of electronics

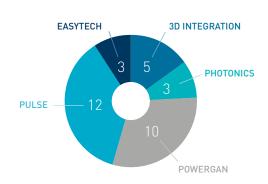

# 06 Key figures of the institute

December 2020

## 08 Trust restored

Director's foreword by Hughes Metras

## 10 Highlights

Our top stories

- 19 3D integration for image

- 33 Photonic Sensors

- 47 Digital Trust

- 63 PowerGan

- 69 Characterisation

- 79 Human capital& Training design

- 87 Technology dissemination

- 97 Artificial Intelligence

100 Europe

#### SCIENTIFIC & TECHNICAL HIGHLIGHTS OF THE IRT NANOELEC 2021 EDITION

Director of publication: Hughes Métras Writing and editing: François Legrand English translation: Aerotraduction

Layout: **Supernova**Cover: **Florence Pillet**Grenoble, July 2021

# Exploring the future of electronics

IRT Nanoelec runs multi-partner technology development and dissemination programs to make the electronics sector more competitive.

"Working together to carry out responsible research and development programs to help businesses create value."

The Nanoelec technological research institute is a consortium of private and public sector players.

Our mission is to help companies create value and enable their products to stand out on the digital transition stage.

Nanoelec contributes to the competitiveness of the electronics sector, especially in France. It is based in Grenoble, a world-class hub for research, innovation and production in the field.

Our R&D programs are built jointly by representatives from the academic and industrial worlds. They deal with the design and development of new processes, systems and components in the following fields:

- → photonic sensors, new-generation displays and smart image sensors,

- ightarrow technologies for connected objects,

- → energy conversion,

- → characterisation and resistance to radiation of components and systems by means of large instruments.

Nanoelec also runs training design and technological dissemination programs for SMEs. With the support of the Auvergne Rhone-Alpes region, we implement open innovation methods as well as more conventional technological development methods for technology dissemination.

Given the pervasive nature of digital technologies, Nanoelec is in contact with actors from all sectors ranging from goods to services, industry and infrastructures to consumer products, not forgetting transportation, environment and health.

Nanoelec is one of the technological research institutes (IRT) and energy transition institutes (ITE) set up by the French Government and financed by the Investments for the Future program (PIA). These institutes pool academic and industrial players on R&D and their innovation projects aimed at boosting competitiveness of the french economy.

# ANTICIPATING FUTURE SKILLS AND TECHNOLOGICAL NEEDS

### Microelectronics innovation

- → Carry out world-class collaborative R&D on common roadmaps gathering industrials ans academics

- → Develop and transfer these technologies to create the electronic circuits of the future

- → Give industry players access to development, prototyping and advanced characterization resources

## Technology dissemination

- → Help businesses in the field of information and communication technologies meet the challenges of IoT and digital trust and security

- → Provide expertise to help SMEs from various industrial sectors build new products and services with innovative components and embedded software

- → Promote cooperation between SMEs, mid-caps and large companies

- → Collaborative innovation to unveil new applications

## Development of human capital

- → Attract young people into jobs in electronics through inclusion, responsability, equality, sustanability

- → Map out needs and assess employment opportunities

- → Design training courses to meet current needs

- → Anticipate future skills required in the sector: sustainability, cross-skills, social and technical communities for innovation

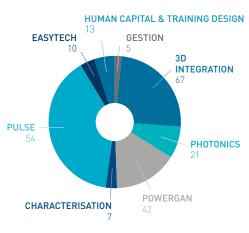

# Key figures of the institute

**DECEMBER 2020**

A consortium of **public & private**

members

(21 partners as of December 2020)

€54M

average annual budget

258

associated partners including 198 SMEs since 2012

472

scientific or technical publications & communications

since 2015

**199** patents and **43** software filed since 2012

PATENTS & SOFTWARE FILED 2020

219

Full Time jobs -31% in from private companies in 2020

HUMAN RESOURCES (IN EQUIVALENT FULL-TIME)

# A renewed trust from our stakeholders

by Hughes Metras, Director of the Technological Research Institute IRT Nanoelec

The Electronics industry is experiencing a period of tension in terms of component availability, the shortage of which is affecting all products: mobile phones, PCs, digital infrastructures, automobiles, etc. As a result, in 2020, the French and European players in the semiconductor sector became acutely aware of the issues of sovereignty and relocation: Owing to their large-scale dissemination, digital systems are at the heart of our economy. This pervasiveness also makes the entire digital sector a prime target for cybersecurity threats: not a week goes by without increasingly sophisticated attacks impacting our public and private economic players.

Following on from the mission entrusted to us by the French Public Authorities in 2012, Nanoelec is addressing some of these challenges, with the aim of successfully completing collectively defined R&D programs. This open collaborative framework is the very DNA of all the IRTs and ITEs under the FIT (French Institutes of Technology) umbrella.

Nanoelec renewed its convention with ANR, the french national research agency. Thanks to this reaffirmed trust and the results obtained over the last nine years in core technologies such as chip stacking, silicon photonics and component security, we set out a range of roadmaps for the period 2021-2025, to target key applications fields for the industrial partners in our consortium.

One of our ambitions is to support our local ecosystem, specialized in the field of imagers, in the move towards smarter sensors and help them identify or anticipate new applications for their components.

Our project in the field of microled displays is a good illustration of how technological innovation can help our industry bring back manufacturing activities that have been abandoned by Europe for a long time. The Smart Pixel concept, which underpins the ambitions of this project in the field of high-end displays, bears witness to the inventiveness of our partners.

Finally, we decided to set digital trust as the core of our developments, in order to address security issues of the IoT, home health care and industrial sectors.

"The IRT renewed its convention with French public authorities."

"The Electronics sector provides the essential industrial base for the design and production of increasingly smart and connected objects in the world around us. The sector thus lies at the heart of the national industrial dynamics and is a powerful force for the development of sectors through innovation and competitiveness."

STRATEGIC CONTRACT OF THE FRENCH ELECTRONICS SECTOR 2018-2022

The diversity of our consortium which, around the Minalogic hub and CEA, gathers local academic teams, key industrial players in the ecosystem including large Groups, midcaps, SMEs and startup, enables us to look to the future with confidence and ambition, while continuing with our technological development, training engineering and dissemination missions.

This latter includes building R&D and scientific services offerings around the advanced physical characterisation skills of our partners operating the Large Instruments in Grenoble, around our silicon technology platforms and our innovative systems integration and testing resources.

Resilience and sustainable development are the facets of the lens through which society (including the endusers of the digital systems) analyzes and questions itself. The younger generations are challenging us on these issues. Evidence of this is the strong commitment of the GEM and Grenoble-INP students who took part in our workshop to design a green phone last February.

In 2021, we are picking up the challenge: we will implement lifecycle analysis tragetting projects at the R&D phase, evaluate environmental diagnosis tools for the Easytech projects and pursue our actions on professional equality in the electronics sector.

IRT NANOELEC Director's Foreword 9

# **Highlights**

#### January 2020

#### Learning communities

→ First "Sustainable Electronics" module rolled out with experts from STMicroelectronics, CEA and UGA to 40 master's students.

#### 🙀 January 2020

#### 3D Architecture

→ In January 2020, Perceval Coudrain receives a "Best Paper Award" for his paper entitled 'Active Interposer Technology for Chiplet-Based Advanced 3D System Architectures' presented at ECTC conference 2019.

#### January 2020

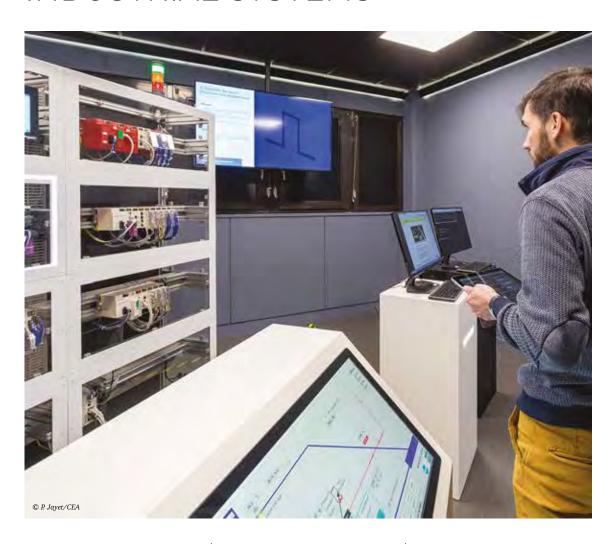

#### Industrial cybersecurity

→ Nanoelec teams present Industrial IoT Security developments at the International Cybersecurity Forum (January 2020, France).

#### February 2020

#### Senior Care

→ Launch of Cocoon Care. The startup is marketing a solution to detect falls. based on a new generation of detectors and an events management and tracking platform.

#### February 2020

#### **Optoelectronics**

→ CEA-Leti silicon photonics platform developed within Nanoelec is presented at Photonics West international conference

March 2020

#### **Power Electronics**

→ STMicroelectronics acquires majority stake in Gallium Nitride innovator Exagan. It's a new context for Nanoelec/Powergan program.

#### March 2020

#### Characterisation

→ 25 PhD students discover characterisation techniques based on neutronic and X-ray synchrotron radiation. The training module was adapted to digital format.

#### **□** March 2020

#### **Batteries**

→ Limatech, a startup that has benefited from the support of Nanoelec/EasyTech, raises €2 millions for the development of its lithium battery systems for aeronautics.

March 2020

#### Nanoelec goes online

→ "Bridging the gap between semiconductor technologies and architecture design" is the title for the very first online webinar at Nanoelec. It is organized for the Date 2020 international conference. 3D Integration, Powergan and Photonics at a glance are covered: 11 key players from our community -including. CEA, Siemens EDA, STMicroelectronics, Schneider Electric, Prophesee and Polytechnic University of Valencia (Spain)- gave talks during the event.

#### March 2020

#### Global Shutter Imagers

→ STMicroelectronics is starting to ship high-performance global shutter image sensors. Their unique backside illuminated global-shutter pixel uses ST die-stacking technology that benefits from results of the Nanoelec 3D program.

11 Highlights IRT NANOELEC

# **Highlights**

(🗘) April 2020

#### **Digital Twin**

→ Siemens EDA joins the PowerGan Program to work on digital twins for energy converters.

May 2020

#### Infra-red imagers

→ Lynred joins the Nanoelec consortium in May 2020 to accelerate new imager developments.

#### **Smart cities**

→ Kentyou is created. The startup provides open digital solutions, to collect and analyze urban data and enable local innovators to build custom solutions that respond to citizens' needs.

April 2020

#### **Energy Storage**

→ Lancey Energy Storage, a startup that has received Nanoelec/EasyTech support, ranks second in the "Sustainable Society Startup Challenge" of the MIT Global Startup Workshop 2020.

May 2020

#### Safety of industrial systems

→ CEA-Leti and Davey Bickford Enaex, collaborating in the frame of Nanoelec, unveil the demonstrator of a new wireless system that offers increased safety, flexibility and productivity gains to the blasting market.

**August 2020**

#### SMEs go digital

→ 1.1 million € to support companies in their digital transition through the Digifed EU program coordinated by CEA through Nanoelec.

**June 2020**

#### Government support

→ Frédérique Vidal, French Minister of Higher Education, Research and Innovation announces € 450 million over 5 years for technological research and energy transition institutes (IRT & ITE), including Nanoelec.

**June 2020**

#### **Business Meetings** for SMEs

→ The Nanoelec/Easytech program take part in online Minalogic **Business Meetings.**

September 2020

#### General Assembly of the institute

→ Online sharing of achievements and insights on technological and social issues such as resilience, sustainable development, gender parity and open innovation.

**July 2020**

#### Webinar on photonics on Si

50 international attendees for Nanoelec speakers (CEA-Leti and CNRS-LTM) share online their latest results & achievements in integrated photonics technology.

13 Highlights IRT NANOELEC

# Highlights

September 2020

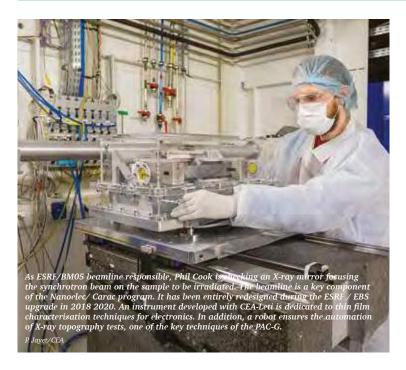

#### X-rays shine

→ ESRF/EBS comes in operation after two years of upgrade. The new machine is the most brilliant synchrotron in the world.

October 2020

#### **IOT Security**

→ The Nanoelec/Pulse program and IRT Saint-Exupery take part in a webinar organized by the SCS competitiveness Cluster on the latest updates and user cases in IOT Security.

September 2020

#### Robotics & Digital Fair

→ Nanoelec/Easytech at the Sido fair combining IoT, AI & Robotics in Lyon.

September 2020

#### 660 students in a (digital) classroom

→ For the very first time, 660 GEM students come together for an original digital Back-to-School challenge designed with Nanoelec.

October 2020

#### Best paper award for photonics

→ Andrea Quintero, PhD graduate receives a **Best Paper Award** at ECS Prime 2020 for her comprehensive study of the impact of Sn content on the Ni / GeSn phase sequence.

#### October 2020

#### Characterisation for powering GaN technology

→ 219 attendees for a webinar on characterisation techniques for GaN components & systems organized by Serma technologies, Nanoelec, Surface Lab and CEA-Tech.

#### Movember 2020

#### French public authorities renewed agreement

→ The contract renewal for IRT Nanoelec is finalized and signed by CEA and the French Research National Agency (ANR): It secures institute funding up to June 2023 with an allocation of 43 M €.

#### November 2020

#### Characterisation

→ The 7<sup>th</sup> edition of the Nanoelec/Carac Symposium attracts 50 attendees.

#### November 2020

#### Silver Economy

→ Nanoelec experts involved in the Activage EU project participate in a workshop with more than 100 professionals addressing senior care industry and services in the Grenoble-Alps area.

→ STMicroelectronics. Schneider Electric and Lynred present the first integration of Edge Al in a high-performance people-counting sensor developed within Nanoelec.

15 Highlights IRT NANOELEC

# Highlights

#### November 2020

#### Cvberweek

→ Esisar, a school of the Grenoble-INP group and a core member of Nanoelec, organizes the European node of CSAW, the most comprehensive student-run cyber security event in the world

#### December 2020

#### Radiation testing of semiconductor devices and systems

→ Nanoelec/G-Rad workshop on current and future needs in radiation hardness testing and evaluating the limitations of radiation facilities and developments.

#### January 2021

#### Blockchain and digital identification

→ A public comprehensive talk by Christine Hennebert (CEA-Leti) associated with the Nanoelec/Pulse program.

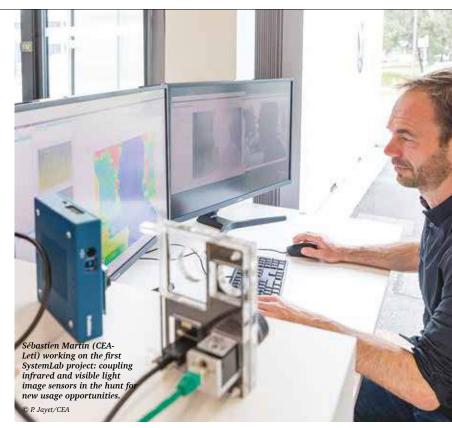

#### December 2020

#### Open innovation

→ Preconfiguration of Nanoelec/SystemLab initiative, a new way forward for technology dissemination, by identifying innovative use cases.

#### 😭 February 2021

#### Sustainable Electronics

→ 57 students from Grenoble-INP and GEM took part in a "Sustainable Electronics" workshop organized as part of the Nanoelec/Human Capital and Training Engineering (Chif) program, with an original serious game "My IOT" created by Nanoelec and Need for IOT (Idex UGA).

#### Partners confidence renewed

→ Industrial and academic partners of Nanoelec finalize a new version of the consortium agreement.

#### March 2021

#### Open hardware

> Nanoelec strongly supports the Risc-V week attracting close to 400 scientists from 33 countries.

#### April 2021

#### Digital training transition

→ Grenoble Ecole de Management (GEM) "Back to school 2020 challenge" is praised for its positive societal impact by AACSB within the framework of the annual challenge "Innovations that inspire".

#### March 2021

#### Woman Engineer

→ Severine Cheramy (Product line manager at Aledia) receives the "Engineer of the year 2021" award from the 3DinCites professional review dedicated to the international 3D architecture community.

#### Display expertise

→ The Fellow Award of the Society For Information Display Fellow Award goes to François Templier, director of the Nanoelec/ Displed program.

17 Highlights IRT NANOELEC

# **Highlights**

May 2021

#### White paper

→ A 100-page report on blockchain for personal identity privacy is published by the French Interior Ministry, Thales and Nanoelec, with CEA.

May 2021

#### **SMEs**

Nanoelec/Technology dissemination program takes part in Minalogic Business Meetings 21.

June 2021

#### **IOT** security

→ Digifed Generic Experiment Community on cybersecurity is kicked-off with sixteen French and European SMEs interested in strengthening the security of their embedded applications for the Internet of Things (IoT).

#### **♀**↑ June 2021

#### **Gender matters**

→ Nanoelec and Giant Campus organize a special public event on June 23th, the International Women in Engineering Day.

# 3D integration for image

3D integration, which consists in interconnecting electronic chips in 3 dimensions, is a promising solution to address the growing need for functionality, density and performance in future integrated circuits. However, to allow the rapid emergence of this technology in industry, an overall approach is needed, taking account of technological development, new circuits architecture, development of new design tools, testing and reliability technics.

From 2012 to 2020, the academic and industrial teams working under the Nanoelec/3D Integration program focused on developing a comprehensive platform compatible with the full design cycle of new products. They dealt with technology, but also design, electronic design automation tools (EDA), testing and reliability.

As of 2021, this activity is giving way to two new programs focusing on applications: one devoted to image display technologies (Displed) and the other to sensing (Smart Imager).

# Towards Display Technology Leadership in Europe

François Templier, CEA Research Director and Society For Information Display (SID) France Chapter Director, heads up the brand new Nanoelec/Displed program.

What drives you in the program you're heading up?

I've been managing CEA-Leti's Display Tech program since 2017. Management of the Nanoelec/ Displed program allows me to broaden the scope of our cooperation with display manufacturers in a multilateral context. We should be able to accelerate our road map for supporting industry by getting stakeholders from different levels in the value chain around the same table. We intend to develop a radically new microLED-based, high-performance display based on a so-called "Smartpixel" chip, for which we'll expand the application fields and strengthen mass production processes. We'll open up the way to ultra-high resolution video walls, very large flat screens for television or interactive meetings, flexible displays and screens prompting a real feeling of 3-dimensional immersion in a virtual or remote world.

#### What is the Smartpixel you refer to?

It's a component that integrates a number of red, blue and green microLEDs into a unique control circuit co-assembled on a CMOS standard wafer. Each of these "Smartpixel" units is then transferred to a connecting media that constitutes the screen. This breakthrough approach will nevertheless require new developments, in particular the so-called "mass transfer" step. Ultimately, we'll benefit from higher performance displays

enabling new functionalities; this represents a real technological and economic breakthrough. It's exactly this opportunity that we're adressing within the Nanoelec/Displed framework.

# Why is it essential to continue developing very high performance image display systems and to be capable of manufacturing them in Europe and France?

By federating key industrial and academic players, our ambition is to rebuild a display industry in France and Europe that can be as strong as the one we had during the time of cathode ray tubes, which were ousted in the 1990s by LCDs of Asian origin.

We live in a society in which images are increasingly present. Why is this? Well, not only because people are staying longer and longer in front of displays, but also because they are seeking systems that are more immersive and free of the constraints such as 3D glasses, for example. New display technologies must ensure not

# **Displed program** at a glance

#### ∇ISION

A unique opportunity for a French & European ecosystem on large display technologies for immersive applications

#### AMBITION

To design and demonstrate key microLED technologies towards high-end, immersive/interactive displays

####

To develop process flows for microled, Smart-pixel fabrication and mass transfer requirements

#### & PARTNERS

Aledia | CEA | EVGroup | Plasmatherm | SET

only higher image qualities, but also enhance functionalities (3D Multiview, flexible screen, interactivity). It's legitimate that European and French industries build a solid offering in the microLED market, thereby taking advantage of its very dynamic growth, which should approach 3 billion USD in 2024, especially in relation to television (TrendForce market intelligence provider).

#### What is your career path?

I've been involved in digital display development for 28 years. I first worked at Thales before joining CEA in 1999. While performing the various functions of researcher, project manager and program manager, I've worked with every type of display (LCD, OLED, microLED, microscreens, flexible screens, TFT active matrices). Finally, my involvement as director of the France Chapter of the Society For Information Display (SID) allows me to continuously consolidate a 360° view of the state of the art in this field.

IRT NANOELEC 3D INTEGRATION FOR IMAGE 21

# From imaging to vision sensing

The Nanoelec/Smart Imager program is committed to providing relevant and real-time environment analysis by vision. It could be one of the greatest technical challenges at Nanoelec for the coming years. Overview by Eric Ollier, Program Director.

## What are the opportunities for smart imagers?

There is a growing number of applications where sensors become a vehicle for decision and action. There are market opportunities for consumers, smart buildings, healthcare, industrial process flows and monitoring, automotive and robotics. Mastering smart imagers industrial process flow would be a competitive advantage for Nanoelec's industrial partners.

#### Tell us why this program represents a real breakthrough and paradigm shift?

For the development of smart imagers, computing and data storage are the main challenge, in addition to image collection. Several technologies –CMOS image sensors, 3D stacking, AI, Neural Networks– are now mature enough to address new possibilities. A wide range of processing functions is possible, including multi-spectral management and associated data fusion. We have to 'wrap-up' these possibilities to build new functions in multispectral image analysis for example. To do that we must develop and combine the best 3D stacking technologies and also imagine the best architecture and partitioning between functions, including neural networks embedded in the smart sensor.

#### How does artificial intelligence integrate imagers?

To make the leap from image generation to information extraction, we intend to embed artificial intelligence processing inside the sensor. And this will require a dedicated embedded computing die. So we have to think about a new hardware and software architecture capable of enabling the implementation of a neural network and additional digital processing inside the smart sensor.

#### What is your strategy?

Our main goal is to evaluate the benefits of 3D-stacking technologies. This encompasses a wide range of inno-

vations in silicon technologies – process and characterization, design, design tools, architectures, software engineering - as well as in the field of software.

## What in the Nanoelec background enables it to start such a challenging new program?

The previous "3D integration" program has been very active in terms of technological developments, publications and IP. The partners of the Smart Imager program intend to use this legacy and pursue this policy actively, especially to strengthen the foundations of our stacking technology for new 3D architectures.

## Form your personal point of view, what is the most exciting part of the program?

I think what is most exciting is the fact that we have to find practical and industrial solutions based on the

most advanced technologies to embed artificial intelligence in the smart imaging sensor. It is also highly motivating to work in very close collaboration between R&D and industrial partners, working with various teams involved in hardware technologies but also in design, design tools, architecture, Al... Finally, it's very exciting to prepare the next generation of smart imaging sensors!

#### Smart Imager program at a glance

#### ∇ISION

The transition from imagers to vision sensors generates new market opportunities

#### AMBITION

To provide key harware and software building blocks, to validate them through demonstrations ranging from test vehicles and proofs of concept to the prototyping of a smart, multi-layer imager

####

- Stacking/3D technologies, embedded AI and data management,

- New architecture

#### 88 PARTNERS

CEA | Grenoble-INP | Lynred | Prophesee | Siemens EDA | STMicroelectronics |

> Mastering smart imagers industrial process flow would be a competitive advantage for Nanoelec's industrial partners.

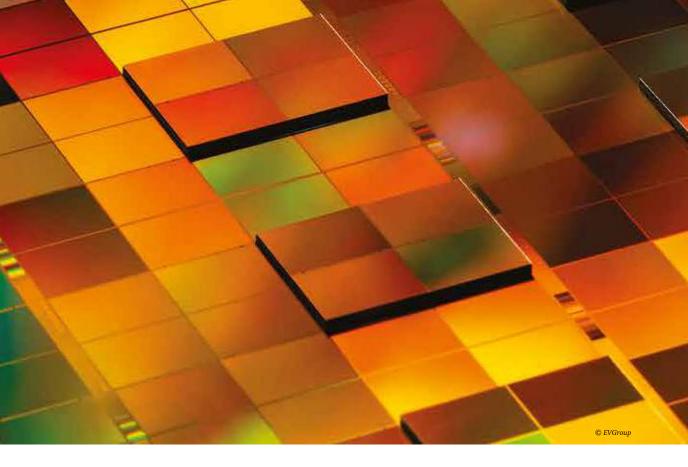

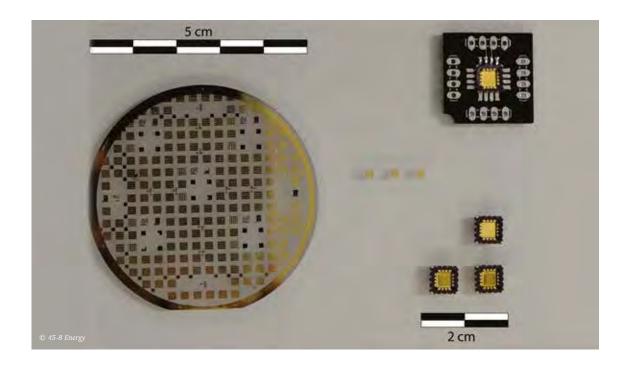

# COLLECTIVE DIE-TO-WAFER BONDING

EV Group, a core partner of the Nanoelec consortium, successfully demonstrates end-to-end process flow for collective die-to-wafer bonding with sub-two-micron placement accuracy, (see PR in last October). This breakthrough represents an important milestone in accelerating the deployment of heterogeneous integration in next-generation 2.5D and 3D semiconductor packaging. Such technologies are required for leading-edge applications such as artificial intelligence, autonomous driving, augmented/virtual reality and 5G, all of which require the development of high-bandwidth, high-performance and low-power-consumption devices without increasing production cost.

The demonstration was achieved at the EV Group Heterogeneous

Integration Competence Center, utilizing existing EVG wafer bonding technology

and processes, as well as existing bond interface materials, with substrates

provided by Nanoelec and CEA-Leti.

Markus Wimplinger,

Corporate Technology

Development & IP Director

at EV Group, explains.

#### For EVG, what are the key benefits of wafer-to-wafer direct hybrid bonding for industry?

In recent years, leading semiconductor companies have stated in public that 3D integration technologies will be part of their next process technology nodes currently under development. This trend has boosted a growth of wafer bonding applications. Wafer bonding was first applied for CMOS image sensor (CIS) manufacturing. Going forward, it is moving to more mainstream applications such as NAND flash memory manufacturing, where hybrid bonding is used at first producers to integrate the cell array with the periphery circuit. Across all fusion and hybrid bonding applications, EVG provides clear technology to hold a dominant market share.

# With the increased momentum for 3D integration for future logic devices, wafer bonding may reach certain limits. What are the key gaps to enlarge the range of applications using 3D integration?

One key gap for stacking technology is that wafer-to-wafer (W2W) bonding technology is not the only solution required for integrating chiplets with one another. There are many scenarios where die-to-wafer (D2W) integration will be required. Several approaches are under development, and have reached varying levels of maturity.

This relates to many of the building blocks involved, such as having a clear consensus on the preferred process flows as well as the precision and cleanliness of pick and place equipment. While it would be intuitive to favor direct placement/ fusion bonding of the dies in the pick and place equipment directly onto the receiving wafer, there is room for alternatives process flows with a collective approach to avoid cleaning and plasma activation of individual dies.

#### How far are you looking to win new markets or to reinforce your position integrating this new process?

Many people believe that a "collective D2W" bonding flow<sup>[1]</sup> can be an efficient route toward achieving maturity and high yields for D2W fusion and hybrid bonding. EVG already has installations in the field that support this process flow in high volume manufacturing for non-mainstream semiconductor applications. The work done last year and presented in our press release has resulted in the

[1] Where the dies are placed on a carrier to be cleaned and plasma activated collectively – through wafer level processing – on this carrier.

definition and demonstration of an end-to-end process flow for collective D2W bonding that EVG can now offer to its customers via EVG's Heterogeneous Integration Competence Center.

Through this work, EVG has improved its industrial standard cleaning and surface activation technology. This could set a new standard for how D2W bonding, and in particular cleaning and surface activation, will be done. Therefore, we expect to reinforce EVG's leading position with respect to technology and the market.

#### What has been the contribution of Nanoelec to the demonstration of the full process?

IRT Nanoelec and CEA-Leti have been providing the wafer material required for this development work. The wafer material was set up to enable hybrid bonding using Cu interconnects. The work would not have been possible without this material. We would like to thank IRT Nanoelec and CEA-Leti for this important contribution.

### Will the process be intensively used?

We have clearly seen a huge and growing interest in D2W bonding over the last few years. For this reason, we expect that the process will find significant interest and use in the industry.

#### How can EVG benefit from collaboration in the French Nanoelec institute?

EVG does not have the capability to prepare adequate test material in-house for such applications. For this reason, the partnership with CEA-Leti within IRT Nanoelec is very important, as it connects EVG with world-leading capabilities from the other partners in this consortium. Moreover, this collaboration gives EVG access to the required materials and technologies and also enables it to perform leading-edge research and development.

MARKUS WIMPLINGER, Corporate Technology Development & IP Director at EV Group

the clean rooms at CEA-Leti. The machine enables electronic chips to be

produced with extremely high alignment precision.

© Aubert/CEA

# ACCELERATING 3D INTEGRATION TECHNOLOGY IN INFRARED DETECTORS

Lynred, a global leader in designing and manufacturing high-quality infrared technologies for the aerospace, defense and commercial markets, joined the Nanoelec consortium in May 2020.

David Billon-Lanfrey,

CSO in charge of Strategy,

Corporate Communication

and Technology at Lynred,

explains some of the advantages that working with IRT

Nanoelec will bring.

#### Lynred has primarily joined Nanoelec to work on imaging developments. Are the projects you'll be working on specifically about infrared (IR) technology?

We specialize in infrared technology. That encompasses a very broad spectrum of technical solutions and applications designed for a very diverse range of sectors, including space imaging, thermographic imaging, defense systems and driverless vehicles. Lynred's IR sensors are critical components used by many of the major players in the commercial thermal imaging sector in Europe, Asia and North America. While maintaining our positioning in infrared imaging, we are keen to leverage key developments in a much wider market, that of visible-light imaging. This is our aim in working in collaboration with Nanoelec.

#### What are the challenges and obstacles you are facing in terms of technology and component modeling?

Like many developers in the electronic sector, and especially in the field of imaging, we take the 'More Than Moore' approach. That's the historical trend. Our first goal, therefore, is to reduce pixel pitch on our imagers so that we can achieve higher resolution images. We can use 3D architecture to help us achieve higher resolutions.

This should also enable us to integrate new smart signal processing functions, at pixel level, as well as to produce lighter, more compact imagers. Thanks to 3D stacking architecture, we will be able to diversify the range of applications and markets for our solutions.

CMOS technology cannot be directly transposed for infrared applications, notably because our imagers are cooled, usually to -150°C, and this is not the case for components used in applications that are more conventional. Another major difference compared to visible light imagers is that most electronic components are produced on 300 mm silicon wafers, the most widely-used industry standard, whereas our components are produced on 100 mm or even smaller wafers. As you can see from these examples, we need some R&D to adapt the cutting-edge 3D technology developed at the Nanoelec IRT to our needs.

#### What attracted you to the multipartner environment at Nanoelec?

We see it as essential to maintain close links with the innovation ecosystem in the field of microelectronics. Nanoelec provides a great

environment for pursuing R&D with the different partners working within that ecosystem. Innovation is the key to be able to build and develop new competitive advantages in a market increasingly dominated by players in the USA and Asia.

## Is Nanoelec also likely to open up new markets for your products?

By integrating image-processing functions within the sensor, we hope to create imaging solutions with high benefit for our customers in extremely demanding markets in terms of product performance, from military aeronautics to driverless vehicles. For example, for next-generation fighter jets, this would provide longer-range imaging for reconnaissance missions, and improve self-protect and threat-detection systems. For the next generation of vehicles, this will improve safety, even in poor visibility conditions such as darkness and fog.

IRT NANOELEC 3D INTEGRATION FOR IMAGE 27

# LEVERAGING IC DESIGN TOOLS AVAILABLE FOR 3D ARCHITECTURE DESIGN

Siemens EDA (ex. Mentor Graphics) is the sole EDA (Electronics Design Automation) partner of Nanoelec. It is providing design & verification tools for the benefit of the Nanoelec research institute's designer community. In addition to providing this valuable support, Mentor also uses the community's feedback to continually improve its design tools within the context of their performance in use on IntAct sophisticated demonstrators.

Juan Rey,

VP Engineering at

Siemens EDA Design2Silicon

Division, focuses on accurate

physical verification of

innovative 3D-IC designs.

How has Siemens EDA's Calibre 3DSTACK been an essential tool for the architecture design of Intact, the 3D manycore circuit partitioned using an active interposer presented by Nanoelec last year?

The accurate Physical Verification of such highly complex demonstrators requires efficient and high performance engines made available through a leading edge product suite. A fundamental tool in the signoff verification of 2.5D/3D-IC designs is Calibre 3DSTACK. Calibre 3DSTACK extends Calibre die-level signoff verification to enable complete signoff verification of a wide variety of 2.5D and 3D stacked die assemblies. With Calibre 3DSTACK, designers can perform signoff DRC

and LVS checking of complete multi-die systems at any process node without breaking current tool flows or requiring new data formats, significantly reducing time to tapeout.

# How does Siemens EDA's Calibre 3DSTACK benefit the Nanoelec IntAct demonstrator?

Calibre 3DSTACK was used extensively during the IntAct demonstrator signoff/final verification (before manufacturing), allowing for the capture of errors that traditional '2D' tools would have missed given the complexity of such design. The consequences of failing to capture these errors during the verification stage could have been substantial, resulting in either a functionality/specification limitation or even worse, a complete chip failure.

# Does Siemens EDA also provide innovative tools for reliability and physical stress analysis?

In addition to providing this signoff 'stamp' to IRT Nanoelec demonstrators, Siemens EDA is also proposing

innovative prototype tools for IRT Nanoelec partners. Thermal analysis for 2.5D/3D has been one strong research axis over the past years, allowing CEA-Leti to perform architectural studies for their future demonstrators. 2.5D/3D Reliability and physical stress analysis are other topics of interest that Siemens EDA and Nanoelec partners will continue to study over the coming months.

IRT NANOELEC 3D INTEGRATION FOR IMAGE 29

### VIPs in Science

#### **SEVERINE CHERAMY**

Product line manager at Aledia, received the "Engineer of the year 2021" award from the 3DinCites professional review dedicated to the international 3D architecture community. Until last February, Séverine was senior business developer at CEA and director of the former Nanoelec/3D integration program.

Severine Cheramy (Product line manager at Aledia) received the "Engineer of the year 2021" award from the 3DinCites review © A. Alix/CEA

#### FRANÇOIS TEMPLIER

Strategic Marketing manager for displays at CEA and director of the Nanoelec/Displed program,

received beginning of 2021 the Society For Information Display fellow award "for his many contributions to the science and technology of thin-film transistors, flexible displays, OLED microdisplays, and GaN micro-LED displays."

# 3D DEMONSTRATORS FOR DISPLAYS

Within Nanoelec, Aledia and CEA-Leti are developing their technological know-how in order to produce new types of displays that are brighter, offer more dynamic contrast and display speed and are more energy frugal.

"These developments employ all the know-how of the Nanoelec/3D program for match-up, plate to plate assembly and interconnection of a light emitting module (LEM) pixelated wafer with a CMOS wafer. The aim is collective interconnection of hundreds of millions of 3D LEDs with CMOS components, with the LEMs providing brightness in three colors (red-green-blue in a single pixel) while the CMOS wafers house

the pixel control function", says Philippe Gilet, CTO & Co-founder of Aledia.

The various technological building blocks are being studied in parallel by means of demonstrators. In 2020, the proofs of concept were specified and designed, in particular for interconnections between the various layers of 3D pixels. "The challenge is to succeed in achieving assemblies of plates and not of individual

pixels", points out Séverine Chéramy, Product Line Manager at Aledia. "And we are aiming for production in accordance with microelectronics standards (200 or 300 mm on silicon) whereas most of today's practices use more specific substrates with small surface areas. Standardized production will enable us to significantly bring down costs."

# Key publications

#### Embedded ultra-thin silicon vapor chambers for the cooling of microelectronics device hotspots

Thermal management, and more precisely hotspots attenuation, have nowadays become one of the most critical aspect in the design of microelectronic components, especially in the case of compact mobile applications. For his PhD thesis, Quentin Struss studied the design, the fabrication and the characterization of an ultra-thin silicon vapor chamber integrating a micropillars capillary wick. It can be directly embedded on the backside of a CMOS component in order to reduce hotspots intensity.

"A vapor chamber is a passive phase-change cooling device, which evaporation and condensation cycles leads to significantly higher heat transfer performances compared to classical heat spreading solution. A numerical estimation of such device made out of silicon with a total thickness of 600 µm has shown a 1.2 K.W-1 reduction in thermal resistance compared to a classical copper heatspreader with the same dimensions", Struss underlines. "We combined analytical and numerical models and experiments to demonstrate a microfabrication process flow, compatible with the presence of a CMOS component on the front side. An innovative collective wafer level filling and sealing approach has also been developed and allows, for the first time, the fabrication of a silicon vapor chamber with no filling hole, bringing these devices closer to an industrial production." Quentin also presented his work in a paper at 2020 Electronic Components and Technology Conference (IEEE 70th ECTC).

#### **QUENTIN STRUSS**

Vapor Chambers for high performance two-phase spreading/cooling

Thesis defended on Dec.18, 2020 at Insa Lyon in collaboration with Univ; Sherbrook (Canada), CEA-Leti, STMicroelectronics and Nanoelec

#### Increasing chip-to-chip bandwidth in an active 3D interposer

Perceval Coudrain (CEA-Leti) who works on 3D integration and advanced packaging as part of the 3D Integration program, received the "Best Paper Award" at the ECTC conference (in May 2019, Las Vegas, USA) for his article titled "Active interposer technology for chiplet-based advanced 3D system architectures". "An active interposer enables the addition of smart features to the final 3D system, such as advanced network-onchip (NoC) interconnects, fast I/Os for off-chip communication, embedded power management and system-onchip (SoC) infrastructure", Coudrain said. "Our paper reported on the first successful technological integration of chiplets on a fully processed, packaged and tested active silicon interposer". The prize was officially announced in January 2020.

#### **PERCEVAL COUDRAIN & AL**

Active interposer technology for chiplet based advanced 3D system architectures

2019 IEEE 69<sup>th</sup> Electronic Components and Technology Conference (ECTC) DOI:10.1109/ECTC.2019.00092

# Image sensors require complexes architecture

Introducing his communication at 3D System Semi Summit, François Guyader (STMicroelectronics) underlines the great interest of 3D integration and partitioning for image sensors and the advantage of scalability offered by the hybrid bonding technology. Showing results obtained at CEA-Leti and STMicroelectronics, within the frame of Nanoelec, he demonstrated that parallel hybrid bonding combined with sequential stacking offer scalable solutions to reach more and more complexity in architectures.

#### FRANÇOIS GUYADER & AL

3D Integrations for Smart Image Sensors 3D System Semi Summit January 2020

IRT NANOELEC 3D INTEGRATION FOR IMAGE 31

# Releasing hpc & big data applications for 3D technology

At the ISSCC 2020 conference, (February 2020, San Francisco, USA), CEA teams reported on a high-performance processor breakthrough achieved as part of the 3D Integration program. They implemented an active interposer as a modular and energy-efficient silicon platform that enables efficient integration of large-scale chiplet-based computing systems for high-performance computing (HPC) and big-data applications.

"This is a breakthrough in terms of system-and-architecture integration, achieved all the way from the architectural design down to a silicon prototype", says Pascal Vivet (CEA-List), the lead author of the paper. "In addition, 3D technology and associated design techniques are now available for implementing large-scale computing systems, thus offering a chiplet-based 96-core computing architecture for the first time."

#### **PASCAL VIVET & AL.**

A 220GOPS 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer offering 0.6 ns/mm Latency, 3 Tb/s/mm2 Inter-Chiplet Interconnects and 156 mW/mm2 @ 82% Peak-Efficiency DC-DC Converters ISSCC

February 2020

# Through-Silicon-Via for 3D stacking

In a paper published in MRS Communication, a CEA-Leti team acting within Nanoelec, studied the combination of Cu-to-Cu direct hybrid bonding technology with Through-Silicon-Via (TSV) to allow 3D interconnection between pixels and the associated computing and memory structures, with each function being fabricated on a separate wafer. "Process developments are mature and can be reliably used in the fabrication of an electrical test vehicle including vertical interconnects associating multi-wafer stacking with a hybrid bonding process and high-density thin TSV applicable to low pitches (<5 µm)", comments Lucile Arnaud, as first author of the paper.

#### **LUCILE ARNAUD & AL.**

Three-dimensional hybrid bonding integration challenges and solutions toward multi-wafer stacking MRS Communication (Material Research Society),

September 2020

# 3D-integration technology and architecture breakthrough to power exascale computing

"Profound changes brought about by high performance computing (HPC) applications are based on continuous and exponential increases in computing performance over the past decades", explains Denis Dutoit (CEA-List) who was a guest speaker at IEDM 2020. He underlined the benefit of a cross disciplinary approach in 3D technology and architecture "It enables high-performance processors that will power exascale-level HPC, he says. State-of-the-art 3D toolbox and architecture that we developed within Nanoelec enable higher bandwidth and heterogeneity for processors."

Exascale computing refers to computing systems capable of calculating at least  $10^{1^8}$ , or one-billion-billion, floating-point operations per second, which would be twice as fast as the fastest computer available today. Efforts to develop exascale computing are driven by highly data-intensive scientific and industrial applications, such as climate research, drug discovery and material design. This level of performance in HPC and Big Data will be achieved with heterogeneous computing nodes composed of generic processor chiplets hosting accelerator chiplets for improved operational intensity.

#### **DENIS DUTOIT & AL.**

How 3D integration technologies enable advanced computer node for Exascale-level High Performance Computing IEEE IEDM

December 2020

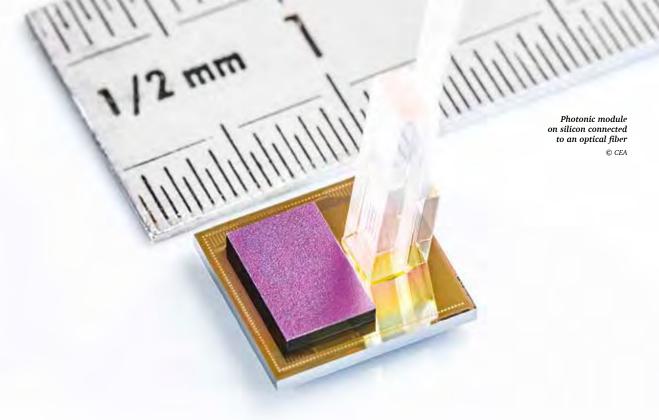

# Photonic Sensors

# Along the optical sensors procurement chain

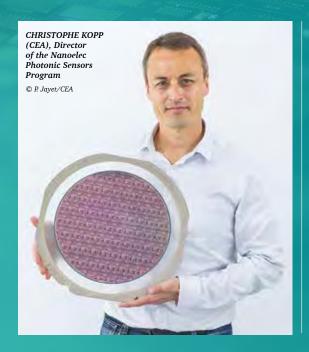

4 questions to Christophe Kopp, Head of the Nanoelec/Photonic Sensors program & Head of the Section of New Photonic Applications at CEA-Leti

What is the potential for optical sensor applications?

In functional terms, optical sensors are well-known for their accuracy, sensitivity, selectivity, versatility and acquisition speed. Thanks to micro-technology integration, their miniaturization is opening up new markets in a wide variety of fields such as environmental monitoring, urban planning, health, industry or energy, but also consumer applications. The digital transformation of our society is leading to the deployment of billions of sensors and sensor networks. They are used across a broad spectrum of applications such as gesture recognition, presence detection, smart heating, etc. The rising adoption of automation in various sectors is speeding up the growth of the market for these sensors.

The global market for optical sensor applications already stands at more than 20 billion dollars, with a target annual growth rate in excess of 10% over the coming decade [1].  $\rightarrow$

[1] Global Market Insights.

## What innovations will sensors carry in the coming years?

These new sensors must be accurate, be as small as possible and consume very little energy. Moreover, their architecture must be compatible with the means of collective manufacturing. These sensors will be based on the use of photonic chips built on production lines derived from the microelectronics sector. This technology and its industrial ecosystem were initially developed for the high speed optical datalinks market. Today, optical sensors require that the spectral bands that can be addressed be expanded from the visible to the infrared, with functionalization of the detection surfaces.

#### What technological challenges do you face?

The main technological challenges for these sensors are the accuracy and stability of measurements, miniaturization, data processing and transfer, and compatibility with the constraints of mass production. The unique properties and the performance of integrated photonics are essential in meeting these requirements. We aim at implementing thousands of functions on the same photonic chip. New components and new technological building blocks are required together with the digital tools needed to design these complex photonic circuits, along with automated characterisation techniques.

#### What are the goals of the program you are running?

Our aim is to speed up innovation and give a technological edge to our industrial partners along the optical sensors procurement chain. In the light of the expected growth mentioned earlier, we ambition to consolidate the technological lead by French players in the field so that they can be on a par with the best in the world. To achieve this, we are pursuing a three-fold goal with them: increasing the maturity of the 200- and 300-mm photonic platforms, developing innovative processes and devices (integration of laser sources in particular) and, finally, implementing application demonstrations.

# Photonic Sensors program at a glance

#### ∇ISION

New sensor opportunities based on large scale 300mm silicon photonic technologies

#### 📥 AMBITION

Enrich our photonic prototyping and industrial platforms with key building blocks enabling new sensors to address Medtech, Environment, Consumers goods, Mobility (Lidars) and Computing

####

- Miniaturize sensors

- Diversify the fields of applications

- Manage the integration of thousands of functions on the same chip

- Increase technology readiness level using CAD tools and enrich our device library including performance corners, fabrication process flow

#### 88 PARTNERS

Almae | CEA | CNRS | Siemens EDA (ex. Mentor Graphics) | STMicroelectronics

# CONTINUOUSLY IMPROVING DESIGN TOOLS FOR SILICON-BASED PHOTONICS

As a core partner of Nanoelec, Siemens EDA (ex. Mentor Graphics) is providing design & verification tools for the benefit of the Nanoelec designer community. The EDA leader also uses feedback from the community to continually improve its design tools in the context of sophisticated demonstrators and platforms. Tom Daspit, Product Marketing Manager at Siemens EDA focuses on design & verification tools for Photonics-on-Silicon applications.

# Why are design tools essential for enabling growth in photonic design?

Photonics-on-Silicon has a wide range of applications in data centers, HPC and telecommunications. The promise of leveraging high-volume, low-cost manufacturing techniques in photonics-on-silicon circuit manufacturing has the potential to extend the range of photonics applications to smart sensors targeting new areas such as autonomous vehicles, autonomous robots, healthcare and more.

Extending and leveraging current silicon design tools in order to seamlessly and productively integrate photonics functions with CMOS-based electronics is a key enabler for high-volume, high-performance photonics circuits.

## What are the main methodologies for architecture design in photonics?

Today, there are two main photonic design methodologies: scripted and custom layout. Both are good for creating small designs, but they become inefficient as the design

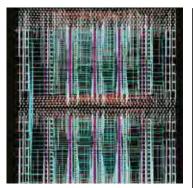

Silicon photonics switch layout based on CEA-Leti/Siemens EDA PDK

© CFA-Siemens EDA

size increases from tens, to hundreds, to over a thousand components in the design.

Photonic design can benefit from the forty-plus years of industry improvements in IC process technology, methodologies and design tools. Ultimately, the availability of more photonic processes should be able to support much larger designs.

IC design sizes have grown from thousands, to millions, to billions of transistors in today's processors. This growth was enabled by automating IC design tasks. Automation is not just tool-centric, it relies on the underlying design methodology that supports it. An example of digital place and route is LEF/DEF, a standard that abstracts the data to the minimal set that is needed. LEF/DEF is derived from a standard cell design methodology and standard cells are created from individual transistors built up from the data in a Process Design Kit (PDK).

#### What is the step forward provided by the Siemens EDA LightSuite Photonic Compiler?

Siemens EDA addresses photonics by supporting both automated and custom layout tools. We are focused on driving state of the art layout automation with our Light-Suite Photonic Compiler. Considering a 4 by 4 switch, the layout was automatically created in under 5 minutes. Now scale that switch to a 16 by 16. The complexity of such a change requires complex optical and electrical routing. This DRC clean layout is implemented in 85 minutes. Manual layout of a design of this size would take many months to implement.

IRT NANOELEC PHOTONIC SENSORS 35

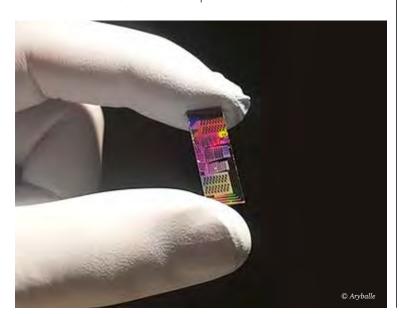

# WIDESPREAD USE OF LIDAR SYSTEMS BASED ON INTEGRATED OPTICAL PHASED ARRAYS (OPAS)

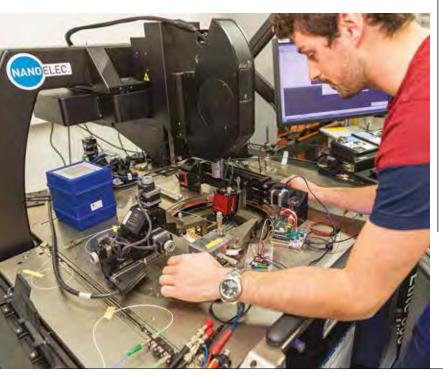

Taking a critical step towards developing Lidar systems for widespread commercial applications, teams at Nanoelec have developed generic algorithms to calibrate high-channel-count optical phased arrays (OPAs), as well as an advanced measurement setup enabling wafer-scale OPA characterisation.

OPAs are an emerging technology made of arrays of closely spaced (around 1  $\mu$ m) optical antennas which radiate coherent light in a broad angular range. The interference pattern produced can be changed by adjusting the relative phase of the light emitted by each antenna. For example, if the phase gradient between the antennas is linear, a directional beam formed. By changing the slope of the linear gradient, the direction of the beam can be controlled, which enables solid-state beam steering.

"The development of a high-performance OPA would pave the way for inexpensive Lidar systems for autonomous vehicles, holographic displays, biomedical imaging and many other applications», says Sylvain Guerber, the lead author of a paper from CEA-Leti and STMicroelectronics at the 21'Photonics West International Conference.

"This can improve performance in scanning speed, power efficiency and resolution compared to the heavy, power-hungry and expensive mechanical beam-steering systems used in current lidars. An additional feature of OPA-based lidar systems is that they have no moving parts, as solid-state beam steering is achieved simply by phase-tuning the antennas, which significantly reduces the size and cost of these systems", he adds. Lidar, which stands for light detection and ranging, has emerged as a key enabling technology for tomorrow's sensing and vision systems. In addition to automotive and medical uses, they could enable autonomous mobility for drones and robots, as well as industrial automation. Commercial Lidar systems must meet stringent requirements, especially for automotive applications. In particular, a high-power, low-divergence beam is needed to accurately resolve a scene. For example, resolving a 10-cm object at 100 m requires an OPA operating at a wavelength of 1 µm with a circuit consisting of at least 1,000 antennas, each spaced 1 µm apart. Therefore, the development of high-channelcount OPAs is necessary for a com-

Sylvain Guerber (CEA-Leti) prepares a series of tests on the new "Lidar bench" set-up installed in 2020. The white fiber is used to inject light into the circuit. The blue sensor electrically controls the phase shifters in the Lidar circuit (steering of the laser beam which exits the chip to scan the visible space, with no moving parts). In red: a camera observes and measures the steering of the beam exiting the Lidar.

mercial OPA-based Lidar system.

© P. Jayet/CEA

IRT NANOELEC PHOTONIC SENSORS 37

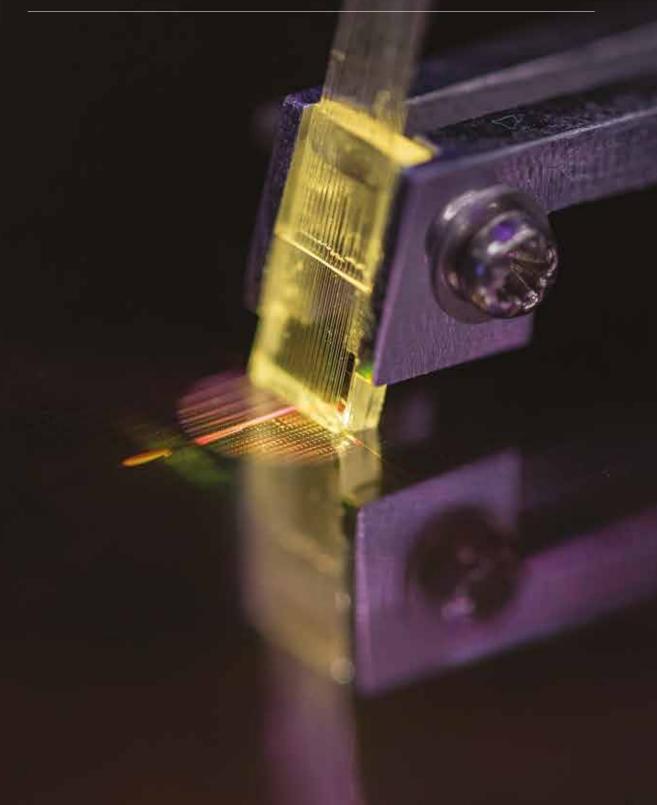

At CEA-Leti, on a Nanoelec Photonic Sensors program test bench. The bundle of measurement optical fibers is aligned to within 10 nm on the light channels integrated into the photonics circuit to be tested.

© P. Jayet/CEA

## NANOELEC AND SOITEC TO SUPPORT THE STARTUP SCINTIL PHOTONICS

Nanoelec is supporting Scintil Photonics, a startup created in 2018, with the development of III-V/Si integrated circuit demonstrators/prototypes by developing technological building blocks, such as die-to-wafer bonding, manufacturing III-V on silicon parts and supporting design and testing activities.

"Soitec, one of the partners in the Nanoelec consortium, joined our board of directors, in 2020. The company brings us its technological expertise and international market", says Sylvie Menezo, CEO and CTO of Scintil Photonics. "Also in 2020 we signed our first contract with a leading European telecom equipment supplier."

"Scintil Photonics offers integrated photonic circuit solutions for high-speed optical communications. These circuits are also very promising for 3D sensing and quantum photonics applications, allowing to

tackle dynamic growth markets, respond to new customer needs and significantly enhance our product portfolio," said Thomas Piliszczuk, executive vice president of global strategy at Soitec.

Scintil Photonics aims to develop products for the generation, modulation and photo-detection of very high speed signals (800 Gbps per wavelength) for the data networks market for storage or computing centers (Active Optical Cables, High Speed Short Reach Interconnects). This rapidly expanding market is increasingly turning to integrated

photonic solutions, owing to the rise in the transmission rates (electronic-optical integration) and the growth in volumes (the traditional technologies which required manual assembly of parts are no longer sufficient). The III-V on silicon integration developed within Nanoelec constitutes the heart of the Scintil Photonics technology: this integration allows the creation of an externally modulated laser, for which the expected performance is state-of-the-art and the process is compatible with mass production (therefore offering low costs).

IRT NANOELEC PHOTONIC SENSORS 39

## PDK MAKES PHOTONIC CIRCUIT DESIGN EASIER

An integrated Process Design Kit (PDK) has been included in the Siemens EDA (ex. Mentor Graphics) Tanner design flow and it is now opened up to Nanoelec partners.

"For manufacturing of future circuits on the CEA-Leti 310nm platform, the PDK is a real time-saver. The main target applications are datacoms, telecoms, Lidars, HPC, and neuromorphic chips", Eleonore Hardy, CEA-Leti business developper, underlines.

CEA-Leti and Siemens EDA are collaborating as core partners of the Nanoelec consortium. "The PDK provides access to a library of proven components and can also be used to design new ones. It is also fully compatible with LightSuite, another Siemens EDA tool that automates the routing of optical and electrical lines and it is also integrated as part of our know-how", adds Hardy.

IRT NANOELEC PHOTONIC SENSORS 41

#### **HIGHLIGHTS**

#### **EDUCATION & TRAINING**

Teams from the Nanoelec/ Photonic Sensors program disseminate their knowledge and know-how extensively through numerous publications and courses.

For example, in February 2020, Benoit Charbonnier (CEA) was invited to the Thales Research Center in Paris-Saclay within the context of the European Network for High Performance Integrated Microwave Photonics. He gave a short course on silicon photonics for communications and new applications. In November 2020, Quentin Wilmart (CEA) discussed Si capacitive modulator integration in a 300-mm Si photonics platform using different annealing conditions, as part of an intensive short course in silicon nitride integrated photonics by the European Silicon Photonics Alliance.

#### **HIGHLIGHTS**

In 2021, CEA-Leti acquires a rotary bench to test the performance of optical gyroscope prototypes designed and prototyped under the Nanoelec/Photonic Sensors program.

The turntable can be used for operating rotation speed measurements from 0.001 °/sec to 1,500 °/Sec with a precision of 0.005%. The aim is to eventually develop gyroscopes for mass market applications.

IRT NANOELEC 43

#### HIGHLIGHTS

# PHOTONICS FOR HEALTHCARE

On March 2021, CEA-Leti broadcast a digital workshop on emerging photonic and integration technologies for healthcare.

Bertrand Bourlon, Head of the Optical Sensors Lab at CEA-Leti, presented advances powered by Nanoelec on midinfrared sensors tackling environmental and medical challenges. "Such sensors enable higher specificity in cost-effective miniaturized sensors & systems", he underlines, calling up several fields of application like process or air-quality monitoring, cross biochemical and morphological information for health. "Other fields such as energy and defense might be also addressed by mid-IR imaging integrated photonic sensors", he adds.

## **Key publications**

# New contacts on GeSn alloys for optoelectronic devices

The semiconductor industry is constantly striving to improve various parameters in order to increase the performance and data transfer speed of optoelectronic devices: this includes changing the steps in the production processes, the device architecture or the materials that constitute the devices. In her PhD Thesis, Andrea Quintero worked on the development of contacts on GeSn alloys. "Germanium-Tin (GeSn), group-IV alloy is an interesting material for integration into electronic or opto-electronic devices and we focused on systematic and comprehensive development and characterisation of Ni/GeSn intermetallics to contact GeSn-based devices", she explains. Results were obtained at

the CEA-Leti in collaboration with C2N (Univ. Paris Saclay / CNRS), within the framework of Nanoelec. "They represent a good starting point for producing high-quality, stable and reliable GeSn-based contacts that can be fully integrated into electronic or opto-electronic devices", adds Quintero. Andrea Quintero has published ten papers on the phenomenon over the past three years, even winning a Best Paper Award at ECS Prime 2020.

#### **ANDREA QUINTERO**

Development and characterisation of contacts on GeSn alloys

University Paris-Saclay (U-Psay) thesis defended on october 16<sup>th</sup> 2020 at CEA-Leti in partnership with C2N (U-Psay & CNRS), Orsay Faculty of science and Nanoelec

## Integrating an optical source directly on a silicon chip

In order to meet the nedd for circuits with integrated optical interconnections, Marie-Léonor Touraton's PhD thesis studied the possibility of integrating an optical source directly on a silicon die. "I specifically studied the technological building blocks enabling the integration of light sources, emitting from the red region of the spectrum to the L band, by mean of selective epitaxy of various III-V materials. For various wavelength ranges, we demonstrated the integration of III-V materials stacks in the form of ridges", she says. With support from Nanoelec, a first version of electrically pumped components, like ribbon diodes, on GaAs and silicon substrates was manufactured and characterized.

#### **MARIE-LÉONOR TOURATON**

Direct epitaxy of III-V semiconductors on silicon substrate for photonic devices

Thesis defended on June 22nd 2020 at University Grenoble-Alpes (UGA) in collaboration with CEA-Leti, CNRS-LTM, STMicroelectronics and Nanoelec

# Optical switch to replace copper interconnections in ICT components

Silicon photonics look to be a promising solution for replacing copper interconnections for communication requirements that are heavily integrated inside data centers, inter and intra chip links. To achieve high data rates, one can use multiplexing on optical links combined with disaggregated resources. In such architectures, an optical switch being able to cope with high size and data rate is a core element to be designed. During his PhD, Nicolas Michit focused on intrachip interconnections on a photonic interposer, based on wavelength multiplexed links around the 1310-nm communication channel. "We were interested in optical switching, Michit says. At first, the decision to use ring resonators based links was justified in terms of compactness, network flexibility and low optical losses. These structures are however very sensitive to the environment and to geometry fluctuations: it is important to understand clearly the physical effects involved. We described different ring resonance models to create a model that is both analytical and accurate enough to describe the peak shifts observed experimentally. This work gave us a better understanding of the ring parameters in order to minimize its impact on a wavelength-division multiplexing (WDM) link."

#### **NICOLAS MICHIT**

Optical switch for the design of fast wavelength-division multiplexing (WDM) links in silicon photonics

Thesis defended at Lyon University in collaboration with Insa-Lyon, INL, STMicroelectronics (CIFRE contract) and Nanoelec

#### A CMOS-compatible laser

For her PhD, Flore Boyer worked on optimizing performance of optoelectronic circuits for high-density data transmission. An innovative integration scheme has been developed in collaboration with STMicroelectronics and CEA-Leti. It consists in the full integration of the III-V emitter, which is a III-V/Si hybrid laser, on a silicon wafer in a 300 mm CMOS-compatible clean room. "We focused on the components required for such integration, in particular CMOS-compatible contact layers of the laser, necessary for the generation and amplification of the optical signal, Boyer reports. We then demonstrated promising and reliable metallization for the full integration of III-V/Si hybrid laser onto a 300-mm Si fab-line."

#### **FLORE BOYER**

Integration of CMOS-compatible contacts on III-V materials for photonic devices on silicon using the 300-mm platform

Thesis defended at Université Grenoble-Alpes in collaboration with CEA-Leti, STMicroelectronics and Nanoelec

#### Best Paper award

Andrea Quintero received a Best Paper Award at ECS Prime 2020 for her comprehensive study of the impact of Sn content on the Ni/GeSn phase sequence. "We performed morphological and electrical properties characterisation during the solid-state reaction", reports Quintero. "Sn segregation around grain boundaries hampers atom diffusion, delaying the growth of the Ni(GeSn) phase. In addition, we observed a correlation between the Sn content and degradation of the morphological and electrical properties. This prize rewards Andrea's amazing efforts and work during the 3 years of her PhD Thesis", underlines Philippe Rodriguez, Head of the Advanced Materials Deposition Laboratory at CEA-Leti.

#### ANDREA QUINTERO & AL.

Analysis of Sn Behavior During Ni/GeSn Solid-State Reaction by Correlated X-ray Diffraction, Atomic Force Microscopy, and Ex-situ/In-situ Transmission Electron Microscopy

ECS Prime October 2020

IRT NANOELEC PHOTONIC SENSORS 45

# CMOS-compatible contact technology on III–V materials

S. Bensalem et al. recently published their "study of the Ti/InGaAs solid-state reactions: Phase formation sequence and diffusion schemes" in Materials Science in Semiconductor Processing. The development of CMOS-compatible contact technology on III-V materials based on Ti for electronics or photonics applications has been carried out at Nanoelec by scientists from CEA-Leti, STMicroelectronics and the Hungarian Academy of Science Center for Energy Research. "We studied solid-state reactions between Ti thin films (20 nm) and InGaAs layers grown on InP substrates from the as-deposited state up to 550°C using a combination of advanced X-ray diffraction (in-plane reciprocal space mapping), Auger electron spectroscopy and transmission electron microscopy analyses" underlines Philippe Rodriguez, as corresponding author for this paper. "The complete knowledge of the phases present and their spatial localization is essential in order to understand and tailor the electrical properties of the Ti-based contacts on InGaAs. It is also important to anticipate and control the impact of the integration scheme in terms of additional thermal budget for instance."

#### **SALMA BENSALEM & AL.**

Study of the Ti/InGaAs solid-state reactions: Phase formation sequence and diffusion schemes

Materials Science in Semiconductor Processing

# Electro-refractive modulators to reduce energy needs

Silicon photonic modulators are a key component for electro-optic transmitters in data centers. Electro-refractive modulators relying on free carrier plasma dispersion in a Mach-Zehnder interferometer have become the most popular solution. Accumulation—based capacitive modulators are an efficient approach, which can reduce modulation power consumption. Preparing his PhD thesis with the support of core partners of Nanoelec (CEA-Leti, CNRS & STMicroelectronics), Ismael Charlet studied the behavior of capacitive modulators with polycrystalline silicon to form the capacitance. "The modulators are made within the

standard fabrication flow with only a few add-ons. We demonstrated that furnace annealing conditions and excimer laser annealing conditions during polycrystalline silicon formation enhance the modulator bandwidths", he says. The results were reported at the 21'Photonics West International Conference.

#### **ISMAEL CHARLET & AL.**

(CEA-Leti & CNRS & STMicroelectronics, Univ. Grenoble-Alpes, Univ. Paris-Saclay) Si capacitive modulator integration in a 300-mm silicon photonics platform using different annealing conditions

SPIE Opto/ Photonics West 2021 DOI: 10.1117/12.2577806

# Designing a photonic process flow for hybrid lasers

Ar and He plasma might be used to pre-clean InP prior to nickel contact deposition. The integration of III-V/ Si hybrid lasers on a 300-mm platform for photonic applications requires the development of dedicated CMOS-compatible contacts, for which those based on nickel are very good candidates. A team from STMicroelectronics, CEA-Leti and Grenoble-INP, working together on this subject within Nanoelec, compared the impact of in situ pre-clean based on argon (Ar) or helium (He) plasma on the surface integrity of InP prior to nickel (Ni) contact deposition. The results were presented in the Journal of Vacuum Science & Technology B. "We observed that Ar pre-clean significantly damages the InP surface by generating high roughness and creating indium (In) dots on the top surface", Flore Boyer, as main author, says. "However, helium pre-clean seems to induce less damage and no indium dots. We suggest that the difference in electrical behavior obtained between Ar and He pre-cleaned Ni/n-InP contacts is due to differences in the surface state and morphology."

#### FLORE BOYER & AL.

Integration of the Ni/InP system on a 300-mm platform for III-V/Si hybrid lasers

Journal of Vacuum Science & Technology B DOI: 10.1116/1.5128554

# Digital Trust (Pulse)

## **Context and outlook**

With the advent of the Internet of Things (IoT), new services based on data management are multiplying. The increase in the number of cyber-attacks is raising awareness among the public and institutions of the risks associated with a toot rapid and poorly controlled digital transition.

New vulnerabilities are being identified and revealed to the general public at a time when medical devices, automobiles, industrial and urban equipment are becoming increasingly connected and autonomous. These vulnerabilities and the attacks that exploit them are undermining the trust of the users in connected services and goods. Consequently, these attacks have an impact not only on the image of the companies, but also on the society's economy. They even sometimes compromise the legal and social liability of the public or private players who have inadequately protected their products.

However, when designing digital products, cybersecurity is often seen as a constraint which should not weigh too heavily on the primary function (health care, mobility, manufacturing, etc.), whether in terms of cost, performance, or ergonomics.

The challenge of the Nanoelec/Pulse program is thus to identify how electronic technologies can participate

in the emergence of new products and services capable of increasing operating safety, protect the confidentiality, authenticity and integrity of digital data, guarantee protection of privacy, while simplifying the deployment of cybersecurity strategies. Our work focuses on three application areas: the security of industrial systems, that of robots and self-driving vehicles, and the Silver economy.

In its own way, the Pulse program aims to help meet the vital need from institutions, solutions suppliers and users, to live in a trusted digital world.

# **Pulse** at a glance

Due to the rise in cybercrime, cybersecurity of the Internet of things (IoT) is a major challenge for digital trust. Strengthening and hardening critical embedded, increasingly interconnected and smarter systems is now vital.

#### AMBITION

New smart and intrinsically secure nanocomponents to reinforce systems resistance against future cyberattacks + Improved security of smart embedded systems throughout their life cycle (including AI algorithms) + Safer deployment environment through digital ID, data sovereignty and secure interactions between smart systems.

#### & MISSION

Develop and test new security features for components and systems in three fields of application: Industry 4.0, Homecare and Robotics.

#### 8'8 PARTNERS

Akeoplus | CEA | Grenoble-INP | Inria | Schneider Electric | STMicroelectronics | UGA

## HOMECARE CYBERSECURITY

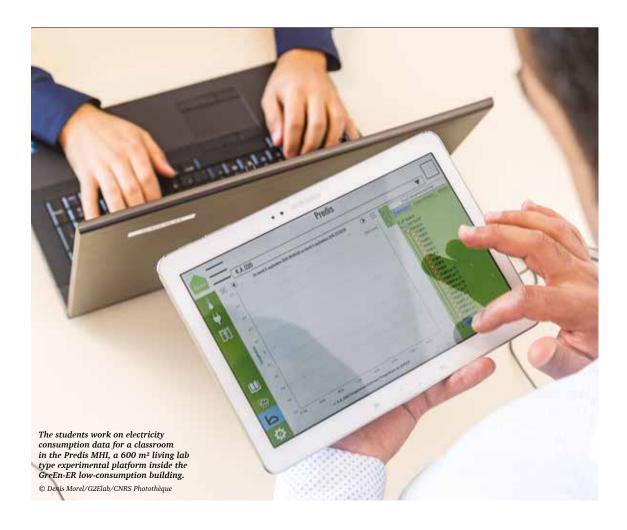

# Accurate occupancy data for smart building management

In November 2020, STMicroelectronics, Schneider Electric and Lynred presented the first integration of Edge AI in a high-performance people-counting sensor developed within Nanoelec.

While monitoring occupancy in large spaces with multiple entrances and exits is a significant challenge in any closed environment, it potentially offers significant value for hotels, offices, retail businesses and building managers. Three core partners of Nanoelec – STMicroelectronics, Schneider Electric, and Lynred – recently demonstrated a prototype of a high-performance people-counting sensor that overcomes the related challenges. This sensor provi-

des the opportunity to use the data to optimize room occupancy, anticipate energy consumption, reduce waiting and queuing time, manage social distancing more efficiently, and more.

Since 2015, the Nanoelec/Pulse program partners have been working on attendance monitoring in public areas using digital devices. The 2020 demonstrator is the first device developed with Artificial Intelligence (AI) at the Edge. In the Nanoelec collaborative environment. STMicroelectronics, Schneider Electric and Lynred, with scientific and technological input from CEA, Inria and UGA, achieved a strong mix of hardware and software options coping with cybersecurity, reliability, and energy specifications. At the same time, Pulse/Nanoelec provided the technological platform to set up and test the different configurations of devices and algorithms to explore a range of suitable innovative solutions.

#### Open Innovation for smart cities and smart mobility

The startup Kentyou partnered with the Nanoelec/Pulse program to enhance its own development to provide a strong capacity to connect sensors, merge and mine data for smart cities.

"Given that sensor technologies are now affordable and widespread, city and building operators have to cope with the problem of extracting intelligent information from the deluge of data. They encounter difficulties with connecting sensors and merging data", explains Levent Gürgen. Levent Gürgen was a researcher at CEA and president of the Urban Technology Alliance (UTA)<sup>[1]</sup> before creating his own startup, Kentyou, in April 2020. "Kentyou helps ci-

ties and innovators exploit digital technologies and build smarter and more sustainable urban environments", adds Levent. Last year, the company partnered with the Nanoelec/Pulse program to enhance its own development to offer its customers the ability to connect sensors, and merge and mine data.