# Scientific & Technical highlights

2023 EDITION

### P. 4 IDENTITY OF THE INSTITUT

Exploring the future of electronics

### P. 6 FOREWORDS

P. 6 A new funding phase for the instituteP. 8 Grenoble joins the mega-fabs

P. 10 POWERGAN SYMPOSIUM

### P. 12 HIGHLIGHTS

### IMAGES & PHOTONS

P. 19 FROM 3D INTEGRATION TO IMAGES

### SMART IMAGER

**P. 20** From imaging to visioning

### Technology, architecture & applications

P. 22 Transforming digital vision with cutting-edge 3D-stack camera sensors, global shutter and iToF

**P. 24** The physical limits of resolution

**P. 25** Dynamic response and frugality of event-based image sensors

### Test chips & performance assessment

**P. 26** First demonstration of 2-layers test vehicle

### **Design & design tools**

P. 27 Optimizing the architecture of the future 3-layer sensor

P. 28 Heterogeneous Packaging Design and Verification Workflows

P. 29 Building a worldwide overview of 3D integration

### **Silicon Technology**

P. 30 Towards reliable hybrid bonds for 3D stacked IC

P. 31 Characterizing connectors

### DISPLED

**P. 32** Towards Display Technology Leadership in Europe

### Building the smart pixels

P. 34 Aledia's first nanowire LED platform is now reaching promising performance levels

P. 35 First results on Smart-Pixel Life Cycle Analysis

P. 36 An unprecedented eco-innovation method applicable as of the R&D phases

### Mass transfer of smart pixels

P. 37 Next-generation

3D semiconductor packaging

P. 37 Full-wafer laser

debonding of dies

P. 38 Picking of dies

as small as 75µm

P. 40 Proof of concept for fabrication of CMOS-driven

MicroLED displays

### **Building the factory scale**

P. 41 Production building almost completedP. 43 Microled receives an award

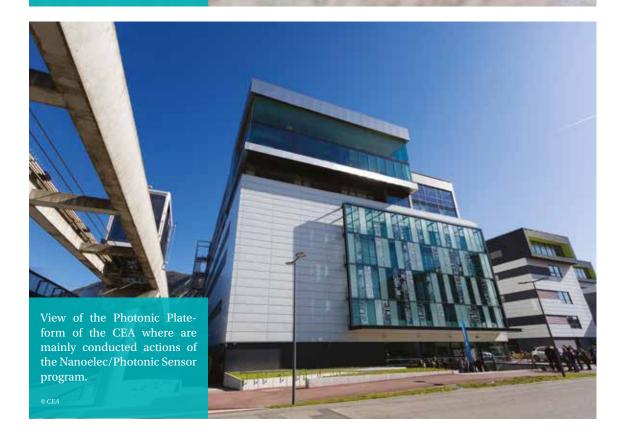

### PHOTONIC SENSORS

**P. 44** Innovative building blocks to address high volume markets

### **Photonic applications**

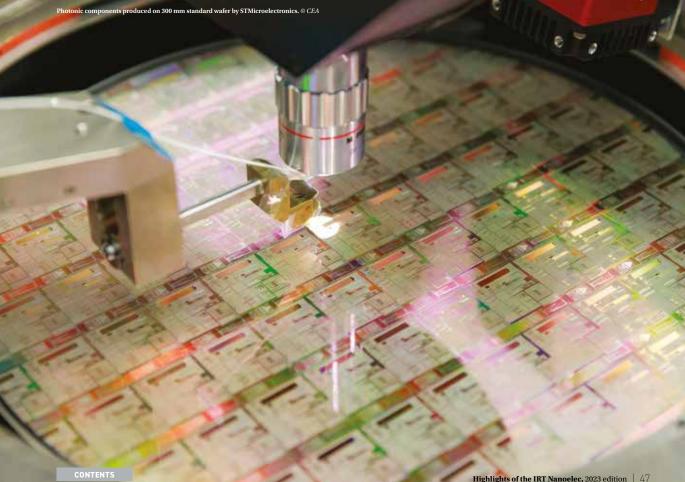

P. 46 Industry standard manufacturing of Lidars

P. 48 An Optical Phased Array demonstrates high angular resolution at 1550nm

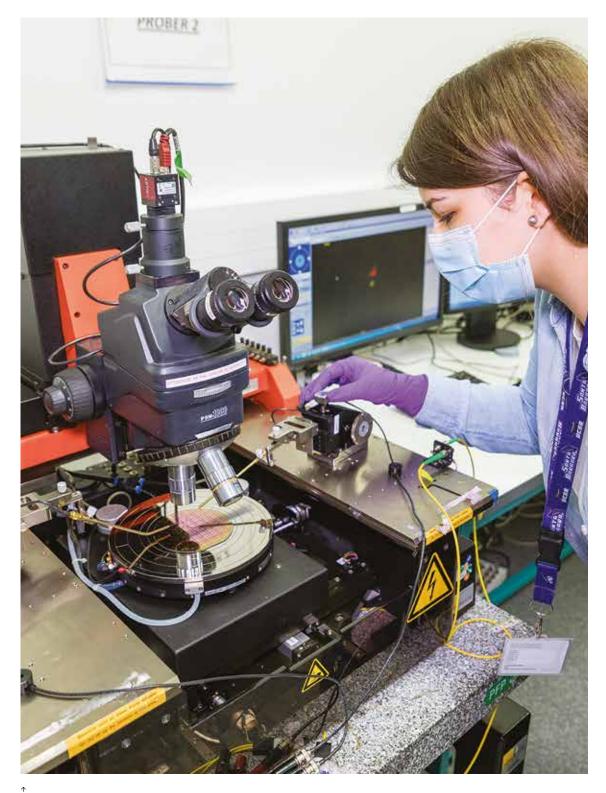

### Circuit design and testing development tools

P. 49 Process Design Kit for C-Band components

P. 50 Characterizing an OPA

### Photonic device integration

P. 52 Industrial standard red

LEDs were produced

P. 55 Capacitive modulators

for Lidars

**P. 57** Driving the computing architectures of the future

### DIGITAL TRUST

### PULSE

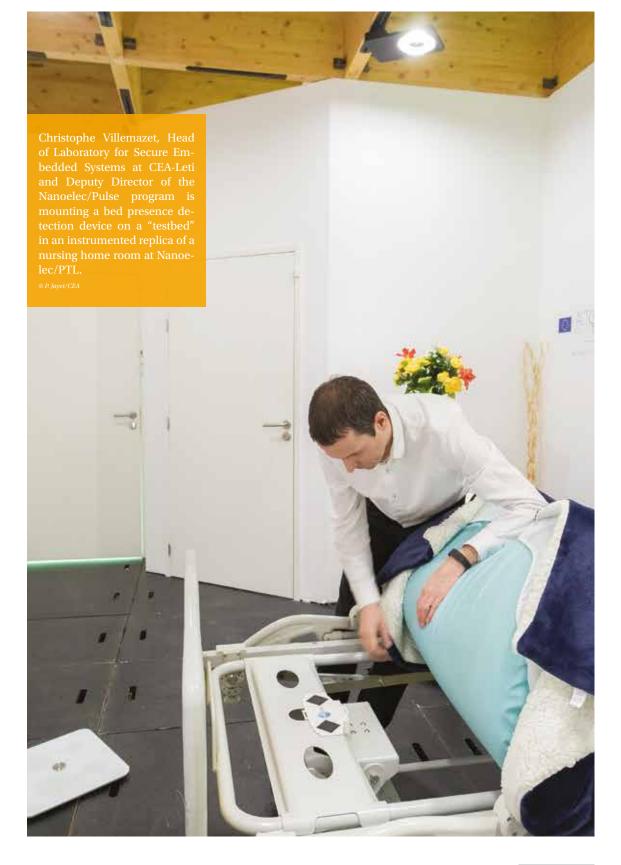

### **P. 58** Interconnected and smarter systems are now vital

### Home & health cybersecurity

P. 60 Reliable connected medical devices

P. 62 Tools and technologies for trusted components

P. 63 Protecting process isolation in multi-task components

P. 65 Protecting memory hierarchy against auxiliary-channel attacks

P. 65 2023 RISC-V Summit Europe

P. 67 RISC-V week in 2022

### Cybersecurity of industrial systems

P. 68 Ultra-secure device for critical IoT

P. 68 Detect and prevent malware attacks that target hardware vulnerabilities in IoT/ IIoT devices

P. 69 Improving cybersecurity of a critical infrastructure P. 70 Towards a global standard for internet coefidantiality

dard for internet confidentiality and embedded systems

### **Industrial robotics**

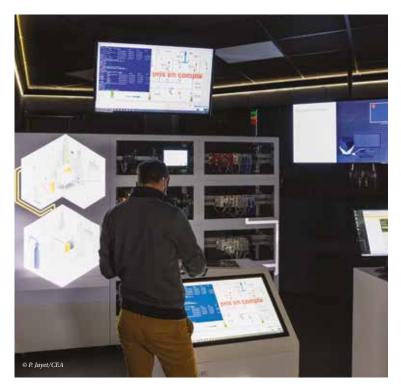

P. 72 Digital identity

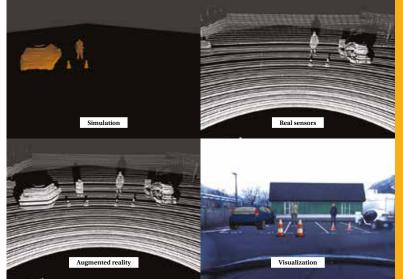

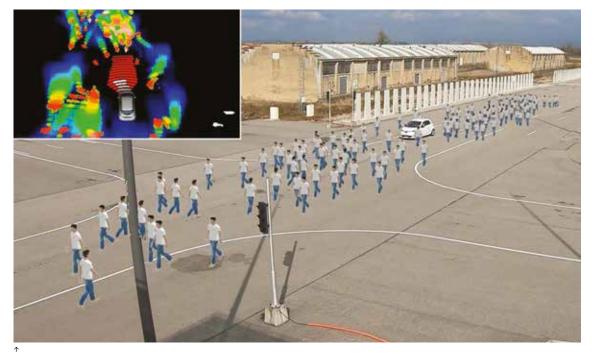

P. 74 Validating automotive software with augmented reality

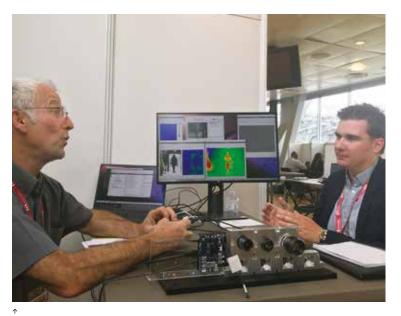

P. 76 Developing the senses of self-driving cars

P. 77 Nanoelec, System X and mobility partners

P. 78 Digitalizing products and services for SMEs

### **Events**

- P. 80 Cybersecurity

Awareness Week

P. 81 European Cyber Week

P. 81 International

Cybersecurity Forum

- Cyber security For uni

### CHARAC-TERIZATION

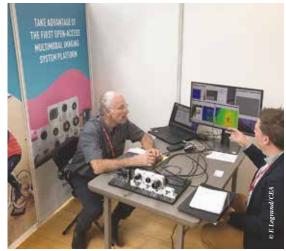

**P. 82** Easy access to large scale instruments for characterization

P. 84 Characterization becomes correlative

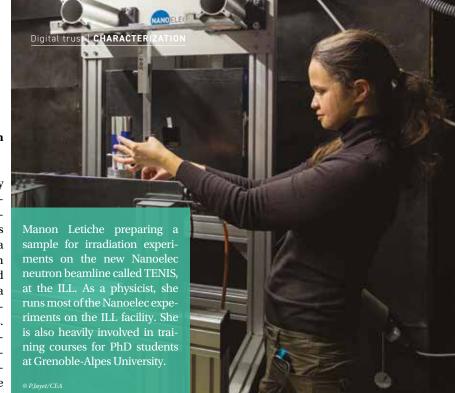

P. 85 Thermal and Epi-thermal Neutron Irradiation Station

### Platform for advanced Characterization | PAC-G

P. 87 A gateway to large-scale instruments dedicated to electronics industry needs

P. 88 Carac 2022 P. 88 2022: a neutron-free year for ILL

### Irradiation

P. 89 Radiation Facilities and Testing of Semiconductor Devices and Systems for Industry

P. 89 Radiation and its effects on components and systems

P. 93 Irradiation: inducing single events in the components

P.94 Effects of Thermal Neutron Radiation on a Hardware-Implemented Machine Learning Algorithm

**Training design**

P. 95 VR + AI visit for education

### TECHNOLOGY DISSEMINATION

**P. 96** Promoting the adoption of emerging technologies in new application fields

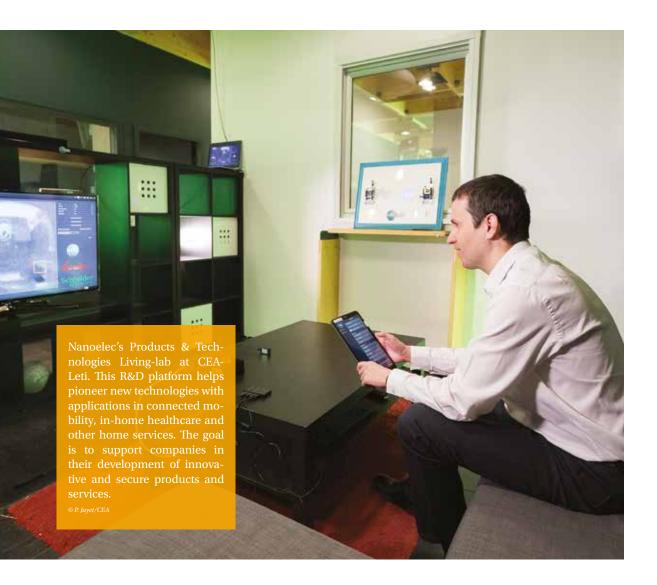

System Lab P. 98 It is time for new usages of imaging

P. 99 Innovating in imaging usage

### Easytech

P. 102 Growing success with SMEs, mid-caps and start-ups

P. 103 Pocket lab to detect pathogenic bacteria

P. 104 Detecting abnormal heating

P. 104 Towards a sovereign European processor

### HUMAN CAPITAL & TRAINING DESIGN

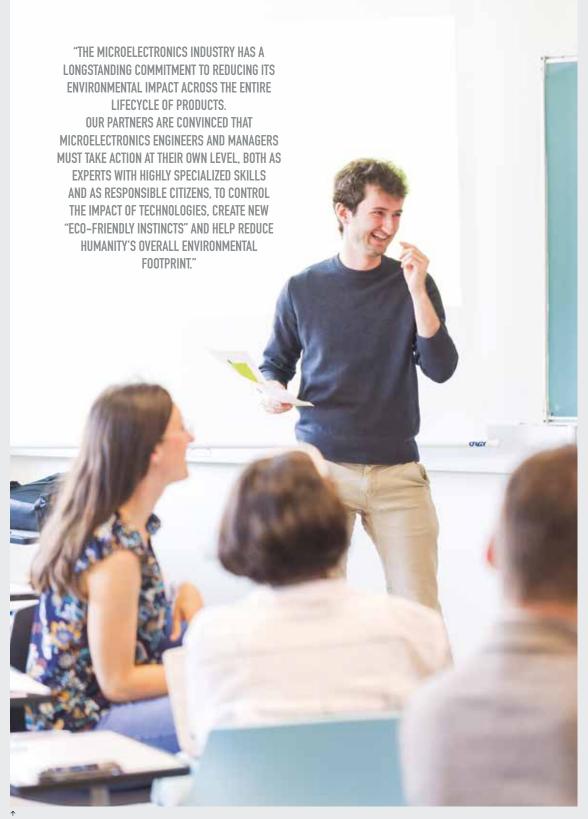

**P. 106** Sustainable development as a driver of innovation

Capsules for fundamental skills P. 108 Mission in a cleanroom

**P. 110** From early adopters of the technology to major markets

The experiential learning program P. 111 Agent of Better Cyberlife P. 112 Engineers for sustainable solutions Learning community to tackle challenges of responsible microelectronics P. 113 Experimenters of Sustainable Technology and Innovation Management P. 115 Anticipating the rollout of digital product passports P. 117 Sustainable electronics for smart buildings

### SUSTAINABLE DEVELOPMENT

### **P. 120** For sustainable competitiveness in the electronics industry

P. 121 Four work areas for sustainable development

P. 122 Running R&D projects

and eco-innovation

P. 123 Management, skills and governance

P. 124 HR, diversity, inclusion, workplace parity and equality

P. 125 Training in EngineeringP. 125 Attractiveness of the

microelectronics industry P. 127 Thirteen inspiring women in technological research

### P. 130 EMBEDDED ARTIFICIAL INTELLIGENCE

P. 132 11 PROJECTS IN EU

### P. 136 GOVERNANCE

P. 138 SCIENTIFIC COUNCIL

# Exploring the of electronics

IRT Nanoelec runs multi-partner programs to make the electronics industry more competitive and greener, and thus contribute to the sustainable development of society.

The Nanoelec technological research institute (IRT) is a consortium of private and public sector players, backed by CEA. Our mission is to help companies create value and enable their products to stand out on the digital transition stage.

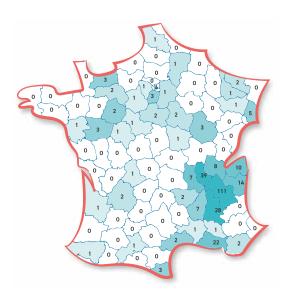

Nanoelec contributes to the competitiveness of the electronics industry, particularly in France. Based in Grenoble, the institute is a world-class hub for research, innovation and production in its field.

Our R&D programs are built jointly by representatives from the academic and industrial worlds. They deal with the design and development of new processes, systems and components in the following fields:

- photons & imaging: photonic sensors, new-generation displays and smart image sensors,

- digital trust: cybersecurity for connected objects, and characterization and irradiation of components and systems by means of large instruments.

Nanoelec also runs training design and technological dissemination programs for SMEs with the support of the Auvergne Rhone-Alpes region and local authorities. We implement open innovation techniques as well as more conventional technological development methods. Given the pervasive nature of digital technologies, Nanoelec is in contact with actors from all sectors ranging from goods to services, industry, infrastructures, and consumer products, as well as transportation, environment and health.

Nanoelec is a member of FIT, a hub of technological research institutes (IRTs) and energy transition institutes (ITEs) set up by the French Government and financed by the Investments for the Future program (PIA). The network of institutes was created to pool academic and industrial players who could run collaborative R&D and innovation projects aimed at boosting the competitiveness of the French economy.

# future

# Anticipating future human and technological needs

### MICROELECTRONICS INNOVATION

- → Carry out world-class collaborative R&D to enable innovative components and embedded systems: image & photons, and digital trust

- → Develop and transfer these technologies to enable the electronic circuits of the future

- → Give industry players access to development, prototyping and advanced characterization and education & training resources

### TECHNOLOGY DISSEMINATION

- → Help businesses in the field of information and communication technologies meet the challenges of IoT through digital trust and security

- → Provide expertise to help SMEs from various industrial sectors build new products and services with innovative components and embedded software

- → Promote cooperation between SMEs, mid-caps and large companies

- → Focus on collaborative innovation to unveil new applications comprising environmental and social impact assessments

### "ANTICIPATING FUTURE HUMAN AND TECHNICAL NEEDS IN ELECTRONICS."

### DEVELOPMENT OF HUMAN CAPITAL

- → Attract young people to jobs in electronics that contribute to sustainable development

- → Work with partners on parity and workplace equality

- → Design training courses to meet current needs

- → Anticipate future skill requirements in the sector: attractiveness for HR, sustainability, cross-skills, social and sustainable communities for innovation

TOGETHER TO CARRY OUT RESPONSIBLE RESEARCH AND DEVELOPMENT PROGRAMS TO HELP BUSINESSES CREATE VALUE."

**"WORKING**

A consortium of 22 PUBLIC & PRIVATE members as of Dec. 2022 235 A consortium of 53 M€ yearly average 2015-2022 53 M€ 229 SMEs since 2012

**0 7** scientific or technical publications & communications *since 2015*  235 patents & 53 software filed since 2012

**223** full-time jobs yearly average 2015-2022

# A new funding phase for the institute

**BY HUGHES METRAS** Director of Technological Research Institute IRT Nanoelec

n 2022, Nanoelec celebrated its 10th anniversary. Our 22-partner consortium, made up of trusted, like-minded professionals, is contributing to the competitiveness of the microelectronics industry. The wide-ranging group of complementary players is currently focused on application oriented programs: smart image sensors new generations of microled displays; silicon photonic sensors; trust and digital security for embedded systems. We also carry out programs on educational engineering and technological dissemination.

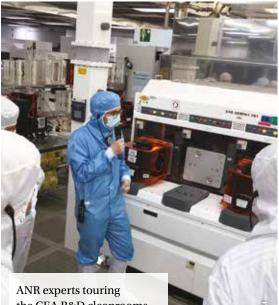

As part of our institute's evaluation in 2022, the French National Research Agency (ANR) conducted an impact analysis, which revealed business value creation in all our technological programs, through either investments or the launch of new products. The evaluators took note of the strong commitment of all Nanoelec's partners since the institute was created; they confirmed our high level of excellence

This excellence prompted the government to confirm a new funding phase for the institute until 2025. I wish to commend program teams and directors for the quality of their research.

The following report includes many highlights pertaining to scientific production and to our partners' technological results. I will mention a few for the purpose of illustration: Nanoelec's research in postquantum cryptography has gained significant international visibility as the result of our publications in the framework of the NIST (US) initiatives in the field; actively involved in our Displed program, Aledia is completing its production plant near Grenoble; and, as part of our Photonic Sensors program, startup Scintil Photonics has raised 15 million euros.

For the past 10 years<sup>1</sup>, Nanoelec has conducted research projects with more than 300 partners, and has tackled technological challenges in multilateral collaborations, a distinctive approach compared with more common bilateral agreements between an R&D organization and an industrial entity.

Since 2020, we have strived to apply a sustainable development approach in our activities. Not only do we integrate eco-design and life cycle analyses in R&D phases, we also focus on initiatives that promote gender parity, and ensure the attractiveness of the microelectronics industry. Our 2022 contest, Women in Technological Research, helped to shed light on highly accomplished female scientists, as well as women who contribute to innovation in their daily work through other professions such as management, communication, and project management. Their commitment contributes significantly to employer attractiveness, which is vital to ensure a sustainable microelectronics industry.

Hughes Metras, Director, and Sandrine Maubert, Deputy-Director of the institute, at the 2022 general assembly of Nanoelec and the celebration of its 10<sup>th</sup> anniversary. © *Cédrine Tresca/CEA*

Particularly as a result of Minalogic's active involvement in the Easytech initiative. "THE ANR EVALUATORS TOOK NOTE OF THE STRONG COMMITMENT OF ALL NANOELEC'S PARTNERS SINCE 2012."

A Hughes Metras, Director of IRT Nanoelec

# Grenoble joins the mega-fabs

"SOCIETY HAS BEGUN TO REALIZE THE CHALLENGES OF CLIMATE CHANGE AND ENERGY TRANSITION; THE SEMICONDUCTOR INDUSTRY IS ADAPTING."

Sébastien Dauvé, Director of CEA-Leti ar President of Nanoelec Steering Committee © *C. Tresca/CEA*  **BY SÉBASTIEN DAUVÉ,** President of Nanoelec Steering Committee

he global market for electronic components currently tops 500 billion dollars<sup>1</sup>; it is expected to double by 2030. The Covid crisis has also demonstrated the essential role played by components in modern economies.

### Hardware supports transitions

Electronic chips are a key enablers of the digital transition across all industry fields: growth is driven primarily by the acceleration of digitalization in consumer, healthcare and industrial sectors, the advent of artificial intelligence, and of course, the automotive industry.

Electronic chips are also vital for the energy transition and its related electrification requirements across the globe. As an illustration, we can mention the industrial transfer based on research conducted as part of the Nanoelec/PowerGaN program. STMicroelectronics has deployed a pilot line for the production of conversion components in Tours, France.

### Significant events in the past three years

Despite its vitality, the electronics market is affected by major events,

as is the rest of society. With regards to supply chains, companies have shifted from a 'just in time' to a 'just in case' strategy. In addition, automobile manufacturers have teamed up with leaders in digital technology.

Society has begun to realize the challenges of climate change and energy transition; the semiconductor industry is adapting<sup>2</sup>: frugal energy use, environmental and societal responsibility. Finally, geopolitical shifts prompt numerous questions regarding sovereignty. As far as we are concerned, how shall we maintain an industrial expertise and how will we succeed in relocatingproduction sites for electronic components.

### A territorial ecosystem and a value chain approach

Two highly significant announcements will have a strong impact on our R&D and innovation activities within the Grenoble ecosystem and beyond. *The European Chip Act* provides a means for us to increase R&D collaborations at a European scale in order to reduce supply chain shortages and tensions, strengthen design and manufacturing capacities, and, in the long term, maintain our industry's competitive edge. The European-wide goal is to reach 20% of the global production of chips.

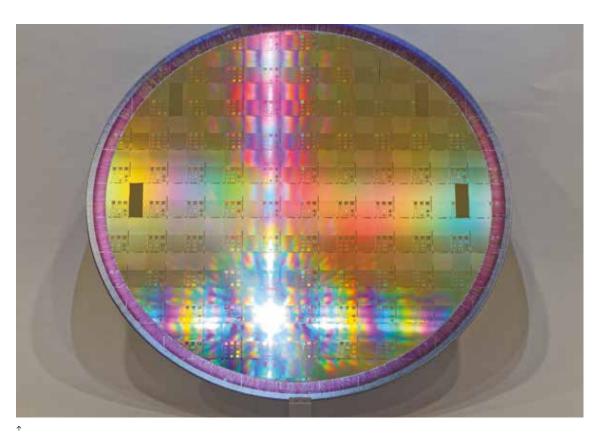

In France, as a result of the electronics-oriented agenda of the France 2030 plan, Crolles, in the Grenoble area will join the selective club of mega-fabs with a capacity of more than a million wafers per year<sup>3</sup>.

### **Tenth anniversary**

For the past 10 years, Nanoelec has successfully tackled some of the key challenges of the microelectronics industry by relying on the complementarity of stakeholders in its ecosystem, and on its value chain approach. Every year, more than 200 women and men — technicians, engineers, researchers and support personnel — are involved in Nanoelec programs with a focus on heterogeneous integration technologies and embedded systems. We are commited to provide them with bold and attractive projects!

> In 2020, 1,000 billion microchips were manufactured across the globe; Europe produced merely 10%.

- The Semiconductor Climate Consortium is focused on the challenges of climate change and works to speed industry value chain efforts to reduce greenhouse gas emissions in member company operations and in other sectors of our value chain. https://www.semi.org/en/ industry-groups/semiconductor-climate-consortium

- 3. In July 12, 2022, the French government introduced a major plan to support the electronics industry. As part of the France 2030 investment plan, and endowed with 5 billion euros, the plan will enable the creation of 5,700 direct jobs. https://www.entreprises.gouv.fr/ fr/actualites/france-2030/france-2030-presentation-de-la-strategiepour-l-electronique

# **POWERGAN SYMPOSIUM**

In March 2022, to conclude the Nanoelec/PowerGaN program, close to 200 experts from both industry and academia got together in Paris (in person and online) at a symposium organized with IRT Saint Exupéry and ITE Vedecom. Numerous industrial players from the power component application sectors were represented. STMicroelectronics presented its industrial and commercial roadmap for the coming years.

Τ2

PC2

PCI

**T4**

MP2

PGM1

**T**3

# Highlights

### **JANUARY 22**

### Sustainable electronics for smart buildings

An immersive two-day workshop for students from business and engineering schools, and industrial experts, organized by the Nanoelec/Human Capital & Training Design program.

### **FEBRUARY 22**

### **Equality & parity**

Nanoelec became member of two associations: Parity for Science in Grenoble and Women Engineers.

### Artificial intelligence

*February 12* | Crossprogram workshop on artificial intelligence, with the participation of Minalogic competitiveness cluster and IRT SystemX.

### MARCH 22

### Women in Engineering

March 8 | Nanoelec launched the "2022 Nanoelec award for women in technological research" to mark the institute's 10<sup>th</sup> anniversary. As part of International Women's Day, Nanoelec conducted a public webinar: "Jobs in Engineering" with association Women Engineers.

### **Education & training**

*March 10* | Webinar that provided an overview of the Nanoelec partner Captronic's training offer.

### **Design and architecture**

March 13 | At the international DATE conference, Nanoelec broadcasted an online one-day event including a plenary keynote, guest speakers, and regular presentations from CEA, Qualcomm, Georgia Tech, Stanford University, ETHZ (Switzerland), Fraunhofer Institute, University of Seville, Prophesee, STMicroelectronics, NTU (Singapore), Boston University, University of Manchester, Stony Brook University, Notre Dame University, META Group (Facebook), Siemens EDA, Intel.

Prix NANOELEC pour les femmes dans la recherche technologique

$\downarrow$

Highlights

### PowerGan

March 15 | National symposium for the conclusion of Nanoelec/PowerGaN, which focuses on electrical power conversion with GaN Material, by Nanoelec, ITE Vedecom & IRT Saint Exupéry.

$\wedge$

### APRIL 22

### System Lab for smart building

*April 5* | At the Campus Numérique in Lyon, session for SMEs, ETIs and innovative startups in the Auvergne Rhône-Alpes region: presentation of System Lab, an open platform for exploring new scenarios for using multispectral optical sensors.

*April 28* | Regional workshop System Lab in Gardanne (Bouches du Rhône) with Captronic.

### MAY 2022

### Open hardware

*May 3* | Annual Risc-V week in Paris, with Nanoelec.

### **Effects of radiation**

May 4 | Grad[Next], a workshop on radiation facilities and testing of semiconductor devices & industry systems, was organized by Nanoelec, Cern, ILL, ESRF, Iroc Technology, CNRS/ LPSC, Radsag & Radecs. France strives to improve next generations of displays *May* 6 | The Nanoelec/ Displed program was presented in a public conference by CEA and Aledia experts.

*May 17* | System Lab booth at Global Industrie (Paris) with Captronic.

*May 31* | Nanoelec/ Technological Diffusion: System Lab + Easytech presented on a booth at Minalogic Business Meeting (Grenoble).

$\downarrow$

### **JUNE 22**

### System Lab

*June 2* | System Lab presented at the regional technological transfer platform in Bordeaux.

### Responsibility & social impact

June 9 | Business webinar: CEA Community on the Societal Impact of Technologies by Michel Ida (CEA).

### Gender quest

*June 16* | Webinar open to all: La science taille XX elles, with association Parity in Science.

### Leti Innovation Days

June 21-23 | Forum Area event: Leti Innovation Days in Grenoble with more than 25 mini-conferences for companies.

June 23 | Nanoelec contest Women in Technological Research: nominee presentations before the jury panel and the public. Organized in the frame of the International Days for Women in Engineering. →

© Vincent Moncorgé Photothèque CNRS Association Femmes & Sciences

### JULY 22

Parity in science "Science taille XX Elles" exhibition presented by Nanoelec at CEA-Leti.

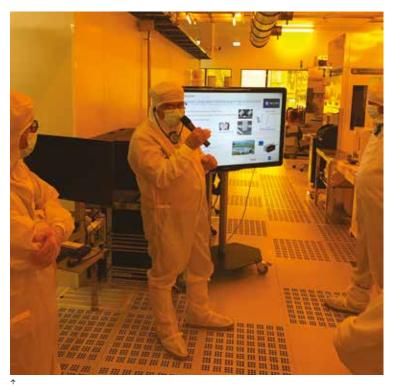

ANR experts touring the CEA R&D cleanrooms during Nanoelec evaluation 2022.

### AUGUST

Outdoor photo & video campaign for Nanoelec awards for women in technological research.

### **Green Electronics**

August 28 | Nanoelec: partner of SICT Doctoral School on Sustainable Electronics, with UGA.

### SEPTEMBER

### **EU Digitalization**

September 12-13 | Horizon Europe EARASHI (Embodied AI/ Robotics Applications for a Safe, Human-oriented Industry): project launch with Nanoelec/Pulse.

$\rightarrow$

### Industry attractiveness September 23

Webinar open to all: "Talking about your job with youngsters" with association Women Engineers.

$\downarrow$

### System Lab

September 6 & 9

System Lab presented at the Colloque Francophone de Traitement du Signal et des Images @ Nancy.

### September 6 & 7

System Lab at their stand & demonstration at Mems & Imaging Sensors Summit @ Grenoble.

$\downarrow$

September 14 & 15 | System Lab on a booth presented at Sido Lyon.

### **OCTOBER**

### World Electronics Forum

October 5 | Nanoelec → partnered with international annual forum: World Electronics Forum (Grenoble).

### National Science Fest Campain

October 8 | Conference open to the public on Blockchain & Digital Identification (Grenoble).

$\downarrow$

### **Embedded Al**

October 18 | Business seminar: Embedded AI with Captronic, CEA and Mines St Etienne (Gardanne).

### **Digitizing SMEs in EU**

*October 24* | Final workshop of DigiFed European project, with Nanoelec.

# <image>

### NOVEMBER

### Digitizing SMEs in EU November 6-9

Nanoelec participated in annual international summit High Level Forum (Finland).

### November 9

Nanoelec partnered with CSAW'22.

### November 22

Annual Nanoelec/Carac colloquium.

### System Lab

### November 22

Conference and demonstration given at SEPEM @ Grenoble, November 2022.

### **DECEMBER 22**

### **Innovation Forum**

December 8 | Webinar open to the public and the press: preview of the 2022 iForum, with La Metro (Grenobleregion community), CCI etc.

### **General Assembly**

*December 13* | General assembly and the 10<sup>th</sup> anniversary of Nanoelec.

$\rightarrow$

### System Lab

*December* 8&9 | Stand and demonstration in SIDO Paris.

### **JANUARY 23**

Sustainable Electronics January 27 | Nanoelec/ Human Capital & Training Design program conducted a seminar: Technology usages: how does sustainable development influence decision making? With contributions from Schneider Electric, Grenoble-Ecole de management, Grenoble INP-UGA and CEA.

### **FEBRUARY 23**

### Photonics West

*February 2* | Presentation of III-V material integration on Si photonics platforms through direct bounding (wafer-towafer & die-to-wafer). As part of a Nanoelec initiative, the process is available for 200- and 300mm wafers. It is CMOS compatible and ready for large-scale integration.

### **Industry Attractiveness**

Two webinars on the attractiveness of the microelectronics industry: "Ninth-grade internships: How to spark interest in technology jobs" & "A learning kit for jobs in smart electronics".

### MARCH 23

$\wedge$

Industry attractiveness

*March 2* | Forty representatives from Nanoelec core partners gathered for an initial collective discussion on commitment, education and recruitment.

### International Women's Day

March 7 | In association with Y.Spot and CEA, Nanoelec conducted a round table: How to attract innovative female talent? Participants included high-ranking female managers from CEA, GEM, HP France, Lynred, UGA & Nanoelec.

### **Photonic Sensors**

*March 8* | CEA-Leti & Nanoelec booth at international Optical Fiber Communication conference (OFC), USA.

### Women in Engineering

March 27 | Nanoelec exhibition Women in Technological Research presented at the Laue-Langevin Institute.

$\checkmark$

### **APRIL 23**

Nanoelec ambassadors  $\rightarrow$

April 18 | Nanoelec exhibition Women in Technological Research presented at the La Casemate, the center for scientific culture in Grenoble, as part of the 50 Audacieuses event.

### 3D integration: design & architecture

*April 19* | Annual Nanoelec workshop at the DATE international conference.

System Lab -April 26 | Imagers, sports and health colloquium at CEA/Y.Spot (Grenoble).

### **MAY 23**

### Industry attractiveness

*May 11* | Local forum on the attractiveness of the microelectronics industry organized by Minalogic and Nanoelec. 150 attendees.

### Women in Engineering

*May 30* | Portraits of Nanoelec female ambassadors by students from Pablo Picasso Middle School (Echirolles) were presented at La Casemate, the center for scientific culture in Grenoble.

# FROM 3D INTEGRATION TO IMAGES

rogress in the semiconductor industry is divided into two classes: Moore's Law, where chips are manufactured with advanced technologies of 16 nanometers and smaller (this is the case for the processors at the heart of smartphones, tablets, PCs, and servers), and the More than Moore's approach, which uses mature manufacturing technologies of 20 nanometers and larger (this is the case for most components such as microcontrollers, power management circuits, sensors, power electronics, and radio-frequency circuits).

As the microelectronics industry continues to face challenges to further miniaturize components, according to Moore's Law, the More than Moore approach is also becoming more widespread. At Nanoelec in particular, we are building on 10 years of R&D on three-dimensional architectures, which now enable us to address very ambitious applications prospects.

3D integration, which consists in interconnecting electronic chips in 3 dimensions, is a promising solution for addressing the growing need for functionality, density and performance in future integrated circuits. However, to allow the rapid emergence of this technology in industry, an overall approach is needed, taking account of technological development and the design of new circuit architectures, the development of design and testing tools as well as reliability.

From 2012 to 2020, the academic and industrial teams working under the Nanoelec/3D Integration program focused on developing a comprehensive platform compatible with the full design cycle of new products. They dealt with technology for hybrid bonding wafer-to-wafer or die-towafer, but also design, electronic design automation (EDA) tools, testing and reliability.

In her talk at the Semi 3D & system Summit, Sylvie Joly<sup>1</sup>, Partnerships Manager for 3D integration & packaging at the Silicon Components Division of CEA-Leti and attached to Nanoelec, stated five challenges in hybrid bonding. "Supply chain integration, interconnection alignment, inter-die spacing reduction, efficient *electrical connections, processing* throughput are the challenges we are seriously working on", she comments. These challenges are all addressed through the partners of the Nanoelec programs focusing on applications: one devoted to image display technologies (Displed) and the other to sensing (Smart Imager).

Joly S. Hybrid Bonding from Hype to Reality: How Will Hybrid Bonding DTW Pave the Way to Large Set of Applications?

3D & system Summit 2022.

# SMART IMAGER

Eric Ollier, Optical Project Manager at CEA-Leti and Director of Nanoelec/ Smart Imagers program © PJayet/CEA

# From imaging to visioning

## SMART IMAGER PROGRAM

### $\rightarrow$ Vision

The transition from imagers to vision sensors is generating new market opportunities

### $\rightarrow$ Ambition

To provide key HW and SW building blocks, to validate them through demonstrations ranging from test vehicles and proofs of concept to the prototyping of a smart, multi-layer imager

### $\rightarrow$ Mission

Stacking/3D technologies, embedded AI and data management, New architectures

### $\rightarrow$ Partners

CEA, Lynred, Prophesee, Siemens EDA, STMicroelectronics, Grenoble INP-UGA Mastering smart imagers industrial process flow would be a competitive advantage for Nanoelec's industrial partners.

he Nanoelec/Smart Imager program is committed to providing relevant and real-time environment analysis by vision. It could be the greatest technical challenge at Nanoelec for the coming years.

The aim of IRT Nanoelec's Smart Imager program is to develop the technologies needed for the next generation of imagers, which will allow the transition from image generation to the analysis of the information included in these images, on the very sensor itself, in order to perceive a scene, understand the situation and intervene on it. This transition represents a very real disruption and a paradigm shift, with the computing and memory issues becoming preponderant, in addition to image generation. This revolution implies the use of artificial intelligence on the image sensor itself.

The consortium's goal is to develop 3D stacking technologies in order to implement artificial intelligence functions on the sensor itself. This is why we are working both on the components and on the software, to transition our image sensor concepts from image generation to data generation, enabling a situation to be analyzed.

Our program is very close to two other activities at Nanoelec: the System Lab initiative, on the search for new multi-spectrum imaging applications, and Displed, -new generations of displays- on the simulation & design tools for hybrid bonding components and technologies for 3D architectures.

# Technology, architecture & applications

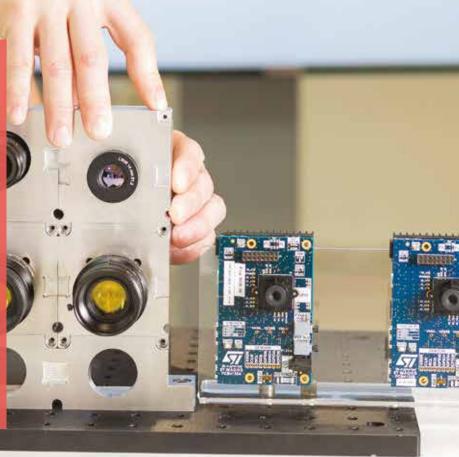

Transforming digital vision with cutting-edge 3D-stack camera sensors, global shutter and iToF

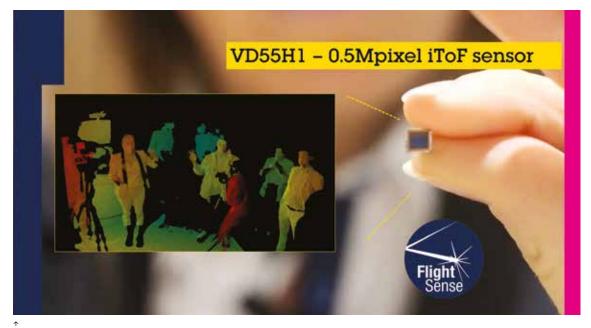

STMicroelectronics recently launched the VD55H1, a low-noise, low-power indirect time-of-flight (iToF) sensor array of 672 x 804 pixels (0.54 Mpixels). @ STMicroelectronics

STMicroelectronics is developing a whole range of new image sensors with unprecedented performance thanks to the 3D integration developed within Nanoelec.

3D architecture technologies are industrialized by STMicroelectronics in its four major imager application markets: automotive, industry, personal electronics and computers & peripherals. The international group is now proposing a full range of products based on these technologies developed within Nanoelec. "The work done within Nanoelec continues to support ST Crolles' technology roadmaps and to contribute to exploring future product architectures for the Imaging Division. 3D-stacking technology is now offered in foundry mode for selected partners", underlines Nicolas Roux, Product Line Manager at STMicroelectronics for Imaging Camera sensors.

STMicroelectronics provides Global Shutter type image sensors based on BSI (backside illumination technology) using 3D building blocks developed after several years within Nanoelec, including the Harmony demonstrator in 2018. "And very recently, teams involved in Nanoelec succeeded in demonstrating the possibility of combining fine pitch Cu-Cu hvbrid bonding technology with high density (HD) TSV", says Eric Mazaleyrat, Technology Scouting and Innovation Director at STMicroelectronics. "The device is made with three different stacked structures, built on 300mm wafers, and has very good characterization performance. Thus, STMicrolectronics is both developing products and looking forward to upcoming results from Nanoelec to keep its competitive edge in commercial competition in the field of smart imaging."

The group recently launched the VD55H1, a low-noise, low-power

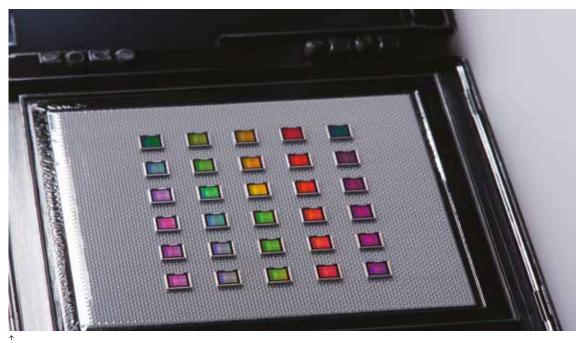

STMicroelectronics sensors VD55G0 and VD56G3 benefited from Nanoelec technologies to serve multiple applications in the field of low-power computer vision. © STMicroelectronics

indirect time-of-flight (iToF) sensor array of 672 x 804 pixels (0.54 Mpixels). "This imager is manufactured using advanced backside illuminated stacked slice technology, based precisely on developments made within Nanoelec. The VD55H1 comprises an image sensor "bonded" onto a 40nm CMOS circuit", says David Maucotel, Business Line manager. "In 2022, this product was evaluated by several customers who have started integration into their own platform. By comparison with comparable devices on the market, we offer moderate energy consumption, a low noise level and reduced chip size. The VD55H1 currently offers the best cost/resolution compromise on the market with a pixel size of 4.6µm."

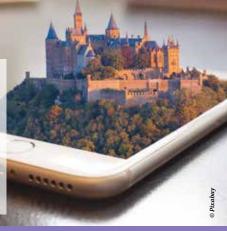

These time-of-flight (iToF) sensors provide smartphones and consumer electronic devices with advanced 3D vision and depth measurement capability, to build a 3-dimensional map of a scene, or human face, with a resolution of more than half a million points. Indirect Time-of-Flight measures the distance of each point from the sensor, from close distance up to five meters.

### "BIOMETRY AND SECURITY THROUGH FACE RECOGNITION BECOME MORE ROBUST THANKS TO THE HIGH RESOLUTION AND GREAT ACCURACY OF 3D IMAGES CAPTURED BY VD55H1..."

They are suitable for both augmented reality and virtual reality applications, such as room scanning, video games gesture and depth/color image fusion, or 3D avatar captures. They can also improve photographic performance in most recent smartphones: the "Bokeh" effect (portrait mode, background blurring), automatic selection of the camera and video segmentation, and faster picture shooting in low light (Laser Au-

tofocus). Biometry and security through face recognition become more robust thanks to the high resolution and great accuracy of 3D images captured by VD55H1, which improve the user experience in various applications such as phone face unlock, phone payment, access control in general, and high-resolution scene capture for robotics and industrial vision. ST and Nanoelec 3D-stack technology are also suited to the recent image-sensor portfolio, with leading-edge pixel array (top die), while keeping more silicon area on the bottom die to increase digital-processing capabilities and features. Pixel resolution can be increased, with high sensitivity and low crosstalk.

Two new sensors VD55G0 (640 x 600 pixels) and VD56G3 (1.5 Mpixels) have benefited from these combined technologies and can now serve multiple applications in the field of low-power computer vision, AR/VR headsets, or face authentication.

### Technology, architecture & applications

### The physical limits of resolution

During his presentation at the Nanoelec General Assembly in December 2022, Xavier Brenière, head of the applications laboratory at Lynred illustrates the link between the two Nanoelec programs: Smart Imager and System Lab. © *Cédrine Tresca/CEA*

Integrating signal processing into the sensor itself will give access to improved image quality and lower electrical consumption.

XAVIER BRENIÈRE, head of the application laboratory at Lynred, tells all.

### Your primary motivation in Nanoelec is to improve resolution and on larger formats. Why is this a paradox?

The advanced technologies to which we have access under the Nanoelec/Smart Imager program are enabling the size of pixels in a camera to be gradually reduced, both in visible and infrared. But paradoxically, when the pixel pitch reaches the wavelength to be captured, the physics changes, with diffraction taking precedence over absorption, so there is not necessarily a direct gain in resolution.

### Visible imagers are therefore reaching this limit, is this also the case of infrared imagers?

In the visible spectrum, we are nearing pixel pitches of almost 0.5 microns, for wavelengths of between 0.4 and 0.8 microns. Similarly, with bolometers, Lynred is achieving pitches of 8.5 microns for a detected wavelength range of 8 to 14 microns.

### Could one hope to improve resolution further simply by reducing the pixel pitch?

Not directly, but this raises interesting questions of physics: by further reducing the pitch, could one take advantage of this pixel over-sampling, the plasmonic function or more advanced functions. This is a very interesting field of research for both the visible spectrum and infrared. 3D stacking will enable signal processing to be integrated into the sensor itself, to improve image quality, facilitate its interpretation or object recognition, while reducing the system's overall electrical consumption.

The work done in 2022 under the Nanoelec/Smart Imager program enabled you to consolidate several technical points and envisage future socio-economic benefits. What are they?

From the technology viewpoint, we have completed the definition of a 3D technological stack compatible with our two product families: cooled diodes and bolometers, which have totally different structures. We have defined the stacking sequence and checked the strength of hybrid bonding, in particular for cooling cycles at cryogenic temperatures.

Progress has also been made in exploring options for the final architecture including the processing of pixel signals, memory and algorithmic image processing.

### Lynred is involved in two Nanoelec programs. What are you hoping for?

With Smart Imager, we are addressing major technological challenges. Nanoelec enables us to invest for the medium/long term: we envisage that 3D stacking technology and the associated architectures will appear in our products by the 2030 timeframe. In addition, the System Lab initiative enables us to continue the process with research opening up new applications possibilities, to which these technological advances are opening the door.

### Technology, architecture & applications

# Dynamic response and frugality of event-based image sensors

Based in Paris and Grenoble, Prophesee is developing event-based sensors.

### JEAN-LUC JAFFARD,

Senior Advisor for innovation at Prophesee, explains what his company is looking for in the Nanoelec/Smart Imager program.

### The traditional approach to imaging consists in taking a series of images, right?

This is done full frame and at high frequency: the sensation of movement is thus recreated. There are two main drawbacks in this method. Firstly, it generates a large amount of data to be processed and it consumes energy. Moreover, it is impossible to know what is happening between two image acquisitions.

### How is the Prophesee imaging approach truly disruptive?

Our approach is more audacious but far harder to implement: we are developing sensors which only react when there is a change in contrast: if nothing happens, they generate nothing. Only those pixels which perceived a change are lit: if a spot of light reaches a single pixel, this pixel will be capable to detecting it at high speeds corresponding to several million events per second.

### Why is this hard to do?

When you try to make sensors which only detect changes, you need "smart" pixels. In a traditional sensor, there are 3, 4 or 5 components per pixel, whereas in an event-based sensor, we have 80 to 100 components per pixel.

So how do you reduce the size of the event-based pixels and inte-

### grate them at the heart of these necessary components?

The challenge is to maximize the information processing inside the pixel. To be able to manufacture small pixels (to increase image resolution) and directly integrate the smart data functions, 3D integration is the path we are exploring within the Nanoelec/Smart Imager program.

Prophesee event-based sensor. © Prophesee

# Test chips & performance assessment

### First demonstration of 2-layers test vehicle

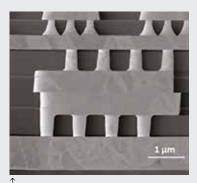

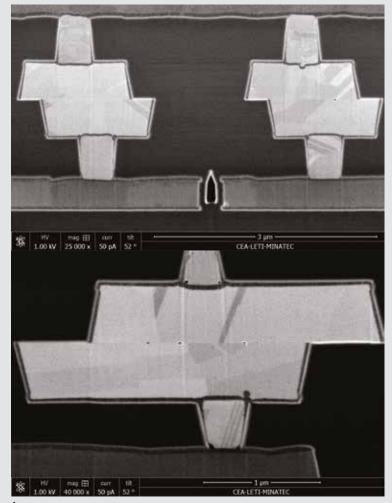

For the Smart Imager program, a CEA-Leti team demonstrates wafer level Face-To-Back (F2B) 3D integration combining fine pitch Cu-Cu hybrid bonding with high density TSV.

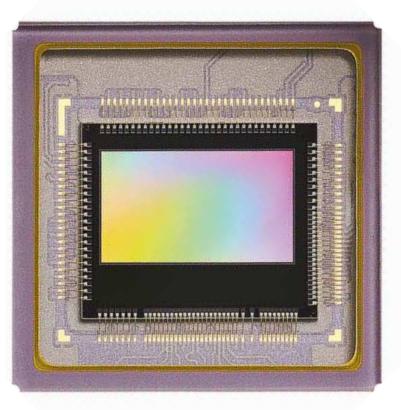

CMOS Imagers have adopted 3D integration with Back-Side Illumination (BSI) technology, with two layers stacked using wafer-to-wafer hybrid bonding technologies. The industry implements such technology for current CMOS imager sensors for various applications including the consumer market, allowing form factor reduction, pixel resolution increase, high performances and low energy consumption. This technology enables the assembly of optimized CMOS image pixel technology onto a CMOS layer dedicated to imager logic acquisition and data processing.

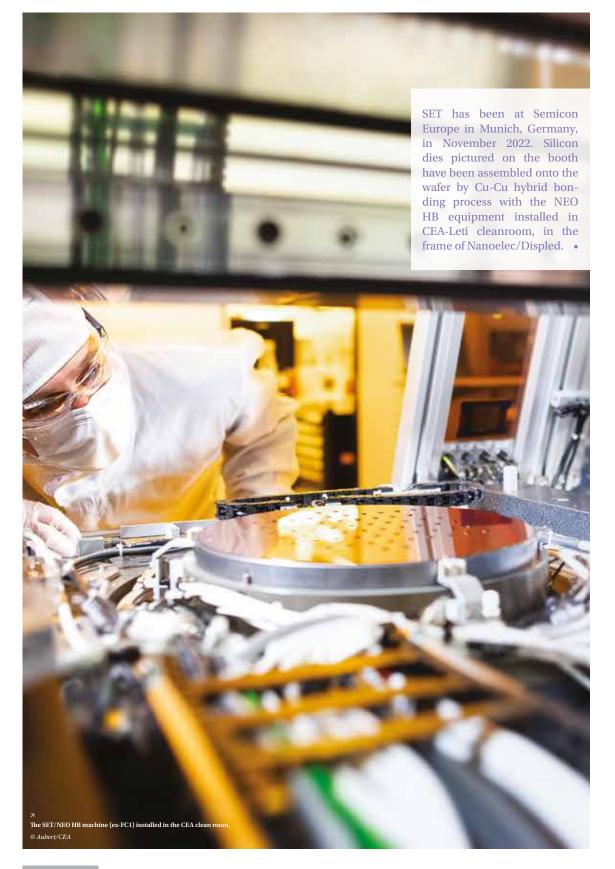

In April 2022, at the VLSI-TSA International Symposium in Taiwan, a team from CEA, working within Nanoelec, presented new 3D design and technology solutions developed in order to build a 3-layers Smart Imager<sup>2</sup>. *"We demonstrated* our expertise in 3D technologies capable to enable manufacturing of 3-layers smart imagers: hybrid bonding technology for the assembly of multi wafers with sub-micron pitch capability and also High Density Through Silicon Via (TSV) with diameters less than 1 micron", says Stéphane Nicolas, project leader in the field of 3D heterogeneous integration at CEA-Leti, one of the authors of the study. In addition, the team proposed a Place & Route methodology with the associated PDKIT to take advantage of 3D fine pitch interconnects. The methodology refers to Design Technology Co-Optimization (DTCO) capabilities. This activity is key to develop new methodologies and design tools enabling innovative 3D stacked architectures, in order to offer AI processing at the edge within the image sensor itself targeting innovative AI and Machine Learning applications.

At the ECTC 2023 Conference, the same team presented the test vehicle demonstrated in 2022. "We have successfully fabricated a 2-Layers Face-To-Back (F2B) test vehicle (TV) by combining fine pitch Cu-Cu hybrid bonding technology with high density (HD) TSV", says Stéphane Nicolas. Morphological characterizations carried out recently highlighted the integrity of the 3D structure. Furthermore, the results of electrical tests on Kelvin and Daisy-Chain structures demonstrated the electrical continuity between all the layers. These results validates the technological integration flow and the compatibility of HD-TSV with fine pitch hybrid bonding. This key building block that is mandatory to demonstrate the feasibility of 3-layers imagers.

### Ę.

- Vivet P., Arnaud L., Borel S., Bresson N., Assous M., Nicolas S., Mauguen G., Moreau S., Altieri M., Billoint O., Thuriès S. & Ollier E. Advanced 3D Design and Technologies for 3-Layer Smart Imager. 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 1-2. https://doi.org/10.1109/ VLSI-TSA54299.2022.9771026

- S.Borel, S. M. Assous, M., Moreau, S., Vélard, R. Recent Progress in the Development of High-Density TSV for 3-Layers CMOS Image Sensors & Suarez-BErru, J-J. Nicolas, S., Bresson, N., Assous, M., Borel, S. Demonstration of a Wafer Level Face-To-Back (F2B) Fine Pitch Cu-Cu Hybrid Bonding with High Density TSV for 3D Integration Applications : two conferences presented at IEEE 73rd Electronic Components and Technology *Conference, Orlando, Florida, May 30 - June 2, 2023*

Cross-sectional SEM micrographs of HD TSV in a dense environment. © CEA

Javier Suarez presenting "Demonstration of a Wafer Level Face-To-Back (F2B) Fine Pitch Cu-Cu Hybrid Bonding with High Density TSV for 3D Integration Applications" at IEEE ECTC Conference 2023. © Joly/CEA

# Design & design tools

Optimizing the architecture of the future 3-layer sensor

About electronic design automation (EDA), through participation in Nanoelec's Smart Imager program, Siemens EDA<sup>3</sup> contributes to establish reference flows for the design and verification of the integrated circuits that will be created by the IRT partners.

The participation of Siemens EDA in Nanoelec "enabled us to obtain state-of-the-art circuits to validate the design and verification flows used with its tools and enjoy strong interaction with the CEA design teams", says Jean-Marc Talbot, Senior Solution & Strategic Partnerships Director at Siemens EDA. The market for CMOS imagers is growing rapidly and Siemens has had major customers in this sector for many years. The work carried out in Nanolec as part of industrial R&D is demonstrating the performance and efficiency of Siemens' commercial tools for this type of integrated circuit, and contributing to the development and testing of new tools by taking advantage of the CEA's R&D environment and measurement capabilities to ensure that simulation and experimental results match. "We are also incorporating feedback from the community to continuously improve the performance of our design tools when used on the most advanced demonstrators and platforms", adds Jean-Marc Talbot.

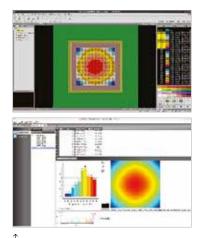

Results of the thermal analysis with the Sahara tool of an architecture for the future 3-layer imager developed under Nanoelec/Smart Imager. © Siemens EDA

Regarding the future 3-layer imagers, Siemens EDA implements a number of flows and tools, including its Symphony mixed digital-analogue verification platform for verifying multilayer imagers, its Catapult high-level synthesis tool in conjunction with the CEA's N2D2 tool to automatically generate the RTL of the imager's IA layer, and the simulation of the power consumption of digital and analogue circuits using the mPower tool, 3D placement-routing using the Aprisa tool, etc. New tools to take account of electromigration phenomena and chip-package interactions are also being developed and tested.

The thermal effects associated with the operation of the future 3-layer imager and its package are also studied. *"The project Sahara software prototype processes the simulated heat dissipation and hot spots on a die and its package"*, explains Lee Wang, head of development of SAHARA prototype, which will become a product in 2023. Lee Wang also took part in the Nanoelec Awards 2022 "for women in technology research".

Sahara is an example of a long-term collaboration with the CEA that has enabled Nanoelec to move from prototype software to a product. There will be others in Nanoelec phase 3.

"This study enabled us to create the methodology and acquire the knowhow to perform a thermal analysis of a complete 3D device, including the integrated circuits and their package, with the Siemens Sahara tool," adds Lee Wang. The thermal analysis proposed methodology enables to analyze the impact particular with the addition of the third imager layer, and iterate on the parameters of the thermal model, such as technology parameters, package, power budget, and circuit architecture, as often as necessary to optimize the architecture of the sensor before it is manufactured.

### Ş

The Siemens Electronic Design Automation SARL - Siemens EDA company, the world leader in design, verification and manufacturing-aid tools for integrated circuits, packages and PCBs, is one of the founding members of IRT Nanoelec.

### Images & photons | SMART IMAGER

### Design & design tools

### Heterogeneous Packaging Design and Verification Workflows

"Chiplet architecture is an answer to semiconductor scaling challenges", says Anthony Mastroianni, Advanced Packaging Solutions Director, Siemens EDA in a keynote speech at the DATE'22 Conference<sup>4</sup>.

"Cost and yield are driving alternatives to monolithic solutions; it provides low latency at high bandwidth for data movement; In addition, fabrication flow by heterogeneous integration provides a path forwards."

Showing the heterogeneous integration product design process, he presented strategies for System Technology Co-Optimization (STCO) and 3D IC Test tools & methodology.

Mastroianni, A. 2022, March 18 Heterogeneous Packaging Design & Verification Workflows. DATE'22. https://date22.date-conference. com/workshop/w02

### Design & design tools Building a worldwide overview of 3D integration

### The yearly international workshop on 3D integration at the DATE conference attracted 50 experts.

3D technologies are becoming more and more pervasive in digital architectures, as a strong enabler for heterogeneous integration. Considering the large amount of data required and the associated memory capacity, Machine Learning and AI accelerators could benefit from 3D integration not only for High Performance Computing (HPC), but also for edge and embedded AI within image sensors. "3D integration and associated architectures are opening up a broad spectrum of system solutions, from chiplet-based partitioning for High Performance Computing to various sensors such as fully integrated image sensors embedding AI features, but also with the close 3D coupling of computing & memory enabling an efficient In-Memory-Computing paradigm", says Pascal Vivet, Scientific Director at CEA-List and Deputy Director of the Nanoelec/Smart Imager Program who every year organizes a dedicated workshop at the Date conference<sup>5</sup>. Date is the annual reference event for electronic system design automation & testing in Europe.

"In 2022, our 3D Integration workshop attracted 50 experts from both academia and industry, interested in this exciting and rapidly evolving field, in order to update each other on the latest state-ofthe-art, exchange ideas, and discuss future challenges. We discussed Heterogeneous 3D Architectures and Sensors", says Pascal Vivet.

Pascal Vivet (CEA-List), Deputy Director of the Nanoelec/Smart Imager Program organizes a dedicated workshop at the DATE conference every year. © Plawet/CFA

The workshop was co-sponsored by Nanoelec. Keynote and invited speeches were provided by experts from CEA, Qualcom, Georgia Tech, Stanford University, ETH-Zurich (Switzerland), Fraunhofer

### "THE CLOSE 3D COUPLING OF COMPUTING & MEMORY ENABLING AN EFFICIENT IN-MEMORY-COMPUTING PARADIGM"

Institute, University of Seville, Prophesee, STMicroelectronics, NTU (Singapore), Boston Univ., Univ. of Manchester, Notre Dame Univ, META Group (Facebook), Siemens EDA, Intel.  "3D Integration: Heterogeneous 3D Architectures and Sensors" Workshop at DATE'22 conference https://date22.date-conference. com/workshop/w02

لیک

# Silicon Technology

### Towards reliable hybrid bonds for 3D stacked IC

Direct hybrid bonding is the solution of interest for advanced 3D stacked Integrated Circuits (IC) with very short interconnect pitches.

3D integration technologies emerged less than 10 years ago as viable solutions for meeting IC requirements such as higher performance, increased functionality, lower power consumption, and a smaller footprint. Some examples of 3D integration in products are CMOS Image Sensors (CIS), memories and interposers.

"Presently, to ensure vertical electrical connections, Through-Silicon-Vias (TSV) are integrated into most of these products, because they allow die-level assembly, and simplify some aspects of testing and packaging, but the main drawback of TSV is the Keep Out Zone (KOZ) combined with a Cu pillar pitch typically limited to 20-40µm", explains Stéphane Moreau, Research-Engineer in Reliability of 3D integration at CEA-Leti. "For some applications, such as CMOS image sensors and memories, smaller pitches (<  $10\mu m$ ) are required for the vertical die-to-die connections; so direct hybrid bonding technology is the solution. While hybrid bonding based products are already on the market, few studies are being published with data about robustness/ reliability", says Stéphane Moreau

who reviewed reliability threats for hybrid bonding-based interconnects at the VLSI22 Symposium<sup>6</sup>.

The potential threats identified by the scientific community are moisture ingress, thermomechanical stresses, electromigration, Cu diffusion, dielectric breakdown. In particular, two topics have been studied in depth: electromigration (times-to-failure, failure analyses, acceleration model) and copper diffusion (electrical and analytical characterizations). In the light of the scientific community results, even if the hybrid bonding-based interconnect is a new way to interconnect two tiers, its behavior against common reliability threats are very similar to that of the BEoL.

Given the published works, even if hybdrid bonding module could raise specific reliability issues, all the lights are green for mass production with micrometric pitches, which is consistent with the fact that this technology is already implemented in some products. On the contrary, for sub-micrometric pitches some questions remain topical: dielectric reliability including Cu diffusion, electromigration. In addition, robustness/reliability of heterogeneous stacking (different materials or dies) must be investigated in depth. Engineers and researchers are still working on these topics to find tricks to solve the potential reliability issues.

### Ş

Moreau S. 2022, June 12 Reliability Threats of Hybrid Bonding-Based Interconnects: Toward Mass-Production. VLSI22: 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), USA.

Electronic imaging of hybrid bonding failed structure (void in Cu material) after an accelerated electromigration test: (presented at IRPS 2023 Conference)

Electronic imaging of Hybrid bonding structure without defect.

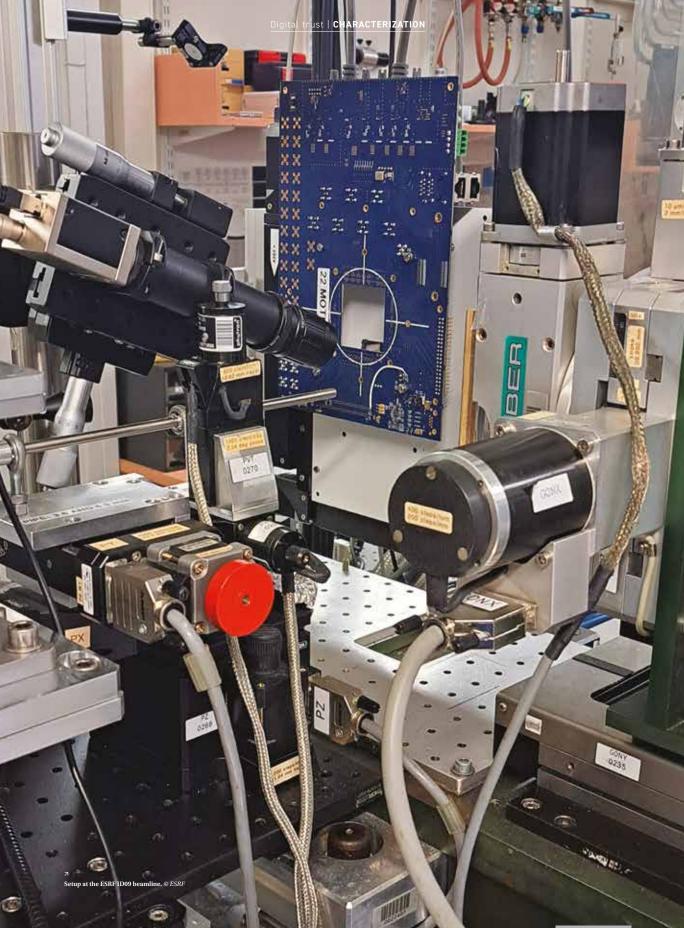

### Silicon Technology Characterizing connectors

### Quality of the Cu pad connectors is an issue for a 3D stack IC.

In the Nanoelec/Smart Imager program, Cu pads as small as 300nm are used with hybrid bonding technology to reach extremely high interconnect density between 3D electronic chips. Successful bonding relies directly on the thermomechanical displacement of Cu above the oxide matrix. "Hence, the control of this technology relies on a profound understanding of the thermomechanical behavior of 300nm Cu pads", explains Bassel Ayoub, PhD student working at

STMicroelectronics, CEA-Leti and the University of Bordeaux, in a paper published in Microelectronic Engineering<sup>7</sup>.

X-ray synchrotron Laue micro-diffraction was used to monitor the strain state and orientation of individual Cu pads in-situ during heat treatment. The experiment was conducted on the ESRF 32 beamline. "A clear relationship between Cu pad microstructure and their mechanical behavior as a function of temperature up to 400 °C has been established", says Bassel Ayoub. "With smaller pad sizes, the microstructure plays an important role in hybrid bonding."

### <u>ل</u>

7. Ayoub B., Moreau S., Lhostis S., Frémont H., Mermoz S., Souchier E., Deloffre E., Escoubas S., Cornelius T. W., & Thomas, O. (2022) In-situ characterization of thermomechanical behavior of copper nano-interconnect for 3D integration. Microelectronic Engineering, 261, 111809. https://doi. org/10.1016/j.mee.2022. 111809

How Henri Matisse would have painted an electronic circuit? **Open AI Dall.e provides an** answer.

© created with Open AI Dall.e. 2023

© ESRF

François Templier, Strategic Marketing manager for displays at CEA and Director of the Nanoelec/ Displed program © PJayet/CEA

32 | Highlights of the IRT Nanoelec, 2023 edition

# Towards Display Technology Leadership in Europe

### DISPLED PROGRAM AT A GLANCE

### $\rightarrow$ Vision

A unique opportunity for a French & European ecosystem on large display technologies for immersive applications

### $\rightarrow$ Ambition

To design and demonstrate key microLED technologies for high-end, immersive/ interactive displays

### $\rightarrow$ Mission

To develop process flows for microLED, Smart-pixel fabrication and mass transfer onto the display

→ Partners

Aledia, CEA, EVGroup, SET

The Nanoelec/Displed program prepares real breakthroughs in the display industry value chain as well as new image functionalization.

### he aim of the Displed program is to bring display production back to France.

MicroLED displays are coming, with the promise of better image quality, but with very real technical and industrial challenges. The smartpixel, combining microLEDs with a CMOS driver at wafer level, will help solve some of them: better driving performance, simplified mass transfer, ...

The Nanoelec/Displed program is highly innovative, particularly in providing a compact, full-CMOS driven RGB microLED pixel (the smart-pixel), which is fabricated using a unique wafer-to-wafer direct hybrid bonding technique.

The aim of the program is to demonstrate the industrial scale feasibility of the Smart Pixel concept.

The project is based on creating a value chain with a focus on specific steps: assembly of microLED wafers and CMOS wafers, technologies for mass transfer of smart pixel components to a substrate. The technical hurdles relate to the technical and economic viability of the concept: transfer of very small chips on a very large scale and at very high speed. The project is built around five main work packages: wafer assembly using 200mm technology, scaling to 300mm technologies and development of packaging and mass transfer solutions for Smart Pixels. Finally, the work will undergo a demonstration phase, and a final activity focuses on the exploration of flexible, immersive, solutions for very high-end displays.

In 2022, we obtained the very first results of our pilot initiative on life cycle analysis as applied to the early R&D phase on smart-Pixel. The first proof-of-concept has been produced on a 2D-Led blue smart-pixel. We investigated two mass transfer solutions (full-wafer laser debonding of  $110x110\mu m^2$  dies and picking of dies as small as  $75\mu m$ ). We also achieved a break-through for 3D Integration with NanoCleave layer release technology. At the same time, our key partner Aledia has nearly completed the construction of its first production building in Champagnier.

# **Building the smart pixels**

Aledia's first nanowire LED platform is now reaching promising performance levels

Philippe Gilet, CTO of Aledia (Core partner of the Nanoelec/Displed program), gave a talk at Display Week<sup>1</sup> (May 2022, San Jose, USA).

Philippe Gilet unveiled the very first results on GaN nanowire technology for mass production of high-performance innovative displays in Europe. "A huge display market is looking for next-generation technology", he reminded his international audience, presenting the promising advantages of MicroLEDs when compared with the current LCD and OLED technology<sup>2</sup>.

"The size of the market for consumer displays alone is estimated at \$120 Billion/year. Gan-on-Silicon technology will allow us to propose disruptive breakthroughs on displays: brighter, more efficient (longer battery life), new architecture for electronic integration as well as Native-RGB monolithic integration on one chip with only GaN", he adds.

The company has 220 staff and is ISO 9001 certified and benefits from more than 200 patent families. The presentation highlighted how, at low current density, smallsize chips (less expensive) with 3D MicroLEDs are more efficient than with 2D MicroLEDs made on sapphire substrate. *"Aledia's 3D microLED technology enables large-*

Philippe Gilet, CTO of Aledia, presenting the very first results of the Nanoelec/Displed program to a delegation of the French National Research Agency, in September 2022.

area silicon to be used. We would make use of low cost and high manufacturability foundries.

This will also allows us of easiest integration of the electronics. In 2022, Aledia demonstrated an first result on RGB active matrix display on an 8-inch silicon wafer for a blue wire-LED. Measured brightness was up to 5500 nits on a full screen (compared to <1000 nits for OLEDs and conventional displays)", says Philippe Gilet. Aledia's first nanowire LED platform is now reaching ac-

### P

- Philippe Gilet, "GaN Nanowire Technology : Moving to Product", Society for Information Display, Display Week, May 8-13th 2022, San Jose, USA

- MicroLED uses microscopic light-emitting diodes to create images. It is a type of LED display that offers many advantages over traditional LED and LCD displays, including greater brightness, better contrast, wider color range, and lower power consumption.

ceptable performance levels. "This platform will allow the production of LED chips ranging from 100µm down to 2µm with no efficiency change. We are on track for rampup production in 2023 on 200mm Si, evolving to 300mm Silicon to meet high volume demands from end 2024."

At the International Micro/Mini LED Display Conference<sup>3</sup> (April

2022, Taipei, Taiwan), Philippe Gilet underlines that an emerging consensus from all major display players makes MicroLEDs 'THE' next display technology. Competition will be stiff but WireLED technology developed by Aledia in collaboration with the CEA under the Nanoelec/Displed program presents huge advantages and perfectly fits the display specification requirements. Ş

Philippe Gilet, "Moving microLED manufacturing to 300mm wafer size", Touch Taiwan, 27-29<sup>th</sup> April 2022, Taipei, Taiwan.

### **Building the smart pixels**

First results on Smart-Pixel Life Cycle Analysis

Environmental impacts must be taken into account when developing any new technology. This applies to the display industry design work carried out by the Nanoelec/Displed program.

This year the SmartPixel Life Cycle Analysis (LCA) began. *"The overall* objective of this study is to assess the environmental impacts of this kind of display manufacturing, considering not only climate change but also all the sixteen environmental impacts recommended by the Product Environmental Footprint method (PEF). Hence, the aim of this study is for the first time to propose a methodology based on LCA", explains Antonin Holo, LCA engineer at CEA-Leti, which carried out the study. An initial set of results has been obtained, for all sixteen environmental impact categories of the PEF 3.0 method recommended by the European Commission. *"For example, the contribution of the epitaxy step could be seen with regard to every environmental impact. Etching, deposition and stripping process-family contributions were also underlined, given their large share of each of the selected environmental impacts",* Antonin Holo reports.

Since there are no databases for microelectronics at the component scale, or the literature is outdated and does not reflect current trends, this LCA will produce new and previously unseen results. These new LCA results are used on an in-house eco-design tool, allowing comparison of new technologies with reference technology. It relies on a similar tool designed by CEA-Liten for photovoltaic R&D<sup>4</sup>. The fabrication flow parameters can be easily altered in order to obtain an overview of how this changes the sixteen environmental impacts addressed.

Among other results of interest is the demonstration of the impact of the electricity type (carbonated vs. nuclear) on CO<sub>2</sub> generation for "IN FACT, THE BIGGEST FACTOR IMPACTING OUR CARBON FOOTPRINT IN THIS PROCESS IS THE CONTRIBUTION OF CMOS."

smart pixel fabrication. "In fact, the biggest factor impacting our carbon footprint in this process is the contribution of CMOS. If we source it from Asia, the impact on the climate is high; if we buy it from a country with a low-carbon energy mix, the balance is more favorable", explains Sandrine Chabaud, Safety and Environment Manager at Aledia.

> Nouha Gazbourg, "Systemic integration of Eco-design in photovoltaic technologies R&D", UGA PhD Report on a doctoral thesis prepared at CEA-Liten, Feb. 2019.

### **Building the smart pixels**

### An unprecedented eco-innovation method applicable as of the R&D phases

The methodology and the tool used for the Ecodispled project are directly adapted from the work done by CEA-Liten. Nouha Gazbour, research-engineer, and eco-innovation manager at CEA-Liten and at the Ines.2s ITE (energy transition institute), originated this development, initially intended for the eco-design of photovoltaic panels.

### Why is addressing environmental issues in R&D projects still an emerging phenomenon?

Two main reasons can be postulated: on the one hand, evaluating the environmental impact is relatively complex for an immature technology currently under development (low Technology Readiness Level (TRL)), as its fabrication characteristics and processes are not yet all known; on the other, there are problems with the tools identified which limit their adoption by the R&D organizations (complex to learn how to use them, analysis of the pertinence of the results).

The work of my thesis, at the French National Institute for Solar Energy (CEA and Savoie Mont Blanc University), aimed to develop a methodology to allow lasting integration of eco-design into the R&D organizations, to support their industrial partners in their innovation and competitiveness efforts.<sup>5</sup>

### How do you use LCA<sup>6</sup> in your approach?

The method developed is based on the principle of estimating the degree of technical, economic and environmental developments in a new technology (low TRL) via a reference database. LCA is the primary tool for construction of this database, in order to provide reliable results, despite the low TRL.

Nouha Gazbour, research-engineer, eco-innovation manager at CEA-Liten and at the Ines.2s ITE

### To what extent is this tool usable by all engineers in the PV field?

To ensure long-term adoption of this approach as of the R&D phase, the method was implemented in a computer tool for crystalline silicon photovoltaic systems, which represent more than 90% of the current PV market. The tool works by differentiation with an LCA on a reference process: you change a parameter in the process and observe the corresponding change in the environmental impact parameter.

### To what extent can this tool, initially developed for PV, be transposed to other technologies, including microelectronics?

A similar methodology and tool are currently being deployed for battery technologies, hydrogen production and the recycling of materials. The microelectronics field is well represented, with the work being done under Nanoelec by Antonin Holo, LCA engineer at CEA-Leti.

This work reinforces the deployment of eco-design in the sector and the inclusion of the environmental impact of the technologies as of the very first TRL levels. It will help guide the technological choices well upstream of industrialization and deployment of the technology, so as to reduce the environmental footprint of future video screens.

> Nouha Gazbour, "Systemic integration of eco-design in photovoltaic technologies R&D", Doctoral thesis presented on 14 February 2019 at Grenoble-Alpes University.

<u>ل</u>

<sup>6.</sup> Lifecycle analysis (LCA) is a method for systematic and quantified evaluation of the potential environmental impacts of a product, service or process, throughout its lifecycle. It is able to evaluate the impacts on the environment, through parameters such as depletion of natural resources, greenhouse gas emissions, water and air pollution, waste, etc.

# Mass transfer of smart pixels

# Next-generation 3D semiconductor packaging

One of the major steps in the process required to control the full production of a microLED display is the mass transfer of the smart pixels to the physical substrate of the display.

This step requires high fidelity and a very fast flow given that a display is composed of millions of pixels. Two core partners of Nanoelec are paving the way for mass transfer through step-by-step improvements to their wafer-to-wafer and die-to-wafer bonding tools: SET and EVGroup are key international players for more-than-Moore enabling technologies.

The breakthroughs they achieve with the support of Nanoelec represent important milestones in accelerating the deployment of heterogeneous integration in next-generation 3D semiconductor packaging, by direct hybrid bonding7. Such technologies are required for cutting-edge applications not only for displays but also for artificial intelligence, autonomous driving, augmented/virtual reality and 5G, all of which require the development of high-bandwidth, high-performance and low-power devices, without increasing production costs.

## Ļ

7. Direct hybrid bonding is a permanent bond that combines a dielectric bond (SiOx) with embedded metal to form interconnections It requires a design with face-to-face connection of the wafers and processing with ultra flat surfaces.

## Full-wafer laser debonding of dies

EVG continues to grow while keeping all the production and development of its tools in Austria, in Europe, and remains committed to this strategy. The projected business growth will result in several hundred additional jobs. EVG now has more than 1200 employees worldwide and almost 1000 at its headquarters in Austria. Laurent Michaud, EVGroup engineer based in Grenoble, presented the Gemini EVG machine for 3D bonding R&D in the Nanoelec/Displed and Smart Imager Programs © F.Legrand/CEA

In 2021 and 2022, the Austrian supplier EVG confirmed the positive impact of Nanoelec developments on its product lines.

"The bonding sub-systems that have been developed are integrated into equipment designed, fabricated, and sold by the company", says Markus Wimplinger, Corporate Technology Development & IP Director at EV Group. This is done with an impact evaluated by the company management at several hundred million euros on advanced semiconductor markets such as memories and processors.

→ 38

"The work performed in the Displed program is enabling EVGroup to extend its roadmap in the field of heterogeneous integration based on equipment and processes for the collective manipulation of chips on wafers", Markus Wimplinger adds.

In 2022, EVG announced a breakthrough for 3D Integration with NanoCleave<sup>™</sup> layer release technology. "IR laser cleave technology enables nanometer-precision layer transfer through silicon, eliminating glass substrates for advanced packaging and enabling thin-layer 3D stacking. Having access to a state-of-the-art sample through a program like Displed is key to deve-

### *loping and improving this technology*", explains Markus Wimplinger.

In 2021, EVG unveiled the EVG°40 NT2 automated metrology system, which provides overlay and critical dimension (CD) measurements for wafer-to-wafer (W2W), die-towafer (D2W) and die-to-die (D2D) bonding as well as maskless lithography applications. "Given that EVG does not have the capability to prepare adequate test material in-house for such applications, the partnership with CEA-Leti within IRT Nanoelec is very important, as it connects us with world-leading capabilities from the other partners in this consortium.

Moreover, this collaboration gives EVG access to the required materials and technologies and also enables us to perform cutting-edge research and development", adds Markus Wimplinger.

New milestones were reached, such as die-to-wafer fusion and hybrid bonding with 100-percent die transfer yield on a multi-die 3D system-on-a-chip. This achievement was carried out at EVG's heterogeneous Integration Competence Center<sup>™</sup> (HICC) with a GEMINI<sup>®</sup>FB automated hybrid bonding system. The design and performance of this tool were improved thanks to previous work done with Nanoelec. ●

#### Mass transfer of smart pixels

# Picking of dies as small as 75µm

SET, a French instrumentation SME evaluated a vacuum tool made by CEA, on its own flip chip bonder in its cleanroom. "After optimization, it appeared to be well handled by the equipment, and the vacuum is sufficient to manipulate micro-components as small as  $75\mu m$ ", says Pascal Metzger, CEO of SET, a core partner of Nanoelec.

With regard to the mass transfer of microLEDs, SET is working with the other Nanoelec/ Displed partners on the feasibility of a concept, which is a prerequisite for an industrial machine that will be essential for the deployment of a screen production line in France and Europe. *"With the Nanoelec ecosystem, we feel we have a* good lead in the field of direct bonding, particularly in terms of assembly precision and yield", Pascal Metzger adds.

#### Mass transfer of smart pixels

# Proof of concept for fabrication of CMOS-driven MicroLED displays

In December 2022, François Templier, CEA-Leti & Nanoelec/ Displed program director and Christophe Dubarry, a research scientist at the Silicon Component Department of CEA-Leti and a major contributor to the Nanoelec/Displed program, were invited to talk at the International Display Workshops IDW'22 in Fukuoka, Japan<sup>9</sup>.

They reviewed challenges and solutions for the fabrication of CMOS-driven Microled Displays from classical flip-chip to fully monolithic.

"These technologies address different challenges, the connection pitch being one of them since it determines the pixel pitch. A huge number of companies and institutions are involved, which is bringing about significant progress. Overall, MicroLED and CMOS integration technologies can be leveraged to fabricate microLED displays of all sizes and types, from AR/MR microdisplays to smartphone, to TV, to outdoor panels", says Christophe Dubarry after the talk and the associated paper.

"From our viewpoint, within Nanoelec, we are developing a novel approach including direct transfer of a Gan epilayer to a CMOS active matrix. Our proof of concept has been demonstrated on 200mm wafers by direct bonding. We obtained operating MicroLEDs after the transfer process and post processing (patterning). A record

Under the Nanoelec/Displed program, CEA-Leti achieved interconnection by direct hybrid bonding with a pitch of 3 microns (FIB-SEM X-section of Copper / silicon oxide hybrid bonding area).  $\odot$  (CFA

pixel-pitch GaN microLED array reaches 3µm and we measured the required electrical characteristics," adds Christophe Dubarry.

These technologies address different challenges. MicroLED and CMOS integration technologies can be leveraged to fabricate microLED displays of all sizes and types, from AR/MR microdisplays to smartphones, TV displays and outdoor panels.

## ι.

IDW Japan: F. Templier and Ch. Dubarry, "Challenges and Solutions for the Fabrication of CMOS-driven Microled Displays" Invited paper, International Display Workshops 2022 (IDW'22), Fukuoka, Japan, Dec 14-16 2022, (2022)

# **Building the factory scale**

# Production building almost completed

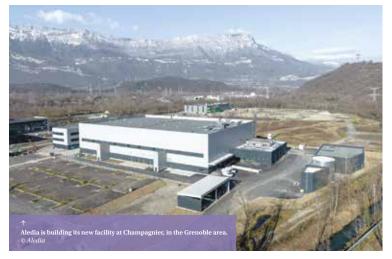

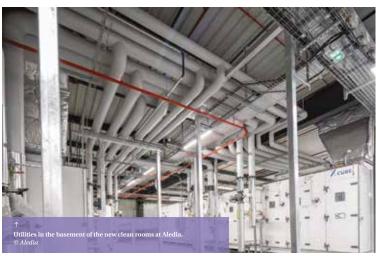

In 2022, Aledia finalized the installation of their pilot line at Echirolles<sup>11</sup>.

"This site was fully operational at the end of 2022 and will allow us to speed up our development and start sampling for customers in 2023", said Philippe Gilet, CTO of Aledia. The company also continued the construction of its production site in Champagnier<sup>12</sup>; the first equipment will be installed in 2023; the first building will cover 5000 m<sup>2</sup> and few hundred jobs will be created.

"Aledia's know-how is nanowires. We implant them on silicon gallium nitride to develop three types of products. The first product we address is a mono-color 2D product, what we call "blu", explains Muriel Dupont, head of R&D activities at Aledia. By integrating the knowhow developed with Nanoelec, Aledia intends to develop RGB smartpixels on the same CMOS wafer in order to acquire expertise in a more powerful technology in terms of image quality. "Of course, all of this will require considerable volume, we are currently working on 200mm silicon wafers but our goal is to be able to develop 300mm technology to ensure large production volumes at a competitive cost", Muriel Dupont adds.

Muriel Dupont, head of R&D activities at Aledia, during the Nanoelec 2022 General Assembly © Cédrine Tresca/CEA

### Building the factory scale

Production building almost completed

## Microled receives an award

François Templier, senior expert at CEA-Leti and director of the Nanoelec/Displed program, and Marc Rabarot, engineer at CEA-Leti, won CEA's 'My invention in 3 minutes'<sup>13</sup> Challenge: their invention relates to the microLED display technology and unlocks the pixel size limitation.

In a microLED display, each pixel is composed of a tiny LED that emits its own light. Unlike LCD displays, which use a backlight and color filters to produce images, microLED displays emit light directly from each pixel, allowing for more precise and vibrant colors, deeper blacks, and higher contrast ratios.