Fête de la science 2025

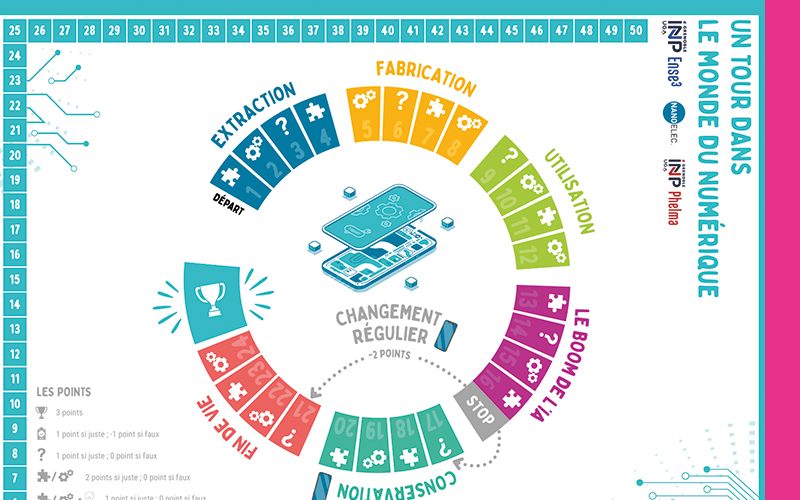

Un tour dans le monde du numérique

Les 7 et 9 octobre 2025, l’IRT Nanoelec et Grenoble INP – UGA, (Phelma et Ense3) ont pris part au Parvis des sciences, événement grenoblois de culture scientifique, en présentant un jeu de plateau original sur le numérique responsable.

Date

07 octobre 2025

09 octobre 2025

Lieu

Grenoble