Afin de pouvoir traiter l’augmentation massive de données, les circuits se complexifient. Pour les applications de type serveur ou « big-data », il est proposé d’associer efficacement différentes technologies et des plusieurs puces, permettant de créer des systèmes plus complexes et plus efficaces. Les quantités d’interconnexions sont de plus en plus importantes, avec des surfaces de plus en plus petites. L’utilisation d’un interposeur silicium actif, permet d’intégrer des couches de redistribution à haute résolution, des composants aux technologies avancées et également des parties de circuits produites avec des technologies éprouvées.

Dans ce démonstrateur appelé « Intact », nous proposons un partitionnement du circuit multi-cœurs en utilisant un interposeur actif.

Ce projet ayant pour nom IntAct fait partie intégrante du programme Nanoelec/Intégration 3D.

Les avantages de ce partitionnement 3D en interposeur actif sont les suivants :

- Gain en rendement en partitionnant le circuit en petits circuits qui sont testés et sélectionnés avant assemblage. Le rendement et le coût du système complet est diminué.

- Le circuit est réalisé dans des technologies hétérogènes : technologie agressive pour les cœurs de calcul FDSOI 28 nm, technologie mature 65 nm pour l’interposeur actif, ce qui diminue les coûts, avec un bon rendement et un taux de remplissage volontairement faible, et technologies 3D agressives pour offrir un bon taux d’interconnexions 3D.

- Avec un interposeur actif il est possible de rajouter dans l’interposeur des fonctionnalités avancées telles que : gestion de l’alimentation, interconnections rapide puce à puces, gestion de l’infrastructure circuit (horloge, reset, test, moniteurs), IO rapide vers l’extérieur du circuit.

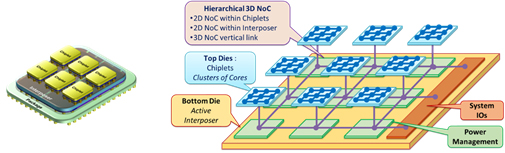

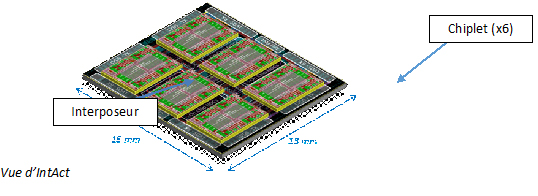

Dans ce contexte, le circuit IntAct est un circuit 3D composé de 6 puces appelées « chiplets » FDSOI 28 nm, contenant chacune 4 groupes avec 4 cœurs de calcul MIPS-32bits, et offrant une hiérarchie mémoire avec trois niveaux de cache cohérents. Ces puces sont assemblées en 3D sur un interposeur actif dans une technologie mature 65 nm, intégrant des fonctions de communication, de gestion d’alimentation (un nouveau bloc), de test et de diagnostic (stress, thermique, etc). Les fonctions de communications (à savoir un « NOC – Network-on-Chip » hiérarchique 3D), sont issues des travaux du précédent démonstrateur 3DNOC.

Le circuit InTact est réalisé avec une technologie 3D avec un pas d’interconnexion agressif 20 µm en architecture « Face à Face » pour des micro-billes, 40 µm de pas pour les TSV (« Trough Silicon Vias ») avec un facteur de forme important de 10:1 et du routage en face arrière.

Les microbilles au pas de 20 µm offrent une communication de chiplet à chiplet de faible consommation et large bande passante, à travers l’interposeur. L’interposeur comprend 150 000 microbilles, dont 30 000 dédiées aux interconnexions de chiplet à chiplet, le reste étant utilisé pour la gestion des alimentations. Il est attendu une bande passante totale de l’ordre de 370 GBytes/seconde.

Quant à la connexion vers l’extérieur à travers le substrat organique BGA (Ball Grid Array), 14 000 TSV (connexions électriques) dans l’interposeur sont nécessaires.

La puissance de calcul estimée est de 100 GOPS (GOPS : Giga Operations/seconde) à 20Watts, dans des conditions d’utilisation typiques.

Grâce à ce type de partitionnement, des gains conséquents en efficacité énergétique sont attendus : i) distance de communication réduite grâce à la 3D, ii) rapprochement de la gestion de la consommation au plus proche de la charge de calcul.

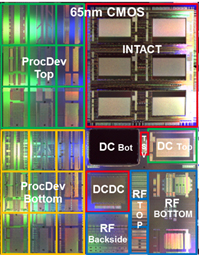

Réticule ITAC, contenant le circuit INTACT et les structures de test associées

Au-delà du circuit Intact (démonstrateur fonctionnel), le réticule contient ainsi des structures de test pour le développement de la technologie, la caractérisation électrique et RF et les études d’assemblage, de fiabilité, de thermomécanique et de thermique.

Les premiers résultats des études technologiques sont d’ores et déjà publiés, d’autres sont à venir. Quant au démonstrateur, des résultats fonctionnels et applicatifs sont prévus à la fin d’année 2018. Ils permettront à Nanoelec de se positionner comme un acteur majeur dans les développements d’intégration 3D à base de chiplet.