L’intégration 3D est, depuis 5 ans, devenue progressivement un standard pour les capteurs d’image basse consommation. L’objectif est de fabriquer en parallèle un circuit de traitement en technologie CMOS et un circuit capteur d’images, puis de les associer de manière la plus proche possible l’un de l’autre.

L’intégration 3D permet en effet d’adjoindre au capteur une unité logique de calcul capable de traiter le signal (traitement HDR, reconnaissance de personnes…) au plus près de la source.

Loin de se restreindre aux applications mobiles initialement visées, c’est désormais toute une gamme d’applications, notamment automobile, qui voit en ce type d’intégration des possibilités de réduction de facteur de forme ou de fonctionnalités ajoutées tout en maintenant une faible consommation.

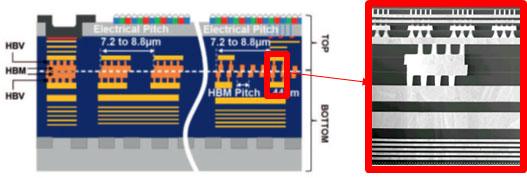

Parmi le panel de technologies 3D possibles, le collage direct hybride présente à la fois les avantages d’assembler en plaque à plaque (cadence augmentée et facilité de poursuivre l’intégration après collage en fonderie) sans ajout de matière (fiabilité augmentée et gestion thermique optimisée), et de permettre d’atteindre des plots d’interconnexion avec un pas largement inférieur à 10µm.

Après avoir développé cette brique technologique, les partenaires du programme 3D de IRT Nanoelec ont mis en commun leurs expertises afin de concevoir, développer et tester le démonstrateur Harmony.

Ce démonstrateur, illustré ci-dessous, a été conçu avec un pas de répétition au niveau de l’interface de collage de 1.44 µm. Un pas d’interconnexion aussi faible se justifie notamment par le besoin d’augmenter le nombre d’interconnexions entre les deux circuits et/ou de s’approcher au plus près des pas des pixels du capteur d’image. La coupe à droite, ci-dessous, représente un plot de connexion de l’ordre de 0,5 µm².

Après avoir relevé l’ensemble des enjeux soulevés par cette intégration, notamment concernant la préparation des surfaces avant collage, ou bien encore la précision d’assemblage des plaques (typiquement inférieure à +/-200nm pour des plaques de diamètre 300mm), le démonstrateur a été découpé et assemblé, pour un ensemble de tests électriques et optiques. La robustesse de l’intégration a également été éprouvée au travers de tests de fiabilité.

L’ensemble de ces tests s’est révélé extrêmement satisfaisant. Cette 1ère mondiale positionne l’IRT Nanoelec et ses partenaires en amont de l’état de l’art de la R&D dans ce domaine.

Pour finir, la photographie ci-dessous, prise avec un échantillon Harmony, démontre la fonctionnalité du capteur d’image, dont les performances s’avèrent en ligne avec les spécifications initiales.

Ces résultats de tout premier plan ont été couronnés par l’acceptation d’un papier à la très renommée conférence IEDM (International Electron Devices Meeting) en décembre 2018 à San Francisco.

Forts de cette réussite, les partenaires poursuivent leurs travaux vers des capteurs d’image toujours plus performants, en cherchant à minimiser la consommation tout en apportant de nouvelles fonctionnalités, ouvrant la voie à une nouvelle génération de capteurs d’image intelligents.