Intel Corporation annonce (COMMUNIQUE DE PRESSE | 27.10.2020) une nouvelle collaboration avec le CEA-Leti sur les technologies d’intégration 3D de microprocesseurs pour la conception de puces électroniques, en particulier pour le secteur du calcul haute performance (HPC). La recherche sera focalisée sur la réduction de taille des puces, l’optimisation des technologies d’interconnexion entre les composants des microprocesseurs et les nouvelles technologies de collage et d’empilements de composants sur plaquettes de silicium. Au CEA-Leti, ces travaux prennent appui entre autre sur le programme Intégration 3D de l’IRT Nanoelec.

Selon Intel et le CEA-Leti, les technologies avancées d’intégration 3D et de packaging renforceront les solutions informatiques dans le domaine du HPC, souligne Severine Cheramy, ingénieure chargée du développement de l’intégration 3D au CEA-Leti et Directrice du programme Intégration 3D de Nanoelec. Cette collaboration va permettra d’accélérer notre feuille de route d’intégration hétérogène grâce à de larges bases communes de connaissances et de savoir faire sur les technologies 3D.

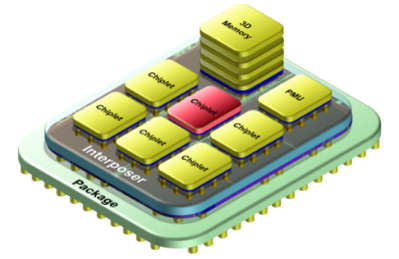

Chiplet assemblées sur un interposeur silicium Schéma de principe d’un assemblage hétérogène