« IntAct, l’approche « Chiplet sur Interposeur Actif » de l’IRT Nanoelec

Dans le contexte des architectures multi-cœur, visant les applications de type serveurs/micro-serveurs dans le domaine du HPC (HIGH ¨Performance Computing), ou offrant des accélérateurs matériels (domaine de l’embarqué), le besoin de performance impose de concevoir des circuits de plus en plus évolutifs en nombre de cœurs, avec des circuits de plus en plus grands en surface, au détriment des rendements de fabrication.

Le choix des partenaires de l’IRT Nanoelec s’est porté sur une intégration 3D à base de silicium actif. Il permet de bénéficier de tous les avantages en terme de performance apportée par le silicium (en comparaison de technologies de packaging avancé), si tant est que l’on utilise intelligemment cette plateforme silicium pour y embarquer des composants actifs, transistors aujourd’hui, guides optiques demain.

Le partitionnement du circuit en 3 dimensions, à base « d’interposeur » actif, permet d’une part de le diviser en chiplets, ou « micro-puces », homogènes, pour gagner en complexité tout en préservant les rendements de fabrication et d’autre part d’apporter des fonctionnalités avancées dans l’interposeur actif telles que la gestion de l’alimentation et des infrastructures de communication inter-circuits.

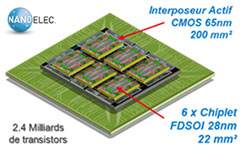

Le démonstrateur IntAct démontre la pertinence d’une architecture 3DIC de ce type pour les applications HPC.

IntAct permet d’assembler un système multi-cœur de 96 cœurs MIPS 32-bits, offrant une puissance de 96 GOPS. L’interposeur est composé, entre autres, des nouveaux éléments différenciant suivants : des Plots de communication 3D avancés, synchrones et asynchrones offrant respectivement 800 MHz et 300 MHz de bande passante ; des convertisseurs DC-DC, sans aucun élément passif externe, permettant d’alimenter à la demande chaque chiplet de manière indépendante, et ce à travers l’interposeur.

Ce circuit 3D repose sur des technologies avancées de l’IRT: un interposeur grande surface actif avec intégration de TSV (« Through Silicon Vias ») et une interconnexion puce à puce à un pas de 20µm. L’interposeur a une surface de 220 mm2, pour 15 000 connexions face avant, avec 15 000 TSV, pour un budget de consommation estimé à 10 Watts. Les TSV ont un diamètre de 10µm sur une profondeur de 100µm. L’option de TSV retenue, le « TSV-Middle », est une connexion verticale traversant le silicium, remplie de cuivre, qui a la particularité d’être insérée entre le FEOL (partie « chaude » de la fabrication du circuit intégré) et le BEOL (partie des interconnexions) d’une technologie de fabrication de circuits intégrés. Ce positionnement permet l’obtention de TSV à fort facteur de forme (rapport hauteur sur largeur – typiquement 10 :1) mais requiert des équipements et des procédés, voire des matériaux, nouveaux par rapport à ceux classiquement présents dans un procédé de fabrication de circuit CMOS. Les travaux des membres du consortium ont largement bénéficié des partenariats associés au programme avec Aveni, Orbotech et Applied Materials, notamment pour la maîtrise du remplissage des TSV.

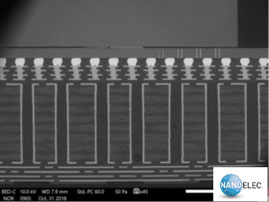

L’assemblage du circuit était lui-même un défi dû principalement au pas très resserré des interconnexions entre les chiplets et l’interposeur. Les interconnexions par micro-piliers de cuivre au pas de 20µm, diminuant par 2 le pas utilisé actuellement en production, ont été tout d’abord validées par les partenaires de l’IRT. Ensuite, ce sont les études de report des composants en puce-à-plaque et les études de remplissage de l’espace entre la puce et la plaque, qui ont été menées. Les études de fiabilité ont enfin confirmé les excellents résultats électriques après report, grâce à des structures de test embarquées avec le démonstrateur IntAct.

L’ensemble de l’intégration de ce démonstrateur a été présenté lors de la conférence IEEE ECTC à Las Vegas en 2019 qui est un événement majeur dans le domaine de l’intégration 3D et du packaging des circuits intégrés.

|

|

| Coupe de l’assemblage 3D | Vue optique après assemblage final |

En termes de positionnement par rapport à l’état de l’art mondial, l’IRT a ainsi présenté des résultats tout à fait en ligne avec les exigences des applications « Computing. Une annonce récente d’INTEL fin 2018 avec la technologie FOVEROS, de même que le lancement d’un programme DARPA aux USA appelé « CHIPS », démontrent la pertinence des choix de l’IRT Nanoelec.

Forts de cette réussite, les partenaires poursuivent leurs travaux notamment avec la réalisation de tests applicatifs grâce à une carte d’application elle aussi développée dans le programme. Les partenaires ont l’intention de proposer ces résultats à de prestigieuses conférences dans l’année qui vient, et de valoriser ces travaux auprès des acteurs mondiaux du domaine du « computing ».