Tom Daspit (Product Marketing Manager, Mentor Graphics) évoque les outils de conception et de vérification pour les applications photoniques sur silicium.

Depuis sa création en 2012, Nanoelec a développé des recherches novatrices dans le secteur de la micro- et de la nanoélectronique, qui ont abouti à des démonstrateurs et des plateformes technologiques de pointe. Mentor, une filiale de Siemens, seul partenaire de Nanoelec en matière d’automatisation de la conception électronique (EDA), propose des outils de conception et de vérification pour la communauté des designers de l’institut de recherche. En plus de fournir ce précieux soutien, Mentor utilise également les retours de la communauté pour améliorer continuellement ses outils de conception quant à leurs performances lorsqu’ils sont utilisés sur les démonstrateurs et des plateformes les plus avancées. Tom Daspit (Product Marketing Manager, Mentor Graphics) évoque les outils de conception et de vérification pour les applications photoniques sur silicium.

Pourquoi les outils de conception sont-ils essentiels pour permettre la croissance dans la conception photonique ?

La photonique sur silicium présente un large éventail d’applications dans le centre de données, le calcul intensif (HPC) et les télécommunications. L’exploitation prometteuse de techniques de fabrication à haut volume et à faible coût dans la fabrication des circuits photoniques sur silicium pourrait permettre d’étendre la gamme des applications photoniques aux capteurs intelligents, et de cibler ainsi de nouveaux espaces tels les véhicules autonomes, les robots autonomes, les soins de santé, etc.

L’extension et l’exploitation des outils actuels de conception sur silicium, en vue d’intégrer de manière transparente et productive des fonctions photoniques avec une électronique basée sur CMOS, jouent un rôle déterminant pour les circuits photoniques à haut volume et hautes performances.

Quelles sont les principales méthodologies pour la conception d’architecture dans la photonique ?

Il existe aujourd’hui deux principales méthodologies de conception photonique : l’implantation scriptée et l’implantation personnalisée. Toutes deux s’avèrent efficaces pour la création de conceptions de faibles dimensions, mais elles deviennent inefficaces dès lors que l’on passe de 10 à 100, puis à plus de 1000 composants dans la conception. La conception photonique peut bénéficier des améliorations de l’industrie depuis plus de quarante ans dans la technologie de traitement, les méthodologies et les outils de conception des circuits intégrés. Enfin, la disponibilité d’un plus grand nombre de procédés photoniques devrait permettre de prendre en charge des conceptions de dimensions nettement supérieures.

Les dimensions des circuits imprimés sont passées de quelques milliers de transistors à plusieurs millions, pour atteindre plusieurs milliards de transistors dans les processeurs actuels. Cette croissance a été rendue possible par l’automatisation des opérations de conception des circuits imprimés. L’automatisation n’est pas simplement centrée sur les outils, elle repose aussi sur la méthodologie de conception sous-jacente qui la prend en charge. LEF/DEF, une norme qui résume les données à l’ensemble minimal nécessaire, illustre parfaitement la place occupée et le chemin suivi par le numérique. LEF/DEF est dérivée d’une méthodologie de conception de cellules standard, lesquelles sont créées à partir de transistors individuels construits à partir des données d’un kit de conception de procédés (PDK, Process Design Kit).

Quelle est l’avancée rendue possible par le LightSuite Photonic Compiler de Mentor ?

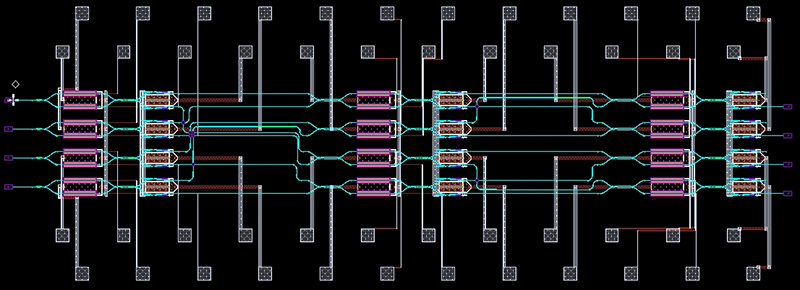

Mentor aborde la photonique avec la prise en charge d’outils d’implantation automatisés et personnalisés. Le leader de l’EDA se concentre sur la réalisation d’une automatisation de pointe de l’implantation avec son LightSuite Photonic Compiler. Le premier exemple ci-dessous est un interrupteur 4×4. L’implantation a été créée automatiquement en moins de 5 minutes.

Faites maintenant évoluer cet interrupteur vers un interrupteur 16×16. La complexité d’un tel changement exige un tracé optique et électrique complexe. Cette implantation propre de DRC a été mise en œuvre en 85 minutes. L’implantation manuelle d’une conception d’une telle dimension nécessiterait des mois de travail. © Mentor Graphics

Le LightSuite Photonic Compiler de Mentor crée automatiquement une implantation photonique de DRC propre, y compris le tracé électrique correspondant. La puce d’interface associée à cette conception d’interrupteur a un ordre de modification technique (OMT) — une modification est forcée dans le brochage, ce qui nécessite également un changement de conception dans la puce d’interface correspondante. Cet OMT exige la modification d’environ 20 % des plots électriques. Cela ne pose pas de problème avec le LightSuite Photonic Compiler de Mentor, qui peut générer une nouvelle implantation dans ce même délai de 85 minutes. © Mentor Graphics