Caractérisation par les grands instruments

Les grands instruments offrent des performances inégalées pour la caractérisation avancée des objets électroniques. Cependant, l’accès à ces instruments a été conçu pour des utilisateurs experts, ce qui est fréquemment le cas chez les chercheurs universitaires, mais moins chez les utilisateurs industriels.

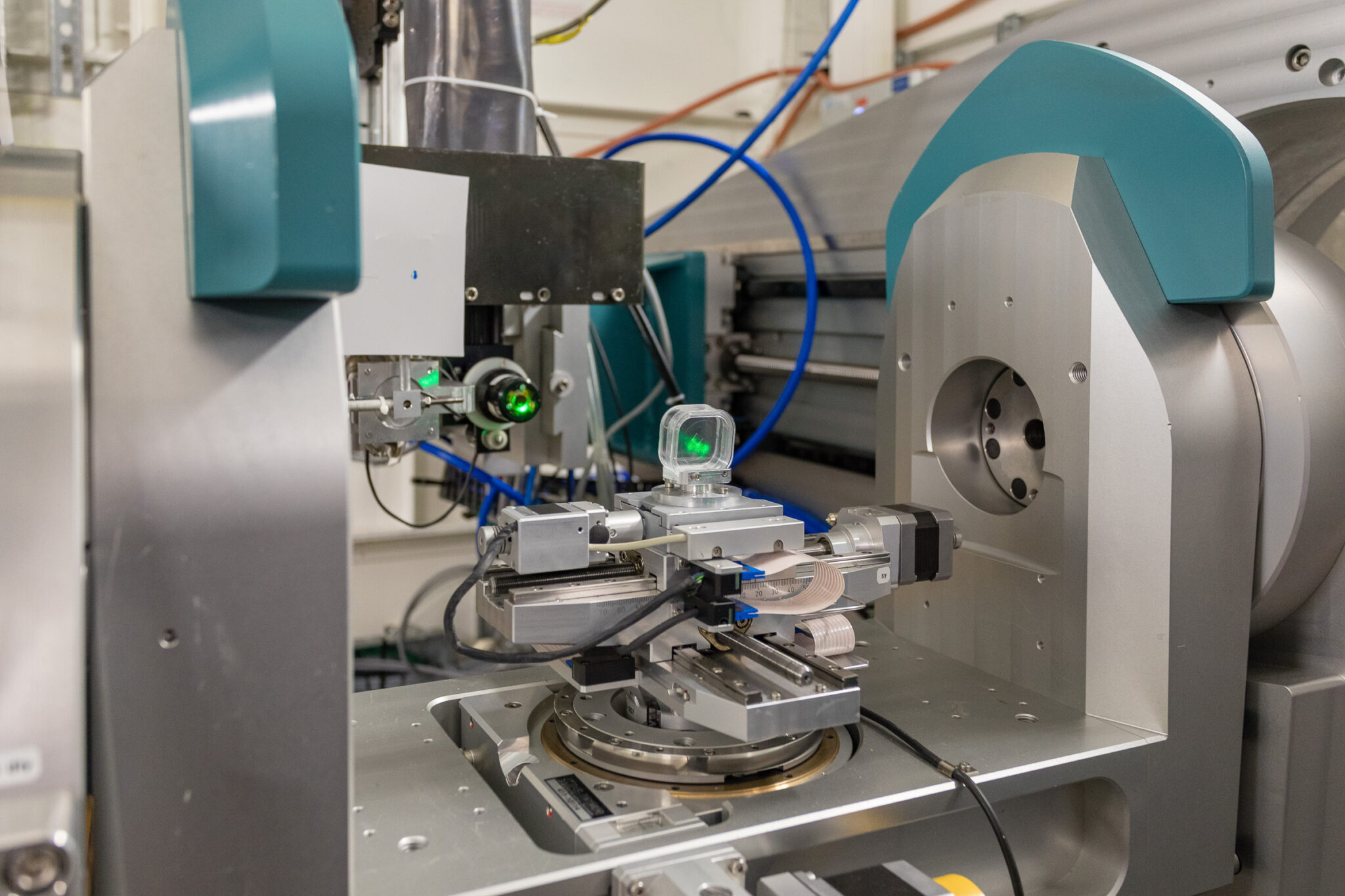

Grâce au programme Nanoelec/Characterisation, les entreprises industrielles et les chercheurs ont accès à des outils de classe mondiale pour étudier les effets des rayonnements ionisants sur les dispositifs et systèmes électroniques, caractériser les propriétés de leurs matériaux et inspecter leurs composants, contribuant ainsi à la qualité de leurs produits et processus. Grâce au pouvoir de pénétration élevé des neutrons et des rayons X synchrotron, ces évaluations peuvent être réalisées de manière non destructive, sans avoir à ouvrir ou endommager les objets, et dans de nombreux cas pendant leur fonctionnement.

PAC-G

Une passerelle vers les instruments à grande échelle dédiés aux besoins de l’industrie électronique

PAC-G offre un point d’accès unique à des installations à grande échelle telles que les sources de rayonnement synchrotron et neutronique grâce à un service rapide et économique adapté à l’innovation dans le domaine de l’électronique.

PAC-G offre à l’industrie électronique un accès rapide et facile à certaines des installations de caractérisation les plus avancées au monde. Dans le cadre du programme Nanoelec/Carac, PAC-G propose également un portefeuille extrêmement large de techniques de caractérisation individuelles mais complémentaires. Un pipeline dédié a été mis en place pour garantir que toutes les preuves de concept validées dans le cadre du programme soient transférées et adoptées avec succès par les partenaires de R&D concernés.