Optimizing Performance and Environmental Impact: The Challenge of 3D Chips

To develop eco-design capabilities for electronic components, the CEA and the IRT Nanoelec are equipping themselves with life cycle assessment (LCA) and environmental impact analysis tools. Their very first model, applied to the most advanced electronic architectures, will be presented at IEEE SusTech 2026, April 19-22, 2026, California/USA. Their initial calculations demonstrate that chip stacking strategies can help reduce the environmental impact of components if they contribute to develop more compact components.

In microelectronics, the consideration of environmental impact criteria, and even societal criteria, requires the adaptation of design and development processes for new components. The scientific community is therefore seeking to equip itself with suitable tools to facilitate life cycle assessments (LCA) in order to systematize and standardize impact assessment methods from the component design phase.

The approach is often difficult to implement due to gaps or uncertainties in the essential data sets for life cycle inventory. The scientific community also lacks powerful and standardized tools for calculations and comparisons.

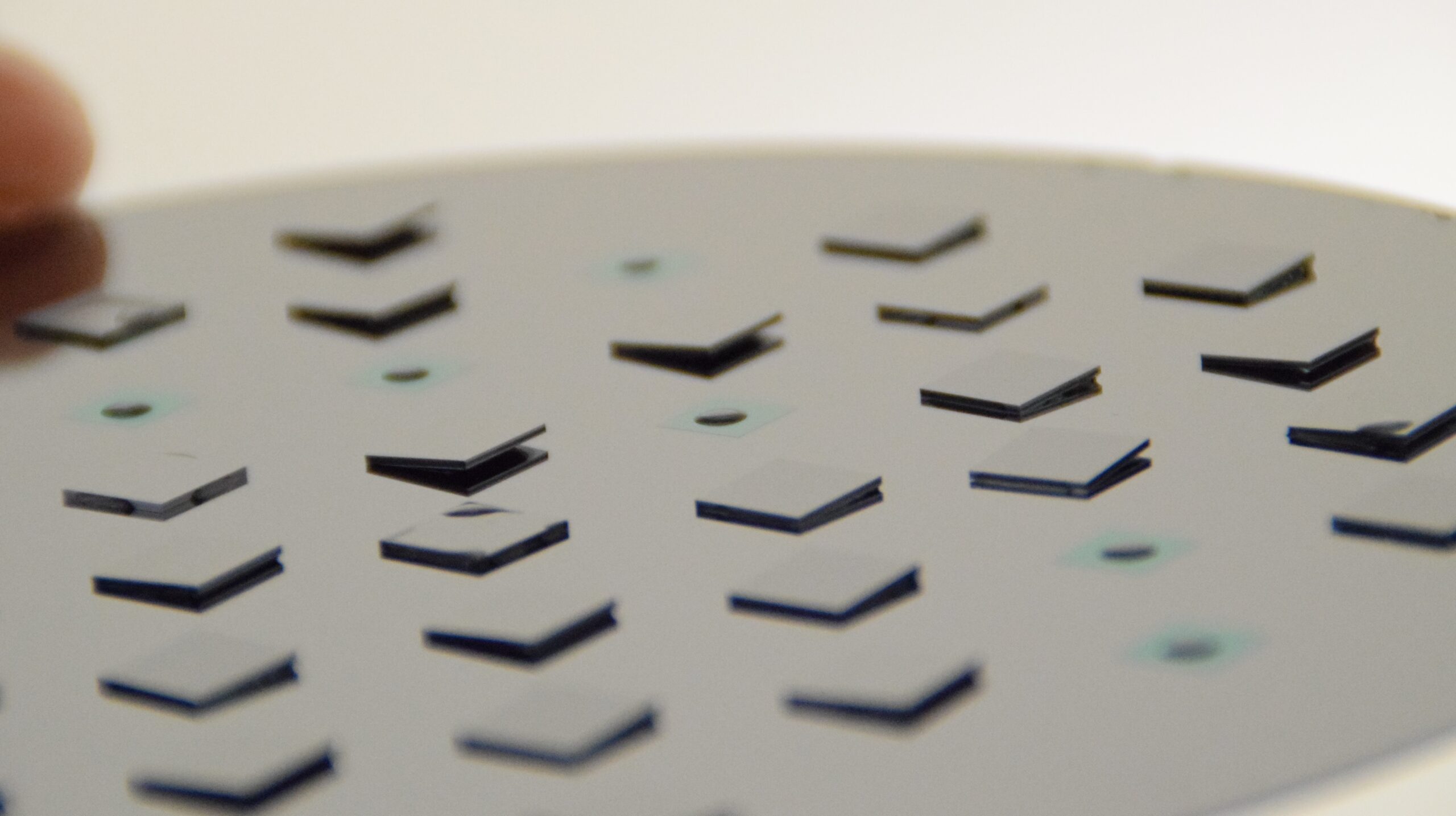

« This difficulty is particularly strong for components integrating multi-chip assemblies, » notes Mathilde Billaud, a CEA researcher and co-author of an article presented at the IEEE SusTech 2026 conference[1]. « Therefore, to help design 3D stacked multi-chip assemblies, we have designed and developed a new, unprecedented LCA model that requires only a limited set of design parameters. »

The very first comparative LCA of three image sensor architectures

With this LCA calculation model, the CEA team, as part of a program supported and funded by IRT Nanoelec and the European project EECONE, publishes the very first comparative LCA of three multi-layer CMOS image sensor (CIS) architectures[2]. « Our results show that the environmental impacts of multi-layer CIS are primarily linked to the manufacturing of the CMOS circuit. Furthermore, we found that the most energy-efficient CIS cannot compensate for its higher manufacturing impacts until after a long period of component use,” explains Maxime Peralta, a CEA researcher and first author of the publication. “We also demonstrate that stacking a third layer of silicon can reduce manufacturing impacts by reducing the size of the chip. Thus, the search for a more compact electronic architecture appears to be a virtuous path in terms of the environment.

Open source

The proposed LCA model and 3D integration environmental data are published in open source to facilitate future work and to contribute to the widespread dissemination of these impact assessment methods beyond the PPAC[1] figure of merit. The publication includes the LCA results of three technological building blocks necessary for 3D integration (wafer thinning, hybrid bonding, and high-density TSV).

« Our model shows that the manufacturing of CMOS circuits is generally the first source of impact, thus penalizing large chips and the stacking of additional circuit layers, which also penalizes the manufacturing yield, » continues Maxime Peralta. « Nevertheless, stacking a third layer of silicon can help reduce the total silicon area and the environmental impacts of manufacturing. The additional manufacturing steps required for 3D integration processes result in minimal environmental costs. »

Accélérer l’estimation des impacts environnementaux

These conclusions confirm previous studies, but for the first time, they are based on verifiable experimental results across multiple environmental indicators. Since the CMOS part is the most impactful, specific in-depth LCA studies are being conducted in parallel on the manufacturing of FD-SOI CMOS chips as part of the FAMES pilot line. These studies rely on the collection of precise information about the manufacturing processes to identify the contribution of each process and compare manufacturing alternatives.

Such a modeling approach can now be easily used to define new components as it requires only a limited set of design parameters. “Thus, we accelerate the estimation of the environmental impacts of components during the design phase, opening the door to eco-design approaches,”** emphasizes Maxime Peralta.

[1] PPAC, for “Power, Performance, Area & Cost,” is a figure of merit for the optimization of new electronic components, based solely on technological criteria.

[1] IEEE Conference on Technologies for Sustainability (SusTech 2026, April 19-22, 2026, California/USA)

[2] The calculations are performed for three different CIS described in the literature.