NANO ELEC.

# Scientific & technical highlights

# AGENDA

## P.4 Identity of the institute

Exploring the future of electronics

## P.16 Sustainable development

P.22 Cross-cutting initiatives for sustainable electronics

P.24 Parity and attractiveness of the microelectronics industry

P.26 Posters to promote the sector

## P.6 Trends notes: sovereignty & sustainability

P.6 Bringing together all the sector's innovation actors

P.7 Paving the way for sovereign and sustainable electronics

P.8 Giving meaning to our sector

## Images & Photons

### P.28 Heterogeneous integration

### P.30 Smart Imager

From imaging to visioning

P.32 Connecting layers by sharpening through silicon via HD-TSV are now available at industry level

P.33 In-sensor computing for event-based imaging

P.34 Date Conference 2024

P.35 Characterization, Modeling, and Reliability for Direct Copper Interconnection

P.35 Copper interconnections within cryogenic systems

### P.36 Displed

Towards Display Technology Leadership in Europe

P.37 The first LED light

P.38 Mass Transfer

P.42 Vacuum bonding of LED chips

P.42 The move to flexible displays

P.42 Nanoscale layer etching

P.43 Blue digital LED product

P.43 Full-color unit demonstrator

### P.46 Photonic sensors

New opportunities based on large-scale 300 mm silicon photonic technologies

P.47 MZI based ethanol detection

P.48 Millimeter-length antennas for optical-phased arrays

P.48 Laser integration

P.49 GaAs for photonic and optoelectronic devices

P.52 Micro light-emitting diodes

P.52 Photonic interconnection for AI

## P.10 Events & conferences

P.33 In-sensor computing for event-based imaging

P.34 Date Conference 2024

P.35 Characterization, Modeling, and Reliability for Direct Copper Interconnection

P.35 Copper interconnections within cryogenic systems

## High performance computing

### P.56

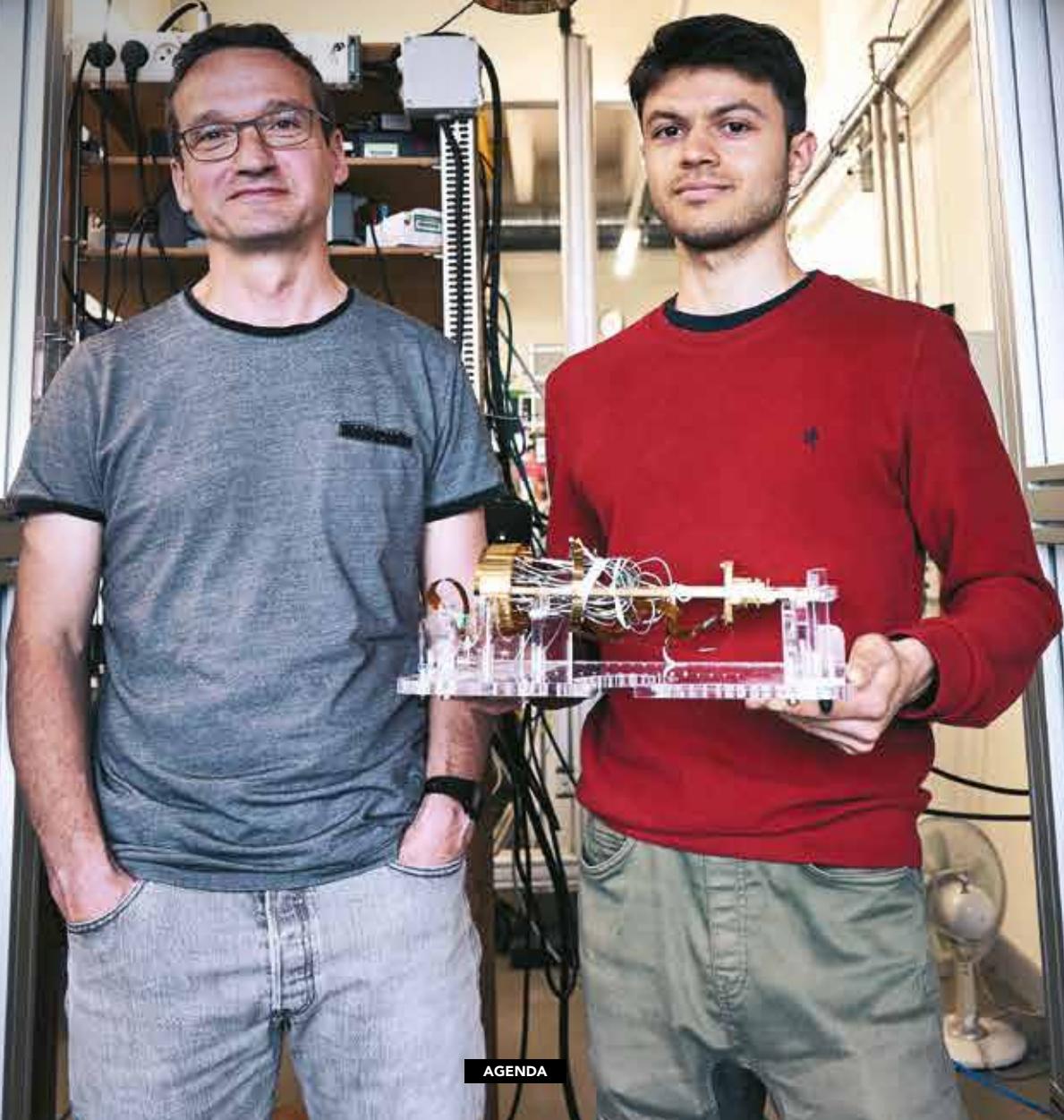

### Q-Loop

The road to the quantum computer

**P.57** Program kick-off

**P.57** First test vehicles for cryo TSV

**P.58** A drastic temperature challenge

**P.59** From qubit to supercomputing

**P.59** Cryo-CMOS

**P.61** Sound strategy to handle cryogenic thermal simulation

**P.61** QEC code

**P.61** Visibility of the program

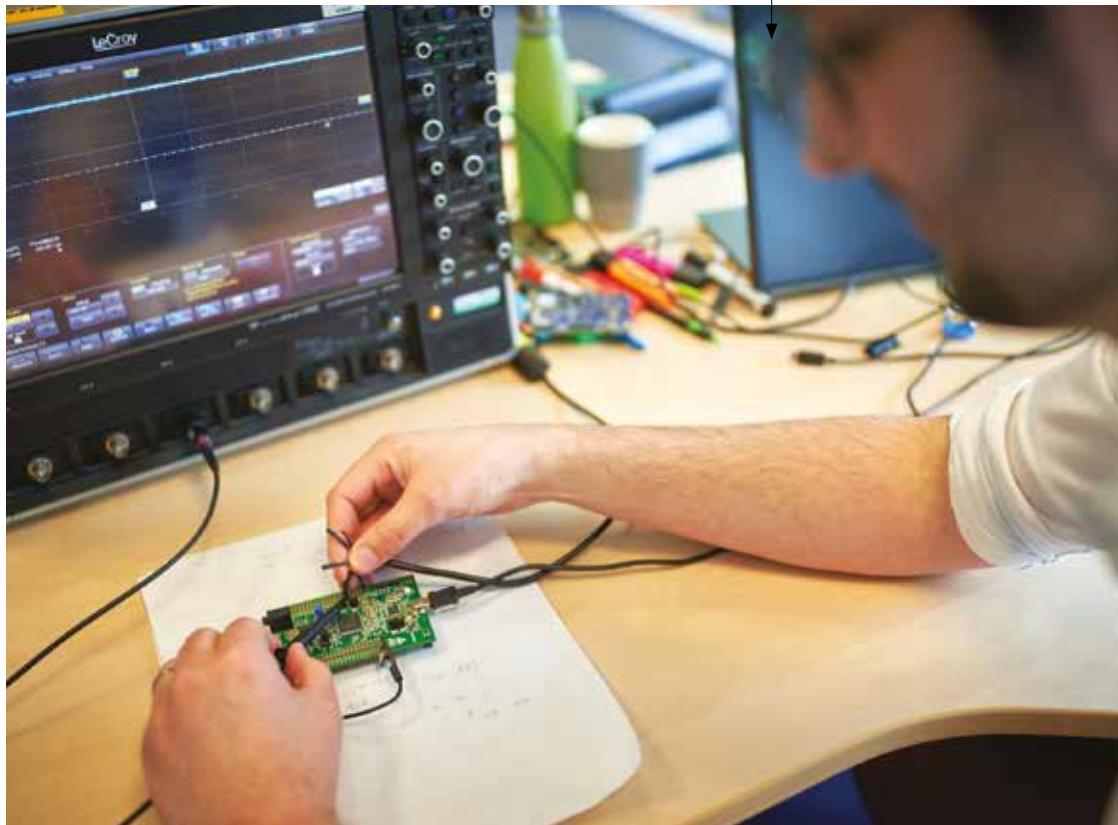

## Digital trust

### P.62

### Pulse

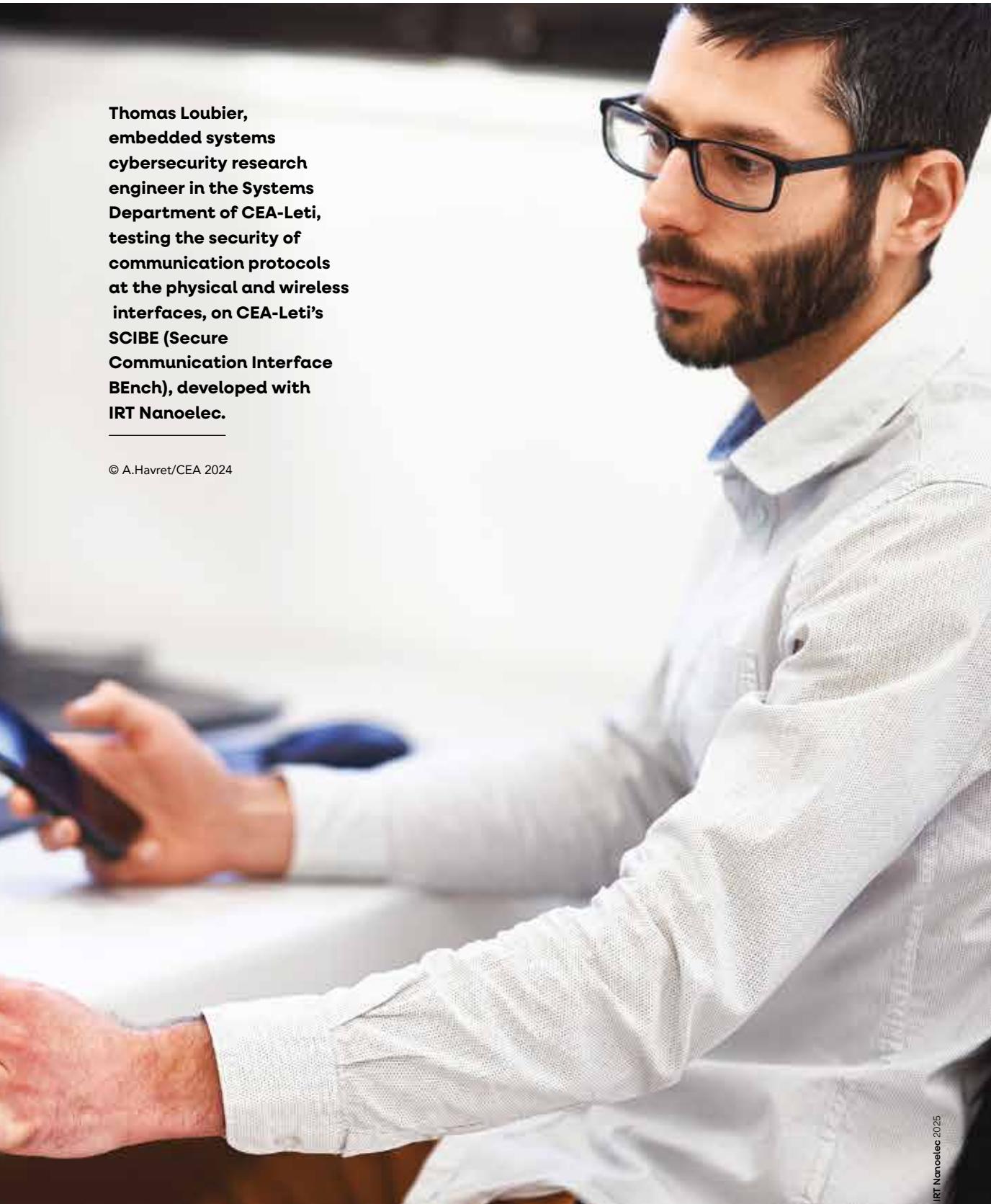

Cybersecurity is a major challenge for digital trust

**P.63** Pulse at international events

**P.66** PhDs at Pulse

**P.68** Safe and autonomous smart hoisting system

**P.69** Validated perception solutions for autonomous vehicles

**P.70** Digital identity management on a robotic system

**P.72** An intrinsically secure processor

**P.73** Secure implementation of post-quantum cryptography

### P.74

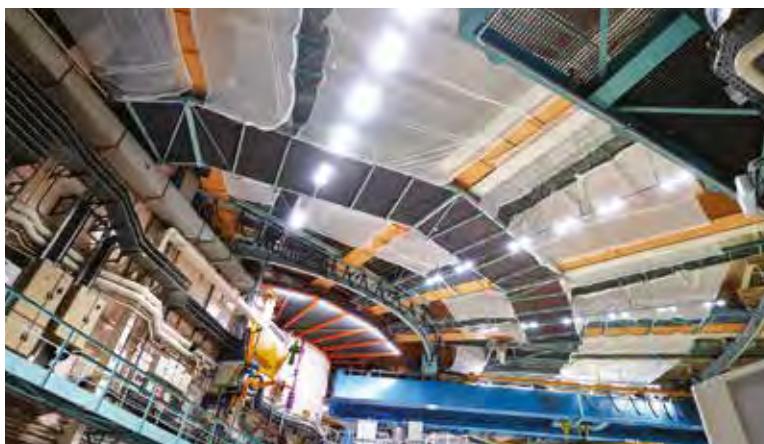

### Characterization

Large scale instruments for characterization

**P.75** Correlative Material characterization

**P.76** Soft errors caused by neutron irradiation

**P.77** Neutron reflectometry for improved photolithography

**P.77** Emulating heavy ions irradiation on components through pulsed X-rays

**P.78** Testing hard coating for resins in photolithography

**P.79** Optical transceivers under heavy ions

**P.80** Single-Event Upsets Induced by Thermal Neutrons in SRAMs

**P.81** French reliability center

**P.81** A gateway to large-scale instruments dedicated to electronics industry needs

## Dissemination

### P.82

### Technology Dissemination

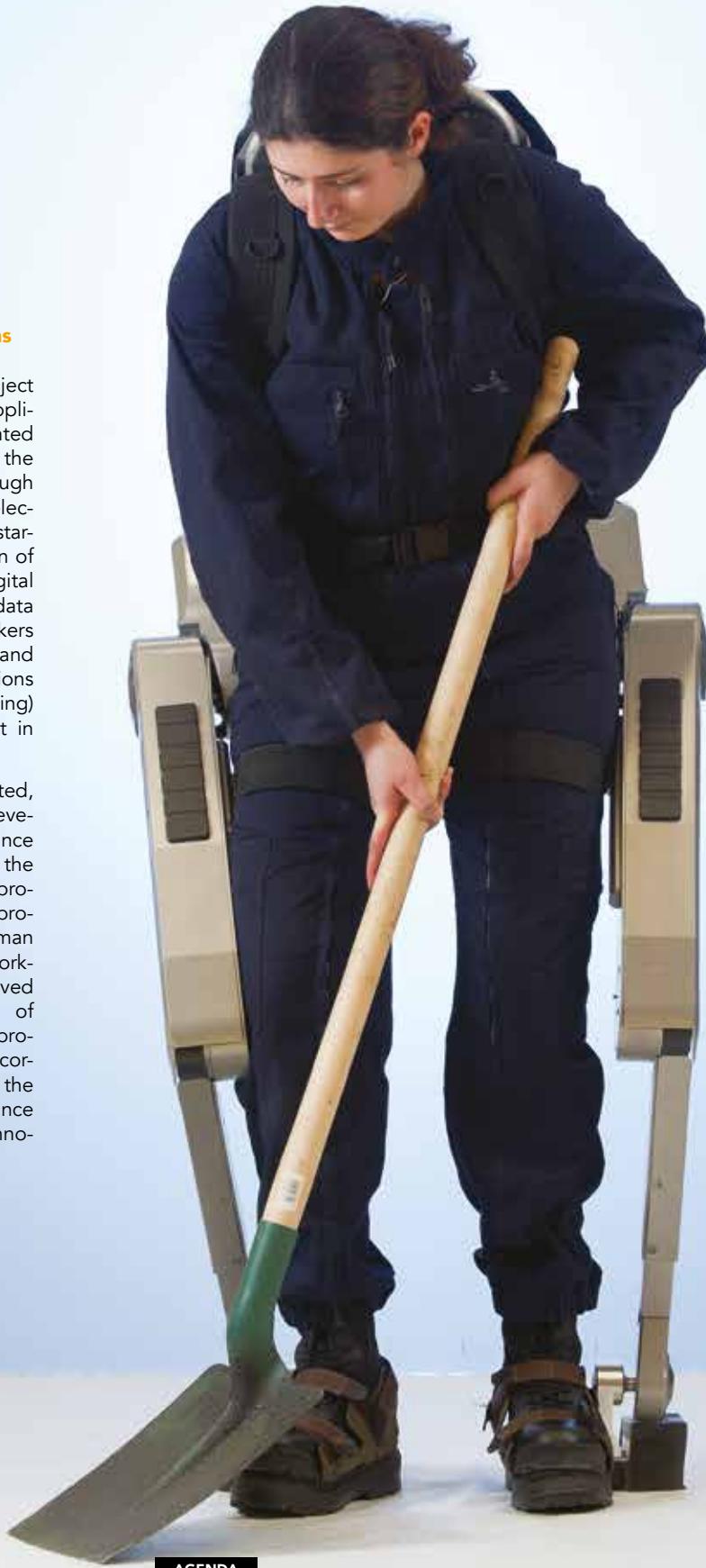

Sustainable integration of digital devices in SME processes

**P.83** Objective: Impact

### P.84 Easytech

**P.84** Lidars for the automotive sector

**P.84** A network of foot-powered sensors

**P.85** Waste heat

**P.85** A miniature broad-band antenna

**P.86** Electronics for music

**P.86** The need for a more integrated approach to eco-innovation

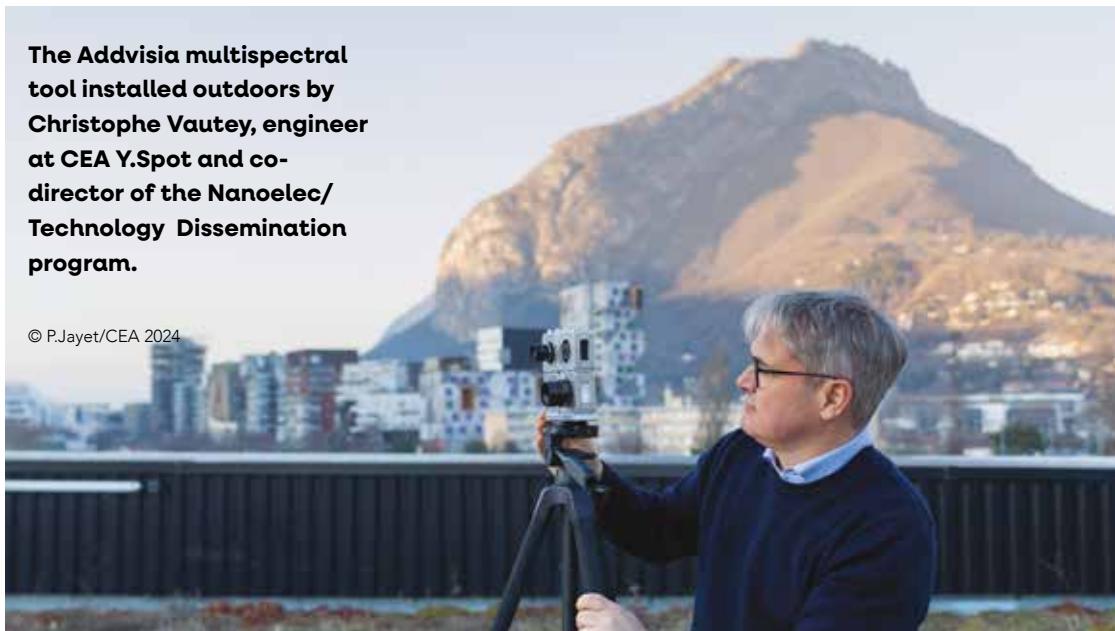

### P.87 System Lab/ Addvisia

**P.87** Displaying strata in the snowpack

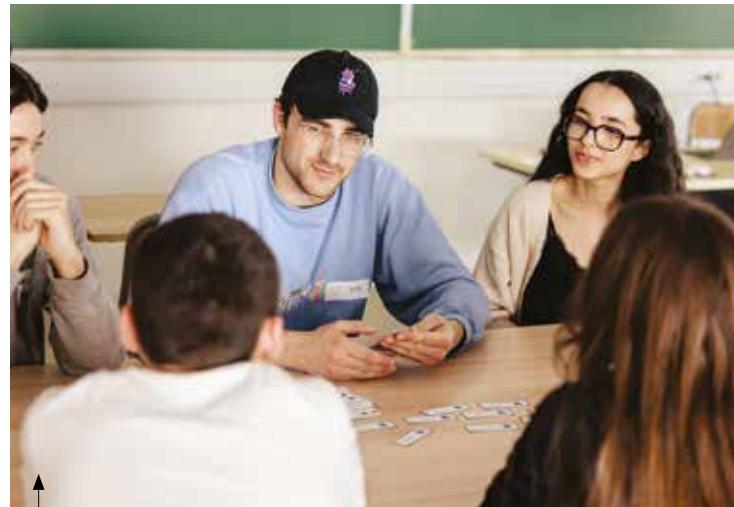

**P.88** The imaging game

**P.89** Biathlon tracker

**P.89** Movement capture and analysis in sport

### P.90

### Human capital & training design

Sustainable development as a driver of innovation

**P.91** Interactive Screens and the Rebound Effect

**P.93** The Addvisia platform adapted to a campaign for a commercial brand

**P.94** Raising awareness for a responsible digital world

**P.95** Hybridizing profiles on the impact of interactive displays

**P.95** Emerging pedagogical methods

# Exploring the future of electronics

IRT Nanoelec runs multi-partner programs to make the electronics industry more competitive and greener, and thus contribute to the sustainable development of society.

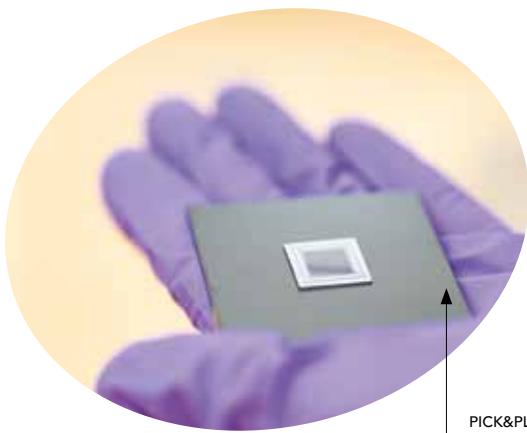

PICK&PLACE TOOL FOR MICROLED MASS TRANSFER

© O.Devise/CEA 2024

The Nanoelec technological research institute (IRT) is a consortium of private and public sector players, backed by CEA. Our mission is to help companies create value and enable their products to stand out on the digital transition stage.

Nanoelec contributes to the competitiveness of the electronics industry, in France and in Europe. Based in Grenoble, a world-class hub for research, innovation and production in its field, the Institute runs R&D programs built jointly by representatives from the academic and industrial worlds. These programs deal with the design and development of new processes, systems and components in the following fields:

- Images: new-generation of displays and imagers,

- Digital trust and frugality on connected objects and embedded AI

- High Performance Computing (via photonics and quantum computing)

- Characterization and resistance to radiation of components and systems by means of large instruments.

Nanoelec also designs training courses for emerging technologies and markets as well as technology dissemination programs for SMEs. We implement open innovation techniques as well as more conventional technological development methods.

Given the pervasive nature of digital technologies, Nanoelec is in contact with actors from all sectors ranging from goods to services, industry, infrastructures, and consumer products, as well as transportation, the environment and health.

Nanoelec is a member of FIT, a hub of technological research institutes (IRTs) and energy transition institutes (ITEs) set up by the French Government and financed by the France 2030 program (National Initiative for Investments for the Future). The network of institutes was created to pool academic and industrial players who could run collaborative R&D and innovation projects aimed at boosting the competitiveness of the French economy. •

***“A circle of trust to carry out responsible research and development programs to help businesses create value.”***

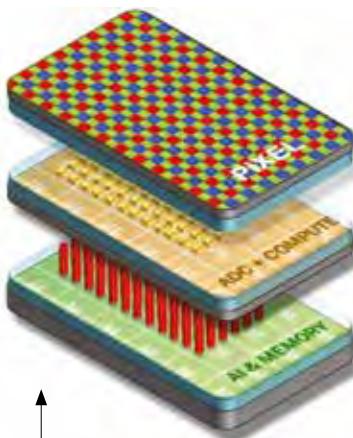

OPTIONS FOR A NEW ARCHITECTURE TO SUPPORT AI AT THE EDGE IN A DISRUPTIVE SMART IMAGER

© O. Devise/CEA 2024

**“Anticipating future human and technological needs in electronics.”**

## Innovation in microelectronics

- Carry out world-class collaborative R&D in selected areas to produce innovative components and embedded systems: imagers, displays, photonics on Si design & devices for quantum computing and digital trust & security

- Develop and transfer these technologies to create the electronic circuits and components of the future

- Give industry players access to development, prototyping and advanced characterization resources, including large EU instruments for research

## Technology dissemination

- Help businesses in the field of information and communication technologies meet the challenges of IoT through digital trust and security

- Provide expertise to help SMEs from various industrial sectors build new products and services with innovative components and embedded software

- Promote cooperation between SMEs, mid-caps and large companies

- Unveil new applications comprising environmental and social impact assessments through collaborative innovation

## Development of human capital

- Attract young people to jobs in electronics that contribute to sustainable development

- Work with partners on parity and workplace equality

- Design training courses to meet the current needs of the electronics business

- Anticipate future skills requirements in the sector: sustainability, cross-skills, social and professional communities for innovation

## NANOELEC AT A GLANCE

A consortium of

**21** public & private

members

as of December 2024

**352** associated partners

including **267** SMEs

since 2012

**€48M** average

annual budget

(2020-2024)

**784** scientific or

technical publications

& communications

since 2015

**258** patents and

**58** software filed

since 2012

**200** full-time jobs

Yearly average 2020-2024

# Trends notes: sovereignty & sustainability

IN 2024, NANOELEC LAUNCHED

THE Q-LOOP PROGRAM DEDICATE

TO THE DESIGN OF QUANTUM

COMPUTER

© A. Havret/CEA

S BASTIEN DAUV , DIRECTOR

OF CEA-LETI AND PRESIDENT

OF NANOELEC STEERING

COMMITTEE

© C. Tresca/CEA

“

**The Grenoble ecosystem is ready to take up the major challenges of the microelectronics transformation, with regard both to sovereignty and the ecological transition.**

## Bringing together all the sector’s innovation actors

by Sébastien Dauv 

In a geopolitical context that we all know to be tense and uncertain, the semiconductor sector is faced with significant challenges, in terms of both sovereignty and the ecological transition. With the Chips Act, Europe holds a strong hand in its dealings with the two main leaders in this field, Asia and the United States: the Chips Joint Undertaking (Chips JU) brings together the main European microelectronics innovation ecosystems. On the Fames pilot line run by CEA-Leti, we will be able to advance the various key technologies in our ecosystem, notably FD-SOI, to bring down the energy

consumption of embedded components, but also heterogeneous integration, which is vital to obtaining smarter and more frugal components.

In the French ecosystem, Nanoelec plays a crucial role in stimulating collaboration between the leading actors who are ready to take up the major challenges of the microelectronics transformation. In line with the slogan “Think global, act local,” the Institute brings together the sector’s innovation actors present in the Alpine region, along with everything they can bring to the table: a circle of trust enabling a wide variety of actors to share common goals, world-class technology platforms and unparalleled training resources to guarantee highly competitive human capital in the coming years. •

HUGUES METRAS,

DIRECTOR OF NANOELEC

© P. Jayet/CEA

## Paving the way for sovereign and sustainable electronics

by Hugues Metras

In 2024, we launched our Q-Loop quantum computer program, which is mobilizing 65 million euros over six years, to enable France to pave the way for qubit control systems and develop the technologies needed for quantum computer control and command. Ahead of the next financing tranche of the IRT Nanoelec (2026-2030), our Institute is already making profound changes

“

We will be

promoting

heterogeneous

integration

for imaging,

photonics and

computing.

1. Organized by Nanoelec with PEPR Electronique, the Microélectronique-UGA labex and the Pôle universitaire d'innovation (PUI) Grenoble-Alpes.

2. Creations by the students of the Brassart school with Teledyne E2V, and the Dauphiné libéré newspaper for the Tech&Fest 2025 festival

to its activities: sovereignty and sustainable development will be the main pillars of our future programs, in which we will promote heterogeneous integration for imaging, photonics and computing.

The advent of more sustainable and more responsible electronic and digital systems is also an increasingly significant aspect of our activity:

→ the very first national symposium on the subject<sup>1</sup>, in December 2024 in Grenoble, attracted more than 40 original contributions and 200 French-speaking participants, making Grenoble the barycenter of eco-design and eco-innovation in our sector;

→ to prepare for our 2026-2030 programs, we also spent twelve months playing a full role in the cycle of the Convention des entreprises pour le climat (corporate climate convention), the aim of which is to organize awareness-raising and transformation programs for economic decision-makers.

We will be continuing to explore relations between our subsidiary and society: Nanoelec has organized the second edition of the microelectronics poster competition<sup>2</sup> and promoted the creation of the "Women in tech in Isère" collective. •

IN 2024 & 2025, NANOELEC SUPPORTED THE CREATION

OF THE "WOMEN IN TECH IN ISÈRE" COLLECTIVE

© CEA

SANDRINE MAUBERT,

DEPUTY DIRECTOR

OF NANOELEC

© P. Jayet/CEA

## Giving meaning to our sector

by Sandrine Maubert

Pilot projects for eco-innovation are now under way in all the Nanoelec programs, notably lifecycle analysis and processes. The issues of systems and infrastructure frugality are also addressed and we are gradually taking on board the development of the digital models needed to design circuits, in order to integrate social and environmental responsibility parameters into the traditional figures of merit used in design in the electronics field<sup>3</sup>.

By supporting the CEA teams participating in the EECONE (European ECOsystem for green Electronics) project, Nanoelec is looking at a new subject of interest concerning the fate of components once they have been used.

•••

**3.** The most common figure of merit takes account of computing power vs. energy consumption, surface area vs. the cost of the component (PPAC).

Finally, even if Europe acquires high-performance technical platforms, we will also need competent and motivated human resources to run our plants. At Nanoelec, we are therefore committed to training and awareness-raising in order to motivate the students, but also to get them thinking, because they will be the future guarantors of our sovereignty, competitiveness, economic performance and respect for the planet's limits. •

“

***Mobilizing

future talents

for sovereignty

and sustainable

electronics.***

IN 2024, NANOELEC INITIATED THE VERY FIRST SYMPOSIUM FOR SUSTAINABLE ELECTRONICS AND DIGITAL, WITH PUI GRENOBLE-ALPES, LABEX MICROELECTRONIQUE GRENOBLE-ALPES, PEPR ELECTRONIQUE, IN COLLABORATION WITH MINALOGIC AND IN PARTNERSHIP WITH TECH&FEST FESTIVAL.

© P. Jayet/CEA

# EVENTS & CONFERENCES

## January 2024

### January 9

#### DIGITAL PASSPORT FOR PRODUCTS

Nanoelec/Human Capital Training Engineering program conducted an interactive masterclass on the emergence of the EU Digital Passport for products.

### January 18

#### SOI 3D PHYSICAL DEMONSTRATOR

Webinar live from CEA-Leti Cleanrooms, on a 3D physical demonstrator to allow experts to easily explain the sequence of steps in the manufacturing of a transistor in a cleanroom.

### January 19

#### WOMEN IN TECHNO- LOGICAL RESEARCH

Exhibition "Portraits of Women in Technological Research" at Grenoble Tourist Center.

### January 22

#### AMBASSADORS WITH FAME UGA

Training for professionals to go in schools and colleges to present their jobs.

## February 2024

### February 1

#### INDUSTRY ATTRACTIVENESS AT TECH&FEST

45 graphic design students from the Brassart school to design a poster on the theme: "Microelectronics for a Better World" with Aniah, Schneider Electric, Teledyne E2V and Ebra/Le Dauphiné libéré.

### February 6

#### INTERACTIVE SCREENS

Workshop for experts and students in electronics and management to consider the rebound effect in interactive screens.

## March 2024

### March 5

**ELECTRONIC

BUSINESS

AMBASSADORS**

IRT Nanoelec, the Agence Grenoble Alpes, and the Association Grenoble Alpes organized a networking event, and meetings with ambassadors of the region and the electronics sector.

### March 6

**FRUGALITY OF IOT**

Webinar: an evaluation methodology for the frugality of connected devices such as IoT, using the specific case study of a sensor designed to control water consumption in domestic environments.

### March 8

**INTERNATIONAL

WOMEN'S RIGHTS**

Round-table: feminization of the workforce in the electronics sector, with STMicroelectronics, Limatech, CEA.

### March 26

**HETEROGENEOUS 3D**

Workshop: "Heterogeneous 3D Architectures and Sensors" at DATE, The European Event for Electronic System Design & Test.

## April 2024

April 2

### WOMEN IN ENGINEERING

Nanoelec exhibition

Women in Technological

Research presented at

STMicroelectronics Crolles and

STMicroelectronics Grenoble.

© STMicroelectronics

## May 2024

May 15

### SOVEREIGNTY IN FRANCE

Nanoelec supports the 2024 Geopolitics Conference a Grenoble Ecole de Management (GEM) dedicated to the technological sovereignty of France.

May 28

### AI-EMBEDDED CMOS IMAGE SENSORS

Three-Layer Integration Breakthrough for AI-Embedded CMOS Image Sensors : three papers presented at ECTC international conference.

## June 2024

June 17

### EXHIBITION AT TELEDYNE

Employee day dedicated to para-sports at Teledyne E2V included the exhibition "Microelectronics for a Better World," created for Tech&Fest 2024.

© Teledyne E2V

June 28

### INTERNATIONAL WOMEN IN ENGINEERING DAY

Webinar: women's networks in large companies, in collaboration with the Women Engineers.

## August 2024

August 18

### 3D PACKAGING

Achieving 3-layer stacking integration for future smart imagers, published in Chip Scale Review.

## September 2024

September 3

### ATTRACTING YOUNG PEOPLE IN SCIENCE AND MICRO-ELECTRONICS

Webinar: the opportunities for industries to take part in the Night of Orientation.

September 18

### DIGITAL WORLD AND SMES

Boot and networking event with Minalogic and Captronic at Sido/Lyon. Seminar on AI & technology research for businesses by 7 FIT institutes: Nanoelec, B Com, System X, Bioaster, IPVF, Railenium & St Exupery.

© Legrand/CEA

## October 2024

### October 3

#### CONTROL SYSTEMS OF QUANTUM COMPUTERS

Nanoelec participated in the thematic day on quantum technologies organized by Minalogic.

### October 16-17

#### CAREERS FORUM

Nanoelec supported the creation of a microelectronics Village at the Grenoble Careers Forum, organized by the local authority, with Lynred, Soitec, ST, CEA, and the Ministry of Education.

## November 2024

### November 8

#### CAREERS IN CYBERSECURITY

Serious games and frugal technology sensitisation at CSAW, the world challenge for pupils and students in cybersecurity, EU node beeing yearly organized by Grenoble INP-UGA/Esisar.

### November 12

#### SCALING OF QUBIT CONTROL AND READOUT SYSTEMS

Kickoff of the new Nanoelec/Q-Loop program to accelerate the development of fault-tolerant quantum computers, by exploring novel control-command architectures and technologies.

### November 14

#### NANOELEC GENERAL ASSEMBLY

Keynotes on AI form Christophe Cerin (Inria) and Lionel Cordesses (IRT Saint-Exupéry).

### November 22

#### GRENOBLE ORIENTATION NIGHT

A round table powered by Nanoelec, with UGA, Limatech, ST, Aniah, CEA, Grenoble INP-UGA, Siemens EDA.

## December 2024

**December 10**

### **SUSTAINABLE INNOVATION**

In the frame of the Pole Universitaire d'innovation Grenoble-Alpes, Nanoelec participated in a roundtable discussion on the expectations and initiatives for sustainable innovation in public research.

**December 12**

### **SUSTAINABLE ELECTRONICS**

#### **& DIGITAL TECHNOLOGIES**

Very first national symposium on Sustainable Electronics & Digital Technologies. With the Grenoble Alpes University Innovation Hub (PUI), the PEPR Electronics, and the Labex UGA Microelectronics.

**December 17**

### **HIGH-DENSITY**

#### **THROUGH-SILICON**

#### **VIAS (TSV)**

Webinar: three years of results on combination of Hybrid Bonding technologies and High-Density Through-Silicon Vias (TSV).

## February 2025

**Feb 5-6**

### TECH&FEST

Poster competition "A World of microelectronics" with Diseingers students of Ecole bras art, Ebra/le Dauphiné libéré and Teledyne E2V. Demonstrator Gesturama, as a gamification of Nanoelec/ Addvisia plateform.

## March 2025

**March, 12**

### WOMEN RIGHT

### INTERNATIONAL DAY

Nanoelec supported the creation of a networking collective "Women in tech in Isère".

**March 31-April2**

### DESIGN, AUTOMATION AND TEST

Nanoelec supported 2025 DATE, the European Event for Electronic System Design & Test.

**April 2025**

### EASYTECH AT A GLANCE

Nanoelec and Minalogic powered a series of webinars on Easytech projects.

## May 2025

**May, 14 & 15**

### IRRADIATION HARDNESS

Nanoelec supported the annual workshop for industry on radiation hardness testing of semiconductor devices and systems G-Radnext, at Ganil (France).

## June 2025

**June, 23**

### INWED'25

Annual international women in engineering day: Nanoelec supported a special event at CEA/Y. Spot with the networking collective "Women in tech in Isère".

## July 2025

**July 1<sup>st</sup>**

### BIODIVERSITY VS BUSINESS

As an output of the CEC cycle, Nanoelec and Decathlon Outdoor cooperated to organise a discovering walk of biodiversity in the context of the urban scientific polygon of Grenoble, with a visit of Schneider Electric Intencity sustainable building.

# Sustainable development

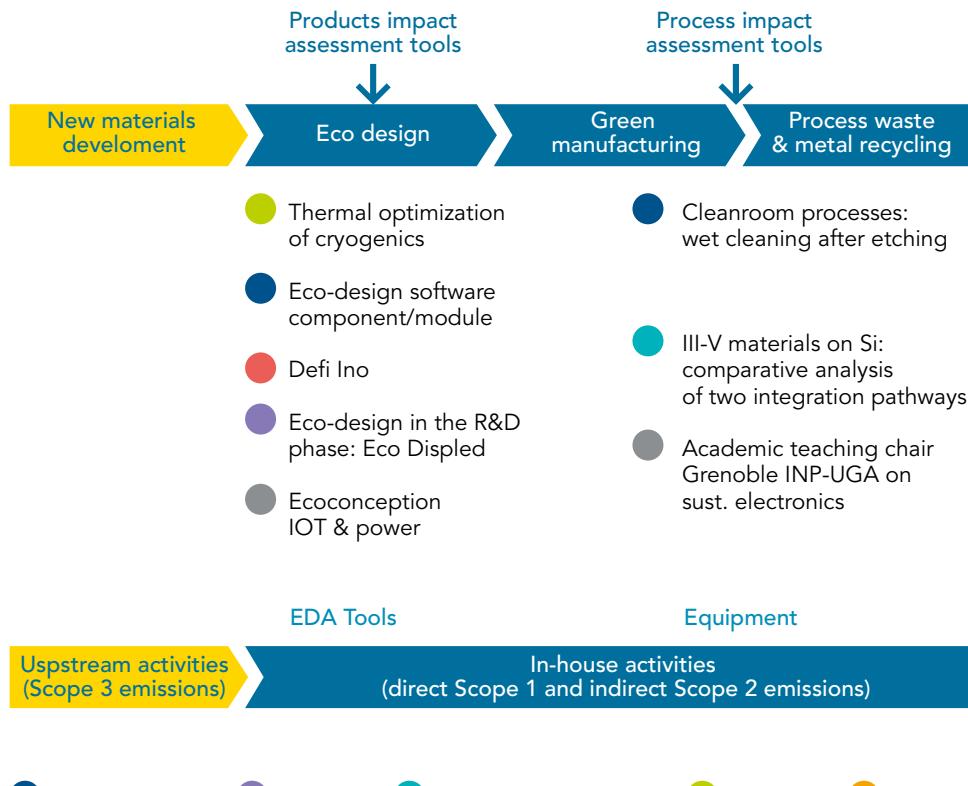

The sustainable development actions initiated and carried out by the academic and industrial players in the electronics sector as part of Nanoelec meet at least 10 of the UN's objectives. They contribute to meeting today's national and European competitiveness challenges, and to making the sector even more relevant to tomorrow's world.

Since 2024, Nanoelec's roadmaps have included addressing challenges at the crossroads of sustainable development and sovereignty. There is no doubt that these challenges will be at the heart of Nanoelec's programs in the coming years. The Institute has already initiated a large number of pilot actions, represented below.

Between 2021 and 2024, IRT Nanoelec launched three cross-cutting initiatives to inform strategy and prepare for the development of future programs for 2026-30, and several pilot operational initiatives in all of its current programs. Here is an overview of the pilot initiatives.

## SMART IMAGER

### First lifecycle analyses for the smart imager design

#### As of the design phase

With a view to designing a smart imager, the first environmental impact assessment results were obtained in 2024. By halving the number of frames to be processed in the imager, we achieve a 31% gain in the climate change criterion, 29% water savings and 49% savings in critical resources.

In 2024, the teams at Nanoelec explored the methodological possibilities for including the estimation of the environmental impacts of a 3D circuit as of the design phase.

A multi-criterion environmental model was developed using the Appa LCA software developed at CEA-List, more specifically thanks to the environmental data obtained from CEA-Leti's clean-rooms. This environmental model was configured to compare the environmental impacts of different multi-layer imager architectures.

## DISPLED

### Smart Pixel

#### Water consumption by Chemical Mechanical Polishing

A Life Cycle Assessment of the Smart Pixel flow under development as part of the Nanoelec/ Displed program was presented at Display Week 2023<sup>1</sup>. Since there are no component scale databases for microelectronics, or the literature is outdated and does not reflect current trends, this life cycle assessment (LCA) will provide new and previously unseen results. Data were included in the very first demonstration of a calculation tool dedicated to optimizing the key parameters of the environmental footprint of the associated process flow.

The 2024 teams involved in the Displed program focused on a study of water consumption by Chemical Mechanical Polishing (CMP) in hybrid bonding. The consumption of softened water in gas abatement of PECVD in the complete process flow drives the "water use" impact category.

## PULSE

### Towards a frugal blockchain

#### Building an alternative to energy-intensive proof of work (PoW)

Consensus protocols and peer-provided proofs are used to establish trust in blockchain systems. Verifiable proofs that guarantee an elapsed time based on security components have emerged as an alternative to the energy-intensive Proof of Work (PoW). *"In pursuit of developing a lightweight blockchain suitable for embedded systems, we studied the feasibility of constructing a proof mechanism attesting an elapsed time for use in a consensus protocol that is suitable for embedded systems, with low-power and that provides a security level at least equivalent to PoW,"* explains Quentin Jayet (CEA-Leti) at the IEEE International Conference on Blockchain<sup>2</sup>. The platform comprises System on Modules that feature an ARM Cortex-A7 processor with a Trusted Execution Environment (TEE) and a Trusted Platform Module (TPM).

1. Holo, Antonin, Dubarry, C., Lopes, J.-C., Dupont, M., Chabaud, S., & Templier, F. (May 12-17, 2023). MicroLED Display Life Cycle Assessment. Display Week, San Jose, USA. <https://www.displayweek.org/2023/Program/Symposium>

2. Jayet, Q., Hennebert, C., Kieffer, Y., & Beroule, V. (2024). Embedded Elapsed Time Techniques in Trusted Execution Environment for Lightweight Blockchain. 2024 IEEE International Conference on Blockchain (Blockchain), 81-88. <https://doi.org/10.1109/Blockchain62396.2024.00020>

## PULSE

### Life cycle assessment of a building

Digital solutions for sobriety

Located on the Scientific Peninsula in Grenoble, Schneider Electric's IntenCity building<sup>3</sup> offers an ideal case study for assessing the pertinence of digital solutions from the viewpoint of the carbon and more generally the environmental footprint. IntenCity incorporates Schneider Electric digital solutions to optimize both occupant comfort and energy efficiency.

The teams from CEA, the UGA, STMicroelectronics and Schneider Electric collaborated in producing the first life cycle assessment (LCA) of a building zone: calculation of the carbon footprint (for the construction and use of the building), and dynamic thermal simulation (for operation).

More specifically, the study consisted in characterizing the influence of the digital systems on the building's carbon footprint, notably in the utilization phase. While digital equipment represents more than 40% of the footprint for the building construction phase, the Building Management System (BMS) only represents 5% of this annual consumption.

Reducing the greenhouse gas emissions from the production part is a key issue in the overall decarbonization of the BMS. It will thus be crucial in the rest of the program to study the optimization of the number of equipment items necessary for an efficient BMS, while reducing the impact of the production phase of this equipment.

3. A 26,000 m<sup>2</sup> office building in Grenoble, France, equipped with 990MWh photovoltaic capacity, 100kW battery storage capacity (Net-Zero in operations & 41kWh per m<sup>2</sup>/yr)

SymposiumBlockchain62396.2024.00020

## EASYTECH

### Responsible Technology Dissemination

#### To commit companies

In 2024, the first flash diagnostics were implemented in some Easytech projects to help companies and their projects move towards an eco-design approach. With the Defi-Ino process, we are looking to develop an environmental diagnostic offering for SMEs, mid-caps and start-ups wishing to work with us. Our priority is to help companies cope with the environmental issues of public innovation policies and to provide them with competitive advantages. The proposed diagnostic is quick and inexpensive. It does not replace an actual environmental assessment, nor a life cycle assessment (LCA). It aims to be a simple evaluation, which could encourage companies to commit to a more detailed study and change their environmental responsibility culture.

## TECHNOLOGY

### Eco-innovation for technological development

#### Technology assessment

An article in the Sustainability review published by a team from CEA and Grenoble INP-UGA collaborating within the Easytech initiative of the Nanoelec/technology dissemination program, examines the essential aspects of eco-design to be assessed in the initial phases of innovation and explores the involvement of decision-makers and entrepreneurs in the sustainability assessment process<sup>4</sup>.

## Q-LOOP

### Performance and energy efficiency

#### Quantum Energy Footprint

Quantum technologies have the potential to shape safer and faster ways to extract, exchange, and process information. However, the question of their energy footprint has been a blind spot in current deployment strategies. By associating researchers who contribute to the Quantum Energy Initiative with its Q-Loop program, Nanoelec will integrate energy footprint evaluation into the design of its hardware and software demonstrators for a quantum computer. "The path towards sustainable and energy-efficient quantum technologies requires in-depth fundamental and applied research on all energetic aspects of these technologies, but with luck this could eventually bring out an energetic quantum advantage," stated Robert Whitney, CNRS Researcher (*Laboratoire de physique et modélisation des milieux condensés (UGA-CNRS Grenoble)* associated to Nanoelec/Q-Loop and cofounder of the Quantum Energy Initiative). The Quantum Energy Initiative (QEI) community gathers experts from various origins, from fundamental quantum physics to technology, from hardware to software, from research to industry, caring for the physical resource cost of emerging quantum technologies and willing to address the question in a scientific way. This requires to build new methodologies, language, and roadmaps.

4. Peigné, S., Ben Rejeb, H., Monnier, E., & Zwolinski, P. (2024). Navigating the Eco-Design Paradox : Criteria and Methods for Sustainable Eco-Innovation Assessment in Early Development Stages. *Sustainability*, 16(5), Article 5. <https://doi.org/10.3390/su16052071>

5. PRX Quantum 3, 020101 – Published 1 June, 2022, DOI: <https://doi.org/10.1103/PRXQuantum.3.020101>

As far as qubit work at cryogenic temperatures is concerned, the question of the energy footprint of a quantum computer is included in current deployment strategies for quantum HPC. On this photo taken at CEA-Irig, a cryostat cools the electronic devices to temperatures close to absolute zero, just a few miliKelvins. At these cryogenic temperatures, cold considerably reduces the thermal agitation within the materials making up the circuits being studied (for example, an electronic component, or a quantum qubit). This is a necessary pre-condition for preserving the quantum properties of these devices.

© A.Havret / CEA

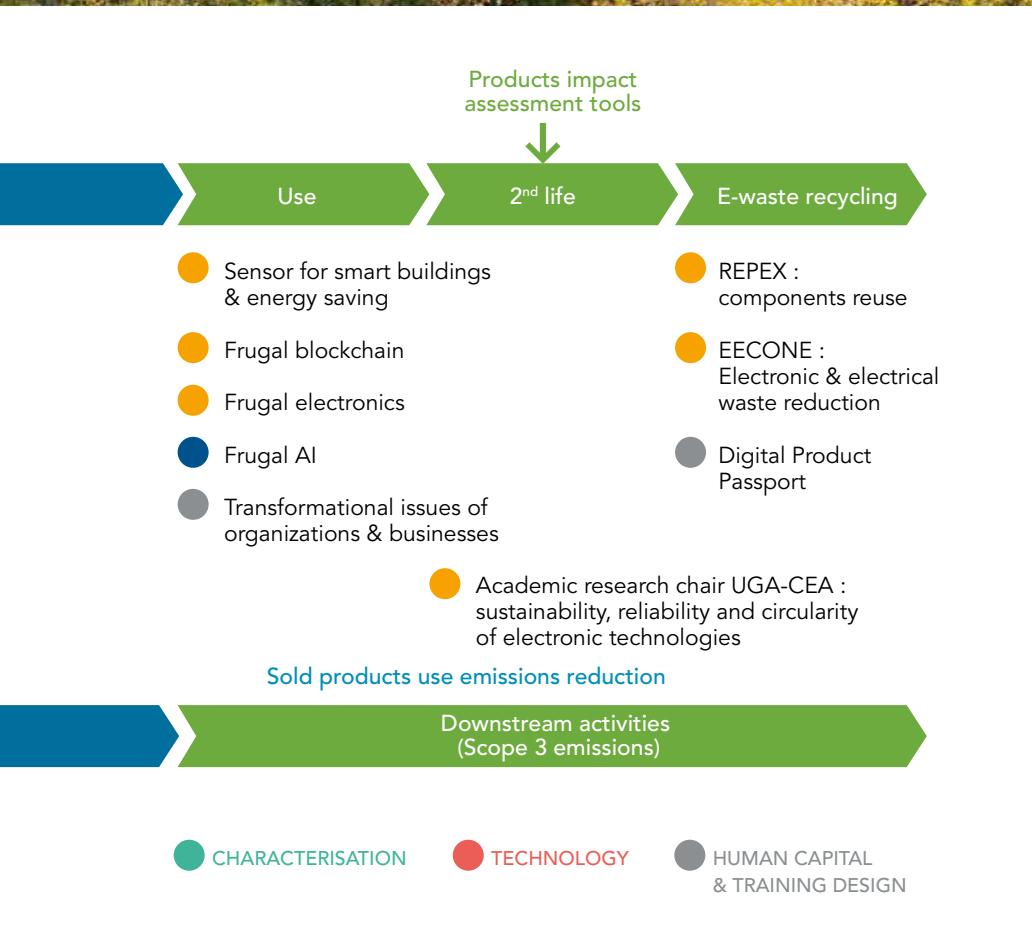

# CROSS-CUTTING INITIATIVES FOR SUSTAINABLE ELECTRONICS

## Symposium for sustainable electronics and digital systems

To support its strategic and programming thinking in favor of developing sustainable electronics – with the help of three other actors in its ecosystem (the PUI Grenoble Alpes, PEPR Electronique and Labex UGA Microélectronique) – Nanoelec took charge of organizing the very first national symposium on sustainable electronics and digital systems. Researchers from all fields were invited to propose scientific contributions promoting their most recent advances regarding tools, methodology and demonstrators on this topic. The symposium was held in Grenoble on December 12, 2024: 42 spoken presentations & posters were given, and more than 200 professionals attended. The experience will be repeated by the end of 2025.

AT THE VERY FIRST SYMPOSIUM

FOR SUSTAINABLE ELECTRONICS

AND DIGITAL SYSTEMS

© P.Jayet/CEA, 2024

## 360° vision

**At the end of 2024, Nanoelec asked CEA's Bibliography and Marketing Studies Department to produce a study of the state of the art with a view to creating an overview of sustainable electronics**, focused on the priorities established for Nanoelec's 2025-2030 vision. The aim is to highlight concepts and areas of research in order to evaluate subjects requiring development and greater maturity through collaborative research (academic, industrial) in priority fields: equipment/processes, design and tools, architecture (eco-design), management/optimization of the impact of data (storage and traffic), in addition to what each actor has already done at its own initiative.

## Convention des entreprises pour le climat

(corporate climate convention)

**From April 2024 to February 2025, two members of Nanoelec's management followed the complete cycle of the Convention des entreprises pour le climat** (corporate climate convention), involving six two-day seminars distributed over the period. This included 45 companies and organizations with a wide variety of profiles, working together in a spirit of openness and breaking down the barriers between professional sectors, with exchanges of good practices and inspiring ideas, and working as an ecosystem. Training of this type makes it possible to take on board the main arguments underlying the need to take a fresh look at development models in the light of sustainable development, climate change, the planet's limits and the necessary social foundation; to link these highly macroscopic considerations to the contingencies specific to our sector; and to prepare proposals for a long-term road-map incorporating sovereignty and sustainable development.

# PARITY AND ATTRACTIVENESS OF THE MICROELECTRONICS INDUSTRY

**For several years now, March 8 and June 23 have been dates on which Nanoelec focuses on the subject of parity and the role of women in our sector.**

The first date corresponds to International Women's Rights Day and the second to International Women in Engineering Day. Nanoelec also actively participates in initiatives relating to the attractiveness of the microelectronics industry, its professions and those of technology as a whole.

To mark International Women in Engineering Day on June 23, 2024, Grenoble Ecole de Management (GEM) produced the "She impacts" podcasts with Siemens EDA, as part of the Nanoelec/Chif program. A webinar style round-table was also organized on this occasion by Nanoelec, with the Association of Women Engineers, concerning diversity networks in the large companies, broadcasted live on June 28, 2024, with testimonials from CEA, Siemens EDA and HP.

ACTIVE PARTICIPATION BY NANOELEC IN COORDINATING ACTORS IN THE MICROELECTRONICS SECTOR, AT THE CAREERS FORUM IN GRENOBLE ALPES-MÉTROPOLE, OCTOBER 2024

© Laval/CEA

PRESENTATION OF "WOMEN IN TECHNOLOGY R&D" PORTRAITS AT THE GRENOBLE TOURIST OFFICE, ON 5 MARCH 2025, IN COLLABORATION WITH THE AGENCE GRENOBLE-ALPES, RESPONSIBLE FOR THE PROMOTION AND ATTRACTIVENESS OF THE REGION.

© P. Jayet/CEA

THE NANOEC WOMEN IN TECHNOLOGICAL RESEARCH EXHIBITION WAS PRESENTED AT STMICROELECTRONICS CROLLES AND STMICROELECTRONICS GRENOBLE, ON APRIL 2024

© CEA

## Feminization of the workforce

On the occasion of International Women's Right Day, Nanoelec hosted a round-table discussion on the feminization of the workforce in the electronics sector. The debate was moderated by Sandrine Maubert, Deputy Director of IRT Nanoelec, with the participation of: Frédérique Le Grévès, President of the Strategic Committee for the

Electronics Sector and President of STMicroelectronics France – Europe (via video conference), Hélène Wehbe-Alause, Research Director at STMicroelectronics Crolles, Florence Robin, Founder and President of Limatech, Anne Roule, Director of the Technology Platform Department at CEA-Leti.

© CEA/Legrand

# POSTERS TO PROMOTE THE SECTOR

On the occasion of the very first Tech& Fest festival, in February 2024, 45 graphic arts students from the Brassart school took up the challenge from the microelectronics actors in the Alpine region, coordinated by Nanoelec: this was to design a poster on the subject "Microelectronics for living in a better world".

The operation was repeated in 2025: the students from the Brassart school worked on the subject after meeting experts from the various companies in the Nanoelec consortium. Responding to our "commission" as true professionals, the students' proposals reflect society's perception of the microelectronics sector. The best creations selected by a jury of Grenoble-based personalities

from the fields of culture, science and industry will be included in a widely distributed catalogue and exhibition throughout the year, helping to raise the profile of our sector across the region. This collaboration with the *Dauphiné libéré* newspaper and the Brassart school enables us to reach out to society, beyond the boundaries of our ecosystem.

THE EXPERT PANEL

SELECTED SEVEN

POSTERS AMONG

THE CREATIONS

FROM THE BRASSART

STUDENTS.

# Heterogeneous integration

Displed, Smart Imager and Photonic Sensors are all based on the same multi-layer principle, initiated by the 3D integration program during the first ten years of IRT Nanoelec.

Nanoelec is positioned as a French center of excellence in the field of heterogeneous integration, with the capacity to address a variety of application markets, including embedded computing, high-performance computing, imaging, displays, and telecommunications. Heterogeneous integration is a technological solution that paves the way for embedding more AI power in components, with the ultimate goal of enabling learning at the level of the embedded system itself, locally. This will make it possible to offer differentiated solutions. As a result, the amount of data exchanged is reduced, thereby reducing the environmental impact.

Heterogeneous integration is a strong trend in the sector, which will require significant ambitious developments and will meet the expectations of manufacturers and market needs while addressing the challenges of sovereignty in the industry by ensuring that key components and system building blocks are controlled in France and Europe. •

# From imaging to visioning

Providing relevant and real-time environment analysis by vision.

© Pixabay

ERIC OLLIER, DIRECTOR OF THE NANOELEC/SMART IMAGERS PROGRAM

© P. Jayet/CEA

**W**ithin the Nanoelec/Smart Imager program, our aim is to develop the technologies needed for the next generation of imagers, which will enable the transition from capturing images to exploiting the information they contain. This exploitation will be performed by the sensor itself, so that it can perceive a scene, understand the relevant situation and intervene on it.

This is a truly disruptive paradigm shift, with the focus shifting to computing and memory challenges, in addition to image generation. The concept includes the implementation of artificial intelligence within the image sensor itself.

In 2024, work continued on developing the key technological building blocks: hybrid bonding, HD-TSV, heterogeneous integration and specific technologies for infrared applications. The development of a "dual damascene" structure is ongoing to improve

the hybrid bonding connection. This reduces the number of interfaces between the various levels and thus the total resistance of the interconnections in the 3D stack. Numerous technological improvements have been made to the HD-TSV and have boosted their maturity, while continuing with the scaling roadmap.

Activity to develop heterogeneous integration technologies based on D2W approach grew this year, with the design of a new set of complex masks which will enable interconnection pitch reduction along with the development of different integration architectures. Finally, in-depth study of the use of 3D technologies for IR imager applications led to start developments based on D2W technologies in order to allow access to advanced 300mm CMOS technologies.

New integrated circuit design methodologies are being implemented to meet the two-fold challenge of introducing AI computing functions as close as possible to the sensors. The two design •••

platforms created in 2023 evolved in 2024 with the addition of new CAD design tools, thus completing the design stream for smart imagers.

Our 3D multi-layer integration technology is progressing in terms of maturity and electrical performance: significant technological improvements have been made, integration efficiency has been improved, and more and more wafers are being completed, with improved morphological and electrical characteristics. With regard to electrical performance, the resistance values of the three-layer stack have been reduced and the electrical isolation at HD-TSV level has been significantly improved. Thanks to joint work by CEA and STMicroelectronics, the process design kit (PDK) including the HD-TSV contributions is more-

over, place and route process has also been optimized to enable precise 3D design in order to meet performance requirements.

Finally, based on all these developments, 2 functional 3-layer smart imager demonstrators were studied under the program: one called J3DAI is virtual, and the other called EB3D/Tanzanite is slated to reach silicon demonstration level in the coming years. The first one intended for visible applications is based on an STMicroelectronics pixel with an AI accelerator from CEA, while the second one intended for event-based applications is based on a pixel designed by Prophesee. An innovative AI part (GNN) was developed by CEA and Prophesee, with the whole scheduled for manufacture in the STMicroelectronics and CEA cleanrooms. •

## SMART IMAGER PROGRAM AT A GLANCE

### → Vision

The transition from imagers to vision sensors is generating new market opportunities

### → Ambition

To provide key HW and SW building blocks, to validate them through demonstrations ranging from test vehicles and proofs of concept to the prototyping of a smart, multi-layer imager

### → Mission

Stacking/3D technologies, embedded AI and data management, new architectures

### → Partners

CEA, Lynred, Prophesee, Siemens EDA, STMicroelectronics, Grenoble INP-UGA

3D CHIP

MOUNTING

AT CEA-LETI

© Havret/CEA, 2024

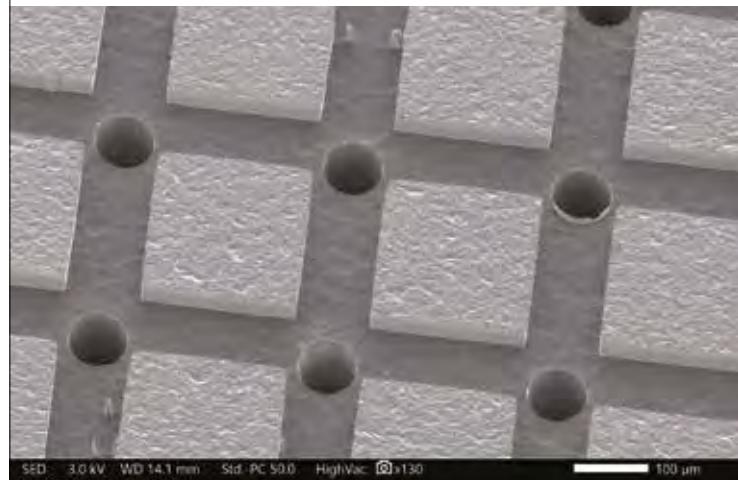

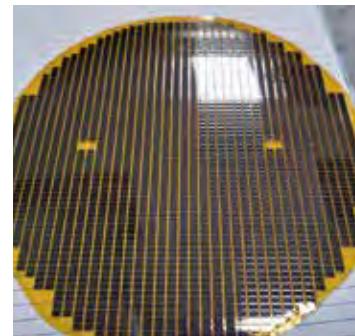

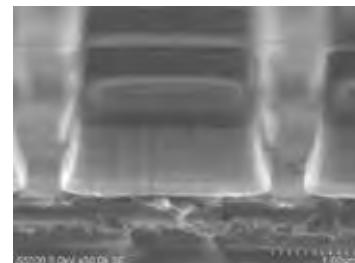

## Connecting layers by sharpening through silicon via HD-TSV are now available for multi-layer 3D integration

The demonstration of wafer level 3-layer integration including Face-To-Back (F2B) configuration received an award at the major ECTC 2024 conference. It combines two fine pitch Cu-Cu hybrid bondings with high-density connections up to an operational 3-layer test vehicle.

**“**

**For several years now, a CEA-Leti team has focused on the key enabling technology of TSV for the 3-Layer CMOS image sensors under development at Nanoelec...**

3D stacks offer multiple advantages for advanced components such as smart imagers and their assembly in a wafer-to-wafer (W2W) approach opens up access to very fine pitch interconnections. While hybrid bonding is commonly used to connect the layers, high-density (HD) TSV are mandatory for the signals to be transmitted through them.

For several years now, a CEA-Leti team has focused on the key enabling technology of TSV for the 3-Layer CMOS image sensors under development at Nanoelec, and every year it publishes several papers to report on its progress at the international ECTC conference.

At IRT Nanoelec, CEA and ST-Microelectronics demonstrated the feasibility of 3-layer stacking in 2023. This major result of the Smart Imager program was presented in the form of three publications at the major ECTC 2024 conference. One of them received a "best paper award" from the professionals.

*"After having successfully demonstrated a 2-layer face-to-back (F2B) test vehicle (TV), we reached the next level of integration by achieving a 3-layer TV with fine-pitch Cu-Cu hybrid bonding (HB) technology and high-density (HD) Through Silicon Via (TSV);*

*After demonstrating 3-layer TV functionality, the next step will be to implement this 3D technology in a functional advanced CMOS image sensor (CIS) in the next few years," says Stephan Nicolas, as a first author of the paper receiving the award.*

*"The 3-layer demonstrator is one of Nanoelec's major technological achievements," underlines Alexis Farcy, R&D Process Development Engineer - 3D Integration at STMicroelectronics. "The three-layer structure will enable the image sensor to be equipped with an artificial intelligence function, which necessarily requires a lot of computing power and memory. Hybrid bonding has already been well developed as part of Nanoelec's programs since 2012. It is now industrial. And from there, the new building blocks of the Smart Imager begin. For us, these morphological and electrical results validate these building blocks, which are really the key elements that will now enable us to move on to the physical relationship of a much more ambitious functional demonstrator."*

FIB-SEM 3D CROSS-SECTION OF THE 3-LAYER TEST VEHICLE - PITCH IS 6  $\mu$ m FOR THE BONDING PADS - HD TSV DIMENSIONS ARE 1x10  $\mu$ m.

© CEA

## In-sensor computing for event-based imaging

On the occasion of the Nanoelec 2024 General Meeting, Pascal Vivet, CEA-Leti, reviewed the development of event-based imagers equipped with artificial intelligence.

SCHEMATIC OF A 3-LAYER SMART IMAGE SENSOR, WITH EMBEDDED AI

© P. Jayet/CEA

### Why develop event-based sensors?

**P.V.** Event-based imagers allow very high-rate acquisition of images, in that only the pixels which record a variation contribute to the data stream. The target applications are augmented reality, typically tracking of the hand, the eyes, gestures, presence tracking or detection.

Sensors incorporating AI functions are already available on the market, but our 3-layer concept offers greater performance and a wider range of applications. We start from an event-based 2-layer imaging architecture available at Prophesee. We propose adding a third electronic layer which will be strongly coupled to the imager. This third layer supports AI functionalities and this is called in-sensor computing.

### What are the development constraints for such a very small sensor?

**P.V.** In Nanoelec/Smart Imager program, we are developing both the hardware part and the AI software highly optimized to reduce energy consumption and computing times. It will be possible to make extremely small objects capable of monitoring our environments at very low cost and running on batteries. Our sensor will measure barely more than one cubic millimeter, and will thus easily be installed in the limited space available inside a smartphone. Its electrical consumption is very low and its processing latency, that is acquisition and processing with embedded AI, will be about one millisecond. This project is the result of active collaboration, in which Prophesee provides the core of the 2-layer imager, CEA proposes and implements the specific AI accelerator in the third layer, Siemens EDA supplies the design tools (behavioral synthesis, DFT, sign-off), and STMicroelectronics participates in logical and physical implementation of the final circuit. The manufacturing of the demonstrator will use both STMicroelectronics and CEA-Leti clean-rooms

### How to embed AI directly in the image sensor?

**P.V.** In an event-based imager, the principle is to generate a pixel event when there is a change in contrast. In this case, standard AI solutions are not easily applicable. The traditional Convolutional

Neural Networks (CNN) used in AI mean that the image and the pixels must be integrated in time, which loses information on the precision of the events. SNN (Spiking Neural Network) type networks, based on spikes, even though closer to the nature of the pixel events, are not suitable as a type of coding. A network structure based on GNN (Graph Neural Network) was proposed to encode the sparsity of pixel events, while retaining an efficient computing method. The HUGNet processing architecture, based on GNN, was proposed, as it can be used to process different types of AI algorithms (monitoring, tracking, recognition, classification, etc.), with unparalleled memory and computing performance ( $> x100$ ) by comparison with the best CNN solutions that could be imagined with an event-based sensor. The algorithm core was developed in 2024, a first high-level architecture model was developed at the end of 2024, and development of the RTL hardware building block is ongoing in 2025, with the circuit being sent for manufacturing at the end of 2025.

PASCAL VIVET, FORMER SCIENTIFIC DIRECTOR OF THE DIGITAL CIRCUITS AND ARCHITECTURES DEPARTMENT AT CEA-Leti

© Jayet/CEA, 2022

SÉBASTIEN THURIES,

DEPUTY DIRECTOR

OF NANOELEC/SMART

IMAGER PROGRAM

© Jayet/CEA, 2024

## Date Conference 2024

In April 2024, at the reference international conference in the field of circuit design, DATE<sup>1</sup>, the Nanoelec/Smart Imager program teams took part in organizing a workshop on the challenges of 3D, more particularly in the field of imagers.

Sébastien Thuries, engineer at CEA-List and Deputy Director of the Nanoelec/Smart Imager program, presented the benefits of multi-layer technology for developing an image sensor with a low energy footprint.

"We are progressing in terms of silicon production with respect to integration of a third silicon wafer, thanks to Through Silicon Vias

(TSV) at very high density (~1µm on a side)," he explains. "The circuit design methodologies are also evolving and a suite of tools (design, simulation and verification) benefited from the circuits developed in the program." Two circuits were presented, one for imaging in the visible spectrum and the other for event-based imagers: J3DAI, a multi-layer circuit with integrated AI accelerator for rapid and efficient processing of the AI algorithm, and HUGNet, also a multi-layer circuit for AI processing dedicated to the event-based imager thanks to the Graph Neural Network (GNN) and offering results several orders of magnitude better than traditional Convolutional Neural Networks (CNNs).

1. Date Conference, March 25 – 27, 2024 | Valencia, Spain

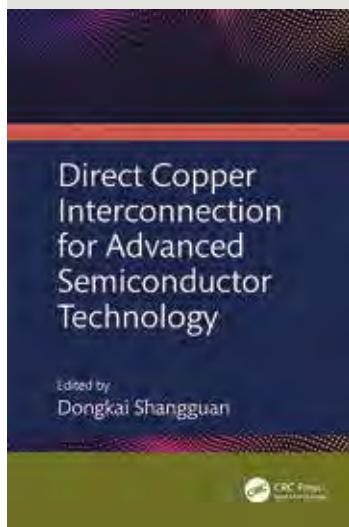

## Characterization, Modeling, and Reliability for Direct Copper Interconnection

Hybrid bonding technology.

Stéphane Moreau, a senior expert at CEA-Leti in the field of integrated circuit interconnect reliability, and Dongkai Shangguan, an IEEE Fellow & IMAPS Fellow and President of Thermal Engineering Associates, Inc. and a strategic advisor to innovative companies in the global semiconductor and electronics industry, have written a book chapter addressing the advances and challenges related to "Direct copper interconnections for advanced semiconductor technologies".

They reviewed the most significant qualification and reliability achievements for hybrid bonding-based interconnects over the last ten years by the industry and the scientific community. An overview of 3D interconnects and their evolution, failure mechanisms, and related accelerated tests and associated standards for 3D packaging technology are analyzed. A discussion follows on the qualification and reliability testing results of the hybrid bonding technology by the industry and the scientific community. This book chapter is completed by a review of numerical simulation studies covering bonding physics, electrical and thermal performance and the reliability of hybrid bonding technology.

**“**

**An overview of 3D interconnects and their evolution, failure mechanisms, and related accelerated tests and associated standards for 3D packaging technology are analyzed.**

## Copper interconnections within cryogenic systems

Assessing robustness and electrical performance of copper HD-TSV at low temperatures.

A study led by CEA-Leti scientists evaluates copper High Density-Through Silicon Vias (HD-TSVs) in cryogenic environments, which are crucial for applications like quantum computing and astrophysics. The use of HD-TSVs notably allows for increased signal density, enabling device scaling. "1,980 thermal cycles between 344 K and 77 K were conducted to assess the mechanical and electrical robustness of HD-TSVs to cryogenic conditions," explains Stéphane Moreau, as first author of the paper published in IEEE Electron Device Letters.

Additionally, one thermal cycle was carried out in a cryostat down to 2 K. In-situ and ex-situ electrical measurements show remarkable stability in the electrical resistances of the tested structures with a variation of less than  $\pm 3\%$ , even after 1,980 thermal cycles. "Our results confirm the robustness and electrical performance of copper HD-TSV at low temperatures, opening up prospects for their integration within cryogenic systems," Stéphane Moreau adds.

# Towards Display Technology Leadership in Europe

NATACHA RAPHOZ,

NANOELEC/DISPLED

PROGRAM DIRECTOR

© Havret/CEA

MicroLED technology is revolutionizing the field of displays by offering exceptional image quality and immersivity, with display sizes ranging from smartphones to large TVs.

**T**he Nanoelec/Displed program uses Smart-Pixel technology, a patented key technology which paves the way for the manufacture of displays based on new display concepts in Europe.

The goal is to produce extremely bright micro LEDs and assemble them with an underlying control circuit, broken down into very high performance pixels. We use techniques for hybrid bonding of different materials, as well as LED cutting to mount them onto the display support, with extreme precision, high density and high speed: this is the "mass transfer" challenge.

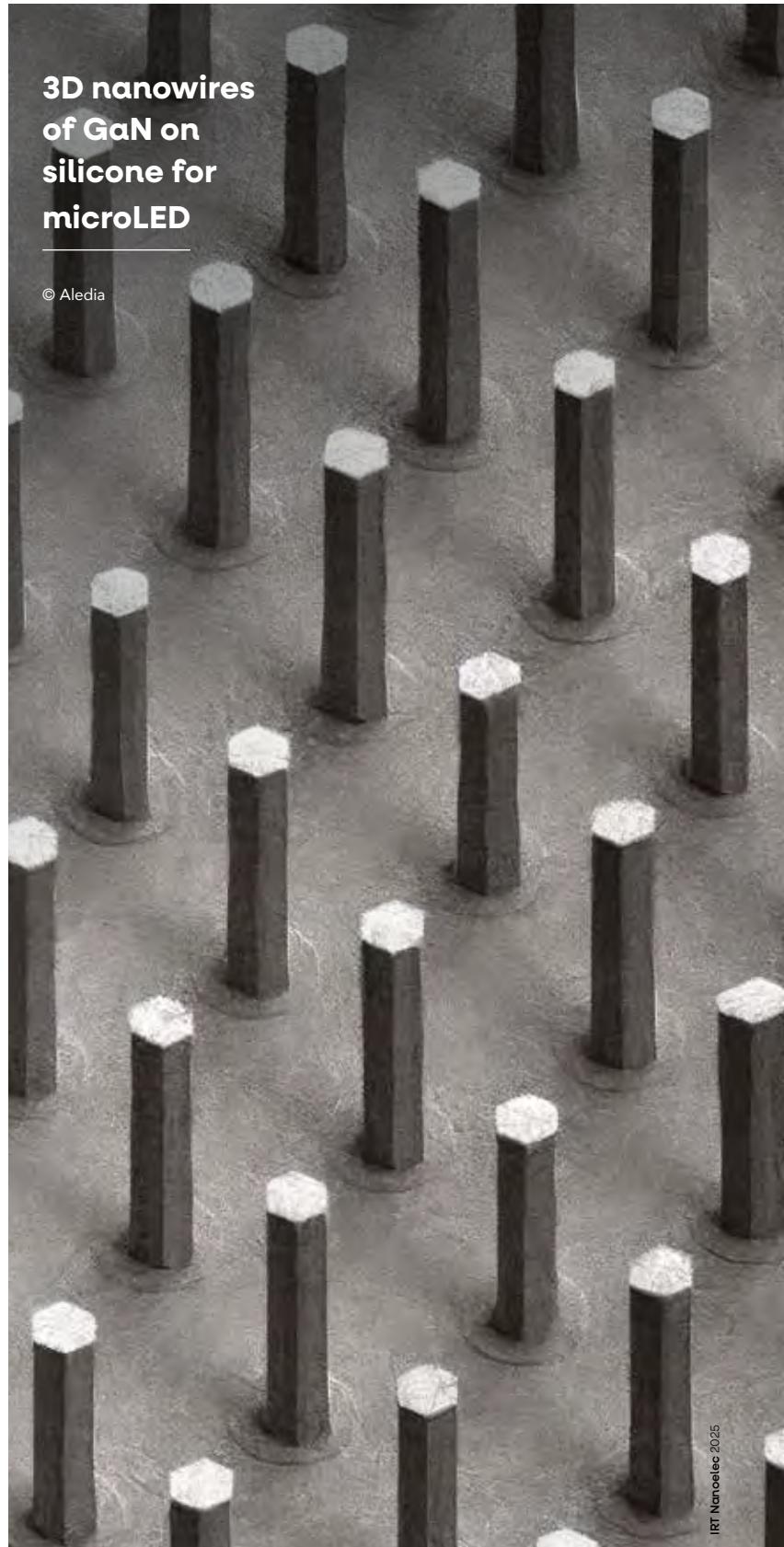

In 2024, the change in Aledia's market access strategy led to work being focused on large pitch 2D-LED technologies, while the small pixel, high-resolution 3D LEDs sector focused on blue smart-pixels.

Given the changing market demands, in 2024 the partners decided to focus their efforts on integration of the 200mm process in order to speed up its industrialization. We are thus developing a low-temperature process for hybrid bonding in order to tap new and promising markets. We are also exploring new solutions for very high-end displays, notably flexible ones. •

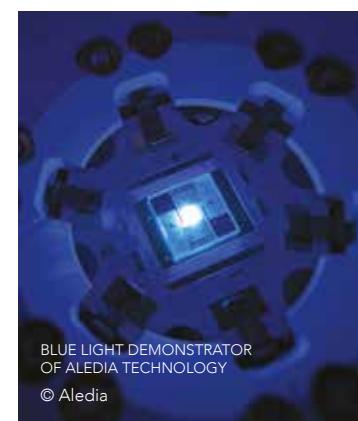

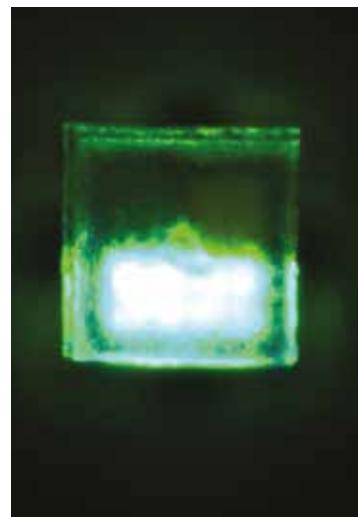

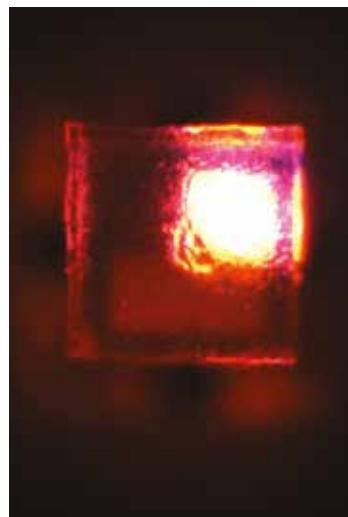

## The first LED light

In 2024, Aledia achieved its very first LED light-up with the process at Champagnier.

This first LED light-up has promising performance homogeneity and a VF (applied voltage) decrease at 3V.

Nanoelec's partners are collaborating to design and develop a high-end Virtual Reality glasses solution, using 2D smart pixel. The prototype was presented at the Eurodisplay 2024 symposium in Grenoble.

## DISPLED PROGRAM AT A GLANCE

### → Vision

A unique opportunity for a French & European ecosystem on large display technologies for immersive applications

### → Ambition

To design and demonstrate key microLED technologies for high-end, immersive displays

### → Mission

To develop process flows for microLED, Smart-Pixel fabrication and mass transfer onto the display

### → Partners

Aledia, CEA, EVGroup, SET

## Mass Transfer

The radically new techniques developed within Displed allow high-volume collective chip mounting with high-precision alignment.

At the Nanoelec general meeting in November 2024, Abdenacer Aitmani, a researcher at CEA-Leti working on the Nanoelec/Displed program, recalled the advantages of microLEDs.

"In terms of brightness, this is the highest performance technology today available. This can create displays which remain legible even when exposed to direct sunlight," he explained. If packaged in optimal conditions, microLEDs can then function for 40,000 or even 50,000 hours, which smashes all lifetime records by comparison with existing light sources!".

Abdenacer is more particularly interested in transfer to the display support, which is one of the major challenges for industrial deployment. "A large number of chips have to be transferred, rapidly," he points out. This is the technological hurdle known as mass transfer.

"Let's take the example of a display, I would say an equivalent 8K<sup>1</sup> display. Today, if we wanted to manufacture it with microLEDs, based on gallium nitride, and if we assume three chips (red, green and blue), plus the related operations, that would mean more than 100 million chips to be transferred to the display, according to Abdenacer's calculations. Even if the most sophisticated automated instruments can achieve 100,000 components per hour, that's not enough to obtain an end-product that is economically affordable for the public."

As part of the Displed program, the SET and EVG companies, along with CEA, are developing

strategies for handling brighter chips and placing them rapidly on the display support.

"These operations must be performed with no chip losses, no alignment errors and no damage to the chips being handled." The process must also enable defective chips to be replaced: "Just think, you are transferring millions of chips and five or six of them are defective, you would be unable to sell that display," adds Abdenacer.

•••

1. According to Samsung's definition, an 8K television has a display consisting of 7,680 horizontal pixels and 4,320 vertical pixels, or a total of almost 33 million pixels.

SET FC300 SIC MATERIAL

ULTRA-FLAT PLACEMENT

TOOL

© CEA

The radically new techniques developed under Displed allow high-speed, collective chip mounting with high-precision alignment. The processes developed could thus make it possible to take hundreds, thousands or even tens of thousands of chips at a time.

*"All these tasks are the preliminary steps needed to develop the industrial equipment essential to the deployment of a display production industry in France or in Europe," concludes Abdenacer.*

HANDLING MICRO-TOOL FOR MASS TRANSFER OF MICROLEDs

© CEA

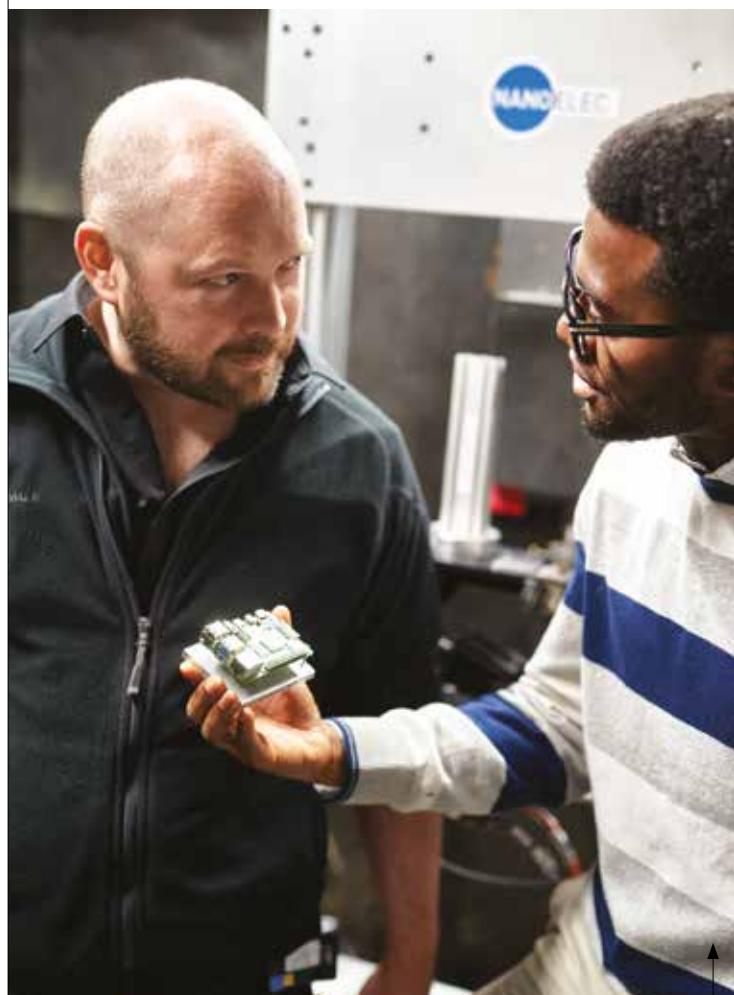

**Abdenacer Aitmani,

researcher at

CEA-Leti for the

Nanoelec/Displed

program, inspects

prototype large-scale

chip transfer tools**

© Devise/CEA

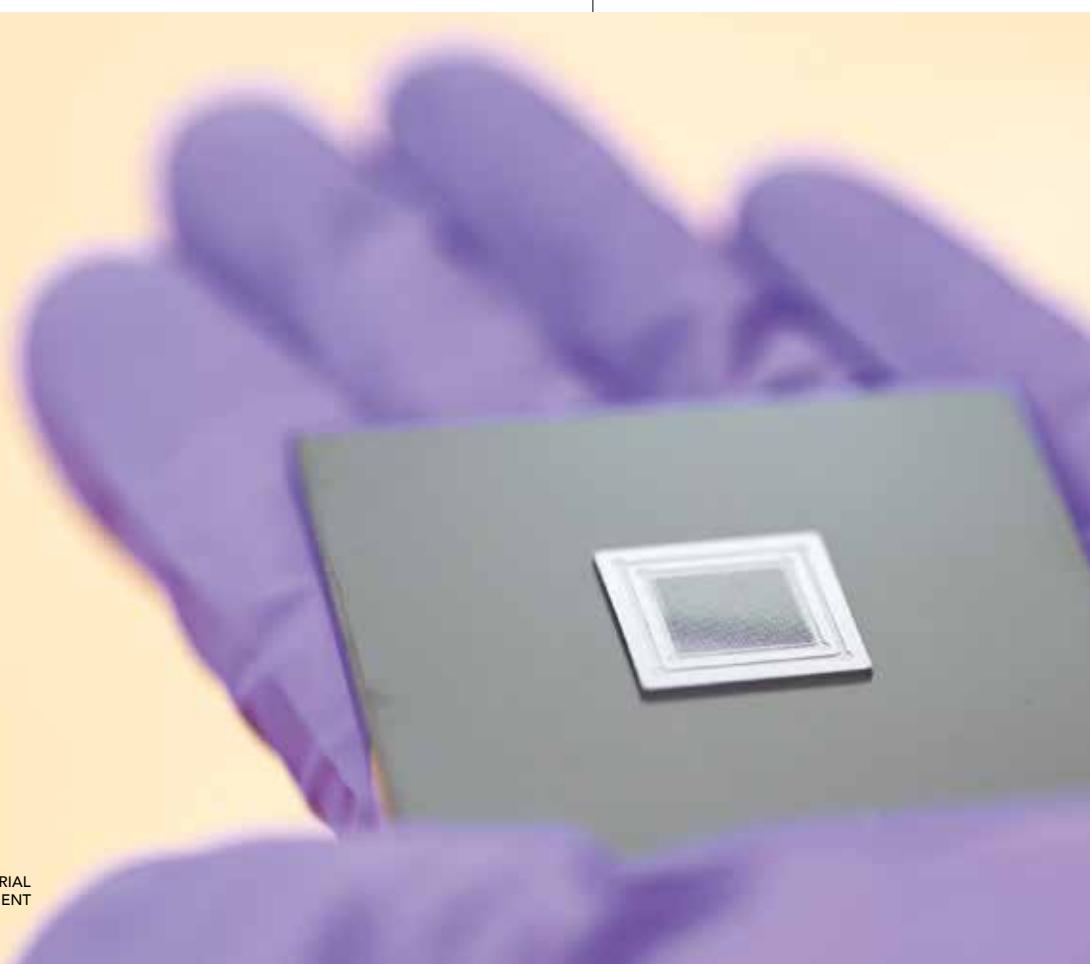

## Vacuum bonding of LED chips

Within Nanoelec, SET and CEA teams have used equipment from their portfolio to test transfer of small dies, individually and collectively.

*"We're developing a silicon micro-tool, in which holes are made, which suck in many chips at once and move them from an original wafer to a display," explains Pascal Metzger, Managing Director of SET. The first-generation vacuum-based micro-tool for mass transfer of microLEDs is undergoing testing on an upgraded version of the SET-FC300 tool. "We have already obtained some encouraging proofs of concept, handling individual tiny chips. To improve accuracy pick-up for smaller dies, we have modified the entire closed-loop system of the robot on one of our machines, adds Pascal Metzger. Our goal is to finish the R&D phase by end of 2025, and then 2 or 3 years to start prototyping and industrialization."* The redesign of the robot of the SET/ACC $\mu$ RA Plus has achieved better placement accuracy of the dies, as required by their tiny dimensions and the small pitch. The results are encouraging, either when handling one single die, or performing mass transfer. All these experiments will be continued in order to adjust the different parameters for efficient mass transfer and optimized bonding.

ACC $\mu$ RA PLUS FROM SET IS USED TO TEST THE PICK-AND-PLACE STRATEGY FOR THE MASS TRANSFER OF DIES

© SET

## The move to flexible displays

Advanced applications of the Smart-pixel microLED displays concept, such as flexible displays, or the new functionality based on the addition of sensors, are truly promising.

The Augmented Reality market is notably the most demanding in terms of performance. The teams involved in the Displed program identified the design and technical challenges for development, such as pixel-pitch reduction, high-density interconnects reliability. Specimen wafers based on a new process flow have been prepared by CEA-Leti and delivered to Aledia in 2024.

## Nanoscale layer etching

A tool capability to etch GaN-based  $\mu$ LEDs has been tested: one process was implemented, based on inputs from Lam Research.

The tool supplier Lam Research and Nanoelec collaborate on a joint development program aimed at advancing nanoscale layer etching processes for a wide range of applications from GaN microLEDs to materials used in RF devices and MEMS.

One process evaluated using Lam Research equipment is the etching of a GaN-based  $\mu$ LED stack, preventing damage to the underlying aluminum contact layer. The landing capability has been successfully demonstrated despite the minimal etch rate difference between Al and GaN.

© Lam Research

## Blue digital LED product

In 2024, Aledia built a demonstrator including a matrix of new-generation 2D-LED Smart Pixels on a fully operational PCB. Severine Cheramy, Product Line Manager at Aledia, presented results at two international conferences<sup>2</sup>.

*"Active-matrix BLU using Aledia Blue Digital LED is now demonstrated as a possible solution for Virtual Reality applications, and other high-end BLU LCDs could also benefit from it in the medium term," commented Séverine after the Touch Taiwan conference (April 2024).*

The Aledia Digital LED Manufacturing Roadmap was presented, including the present ramp-up for the production of the blue digital LED product.

**2.** LIDs (Grenoble, June 2024) and Touch Taiwan (Taipei, April 2024).

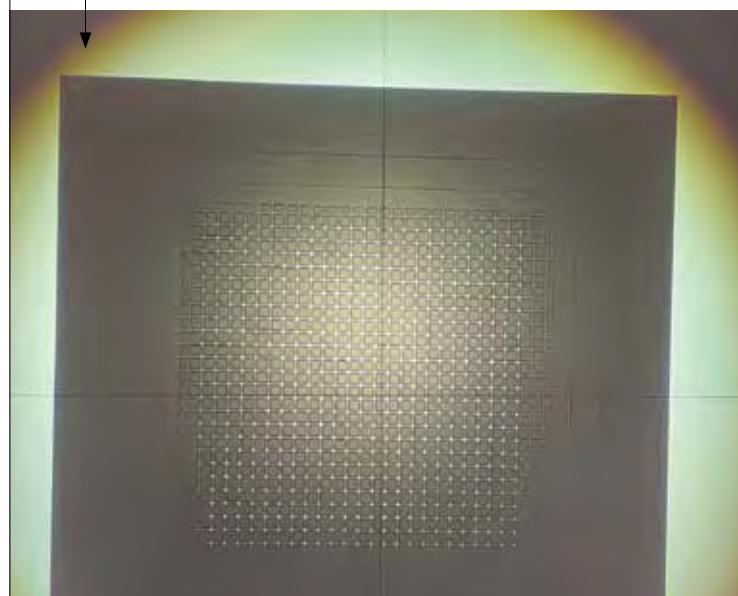

## Full-color unit demonstrator

A demonstrator including a matrix of new-generation 2D-LED Smart-Pixels on a PCB is fully operational and major improvements have been obtained on the roadmap towards 300mm microLED production.

LED growth on the 300mm MOCVD system installed at Aledia/Echirolles showed an emission wavelength centered on 446.4nm with very low standard deviation among the LEDs.

3D-LED Smart-Pixel process integration was successfully demonstrated, involving two metal levels, hybrid bonding and backside grinding. For the demonstration of full-color units, the test vehicle implemented by Aledia teams showed blue emission coming from the nanowires and green and red emission based on QD conversion.

FOR THE DEMONSTRATION OF FULL-COLOR UNITS, THE TEST VEHICLE IMPLEMENTED BY ALEDIA TEAMS SHOWED BLUE EMISSION COMING FROM THE NANOWIRES, AND GREEN AND RED EMISSION BASED ON QD CONVERSION

© Aledia

## Production building now completed at Champagnier

In 2024, Aledia completed construction and installed 25 systems in the Champagnier plant (SDM). The plant now has 34 machines installed.

© Aledia

# New opportunities based on large-scale 300 mm silicon photonic technologies

The aim of the Nanoelec/Photonic Sensors program is to produce a complete range of solutions designed to facilitate the adoption of photonics on silicon by new applications requiring complex detection functions, such as 3D detection in mobile phones, self-driving vehicles, or biochemical detection for health care purposes and environmental monitoring.

STÉPHANIE GAUGIRAN

(CEA), HEAD OF THE NEW

PHOTONIC APPLICATIONS

SECTION AT CEA-LETI

& DIRECTOR OF THE

NANOELEC/PHOTONIC

SENSORS PROGRAM

© UtopikPhoto/CEA

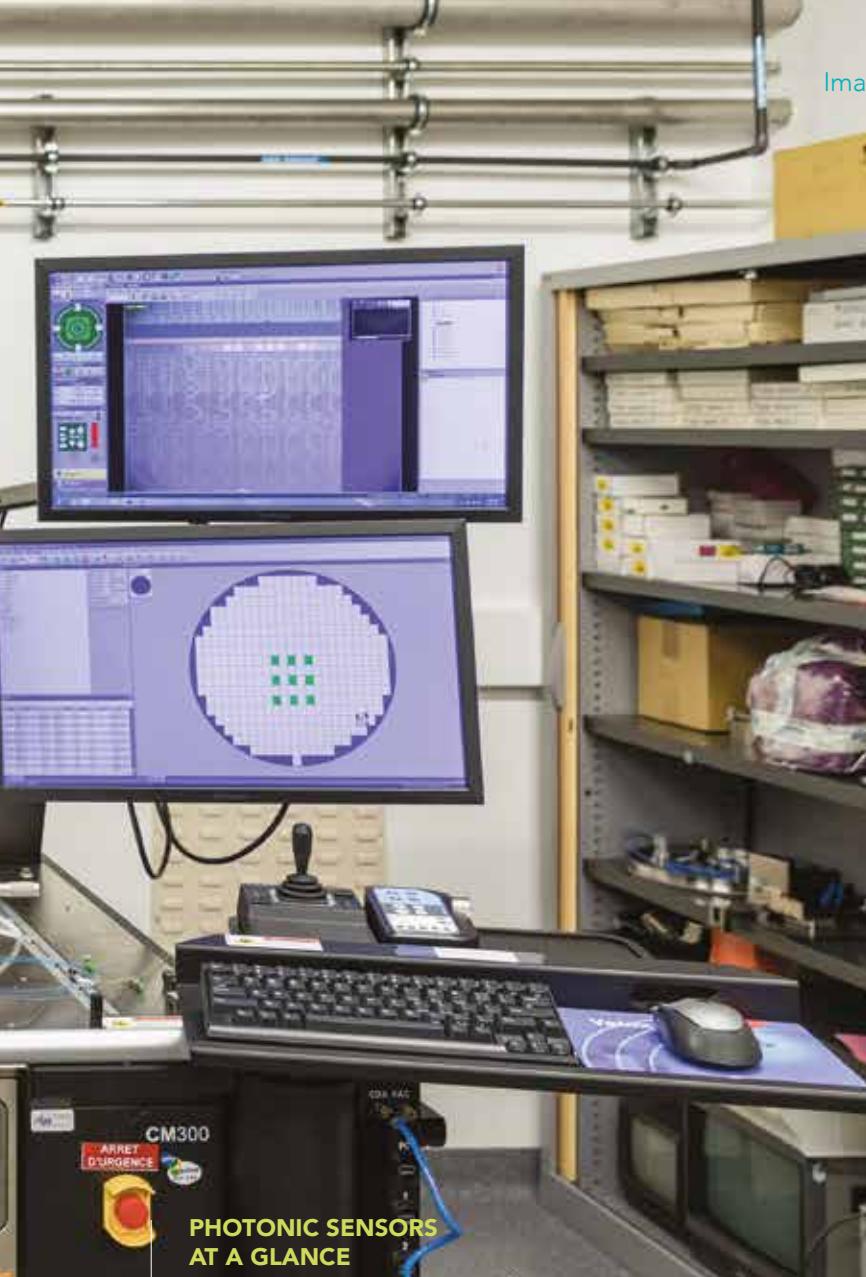

**T**he main key technological challenges for this type of sensor are measurement precision, miniaturization, data processing and transfer and compatibility with mass production. The unique properties and performance of integrated photonics are essential in meeting these challenges.

In 2024, a first demonstration of ethanol detection without substrate functionalization was performed using a two-wavelength Mach Zehnder interferometer. Initial results are highly promising.

Our teams performed a study of a physical phenomenon limiting long-range LIDAR applications, which require high power levels: the non-linear two-photon absorption (TPA) phenomenon. The process was transferred to STMicroelectronics at the end of the year.

Work on very low loss SiN guides improved the platform's results and its performance is now world-class.

Finally, the year was marked by the production of the 300mm laser batch and the first structures were successfully tested. •

### PHOTONIC SENSORS AT A GLANCE

#### → Vision

New sensor opportunities based on large-scale 300mm silicon photonic industrial technologies

#### → Ambition

Provide the Nanoelec partners with a complete chain of solutions – from EDA to mass production – designed to facilitate the adoption of photonics on silicon by new applications requiring complex detection functions such as 3D detection in mobile phones, autonomous vehicles, or biochemical detection for health care and environmental surveillance

#### → Mission

Our main technological challenges for such sensors are measurement precision, miniaturization, data processing and transfer, and also compatibility with mass production. The unique properties and performance of integrated photonics are essential in being able to meet these demands and these challenges

#### → Partners

Almae, CEA, CNRS, Siemens EDA, STMicroelectronics

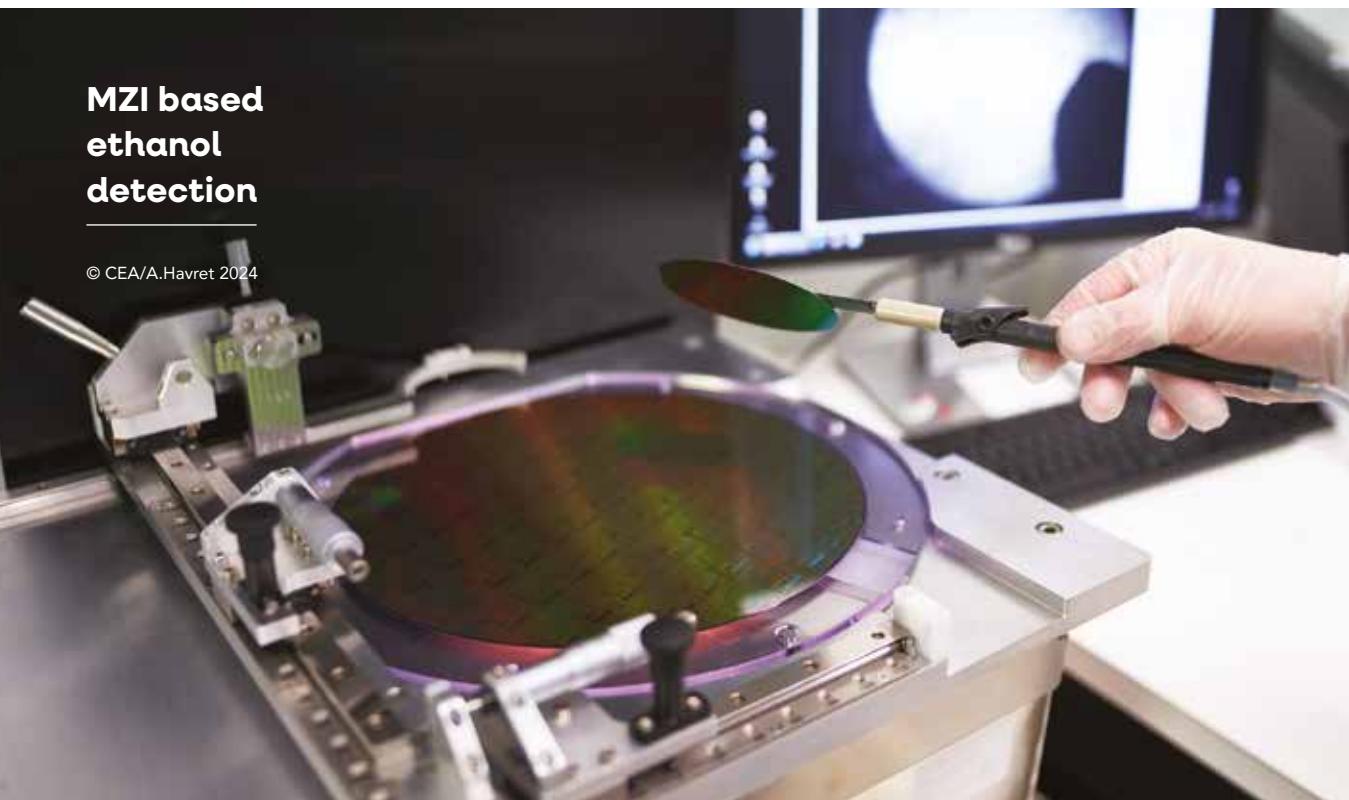

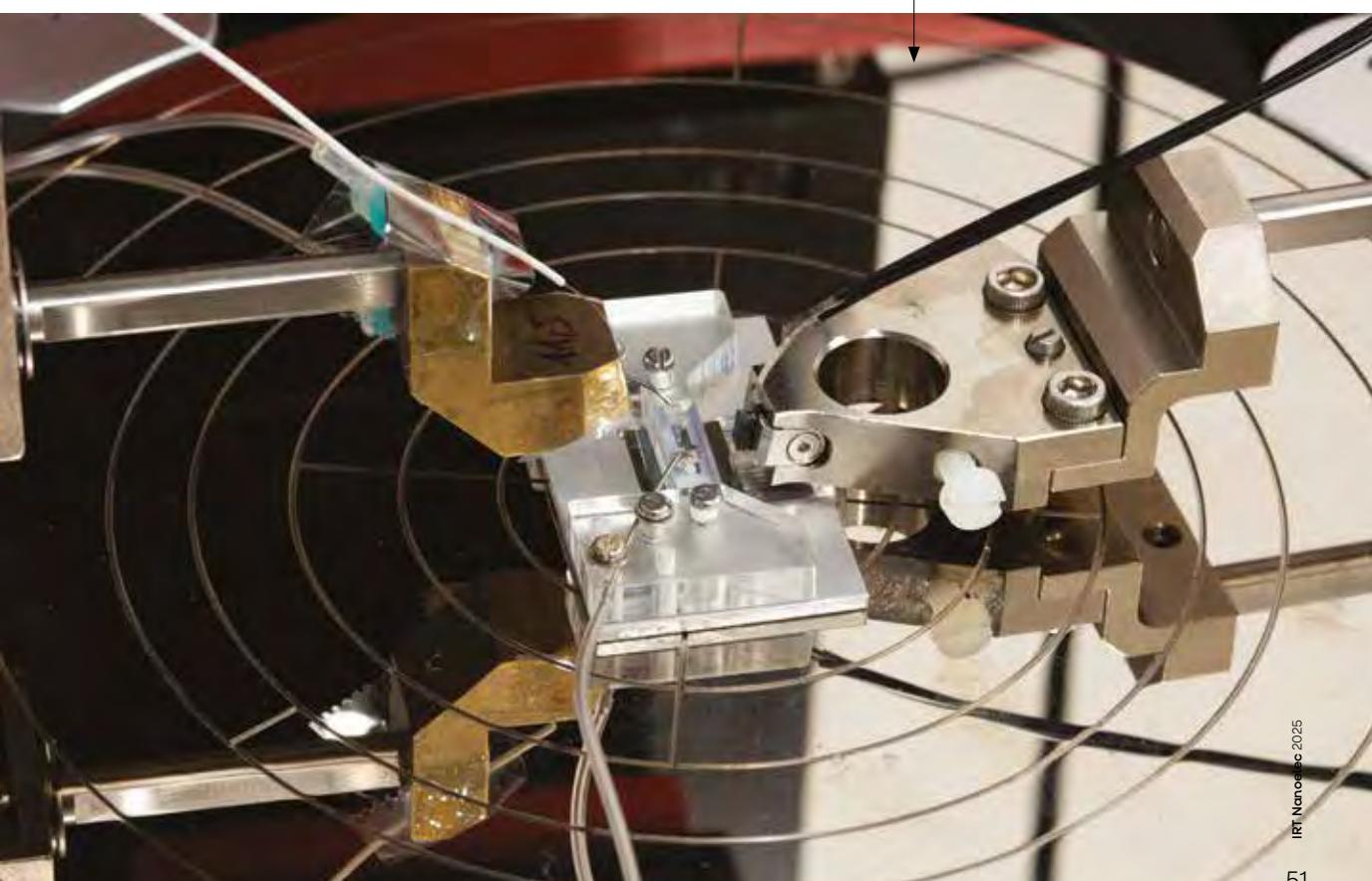

## MZI based ethanol detection

CEA is developing an application measuring the ethanol concentration using an MZI without functionalization on the STMicroelectronics platform, within Nanoelec.

Measurements down to 0.2% alcohol concentration in water were achieved, with a detection limit evaluated at 0.025%. A CMOS photonics on silicon interferometer allows measurement of very small quantities of liquid. The application could be of interest to the agri-food industry and the health care sector.

## Millimeter-length antennas for optical-phased arrays

Improving the scanning accuracy.

A team gathering scientist from CEA, STMicroelectronics, C2N (CNRS & Université Paris-Saclay) studied the behavior of mm-long BIC-effect and dual-layer antennas for silicon photonics based optical phased-arrays (OPAs).

*"The designed and fabricated antennas are simulated and characterized in terms of divergence and directivity in order to achieve precise scanning of the environment," underlines Louise-Eugénie Bataille (STMicroelectronics) as first author of the paper awarded as the "IEEE Silicon Photonics Conference 2024 - Best Student Paper".*

In further work, BIC-effect and dual-layer Si-SiN SWGAs will be integrated in active OPA with carrier depletion phase control. The apodisation of the gratings period is foreseen for next designs. *"This should confirm the potential of scanning the environment with mm long SWGAs in order to expand the OPA to several hundreds of channels and improve the scanning accuracy of OPA-based sensing applications," concludes Louise-Eugénie Bataille.*

## Laser integration

At IEEE Silicon Photonic 2025, Benoit Charbonnier reported the fabrication of SOI integrated III-V lasers using a full 300mm CMOS foundry flow based on work by CEA. After SOI fabrication, III-V Wafers are bonded then processed with CMOS compatible planar BEOL. The lasers exhibit around 70mA threshold, 30dB SMSR with mW range output power. The picture above shows a cross section of the finalized SOI integrated III-V laser.<sup>3</sup>

## Laser integration

Silicon photonics technology and devices for machine learning.

Benoit Charbonnier & al. (CEA-Leti) demonstrated how silicon photonics for AI is suited to use cases where high computational speed is required.

*"CEA Leti's SiPho platform offers state of the art performance for photonic accelerators," underlines Benoit Charbonnier. "In the future, wafer scale (spiking) laser integration could be a good candidate to support full analog neural networks."* These results were presented at Photonic West (January 2024, San Francisco, USA), the conference attracting more than 24,000 attendees from 70 countries.<sup>2</sup>

7/16/2024

7:41:55 PM

1. Silicon Photonics Conference (SiPhotonics, April 2024, Tokyo, Japan).

2. Charbonnier, B., Malhouitre, S., Ramez, V., Bellemín-Comte, A., Ribaud, K., Coppola, G., Faure, T., Dafonseca, J., Thibon, T., & Jany, C. (2024, janvier 30). Silicon photonics technology and devices for machine learning. Photonic West.

3. Charbonnier, B., Bellemín-Comte, A., Adelmini, L., Mathieu, V., Stigliani, M., Castan, C., Philip, P.-E., Hebras, D., Hartmann, J.-M., Ribaud, K., Szélágh, B., & Hassan, K. (2025). 300mm III-V on SOI laser integration process, fabrication and prototyping. 2025 IEEE Silicon Photonics Conference (SiPhotonics), 1-2. <https://doi.org/10.1109/SiPhotonics64386.2025.10985732>

## GaAs for photonic and optoelectronic devices

III-V monolithic integration on silicon compatible with CMOS processes.

The integration of III-V compound semiconductors on a silicon platform has emerged as a transformative approach to enhancing the performance and functionality of photonic and optoelectronic devices.

A team from CNRS/LTM, CEA, Grenoble INP-UGA and UGA associated within Nanoelec presented recent achievements, challenges, and future prospects of GaAs monolithic integration on silicon with specific focus on the development of near-infrared (NIR) emitters and

photodetectors. "We address the challenges associated with III-V monolithic integration on silicon and its compatibility with CMOS processes. These challenges include lattice mismatches, thermal management, and process scalability," explains Thierry Baron (CNRS/LTM) as first author of the paper presented at Smart Photonic and Optoelectronic Integrated Circuits 2024 (January 2024, San Francisco, California).

The latest results were obtained on near-infrared resonant cavity

enhanced photodetector and light emitting devices integrated onto a nominal Si(001) substrate. "The device structures have been optimized by incorporating active regions based on InGaAs/GaAsP strained-layer super-lattices and GaAs/AlGaAs distributed Bragg Reflectors. We also show an alternative solution for fabricating low-threshold emitters based on III-As membranes and lateral injection devices," Thierry Baron says.

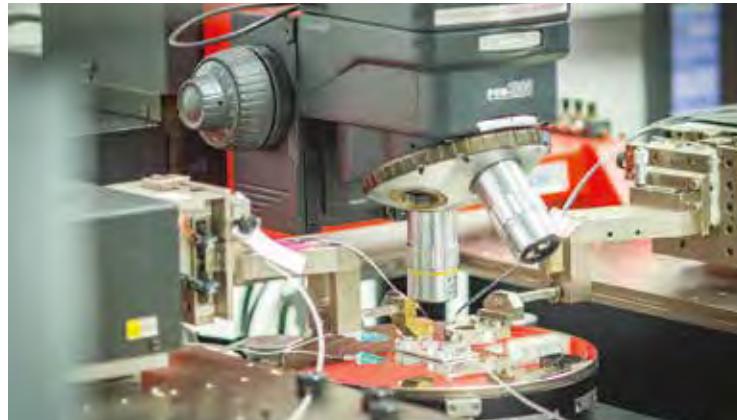

## MZI based ethanol detection

© CEA/A.Havret 2024

PIERRE LABEYRE

(CEA-LETI),

DEVELOPING

A SENSOR FOR

ALCOHOL DOSE

TITRATION

© O. Devise/CEA 2024

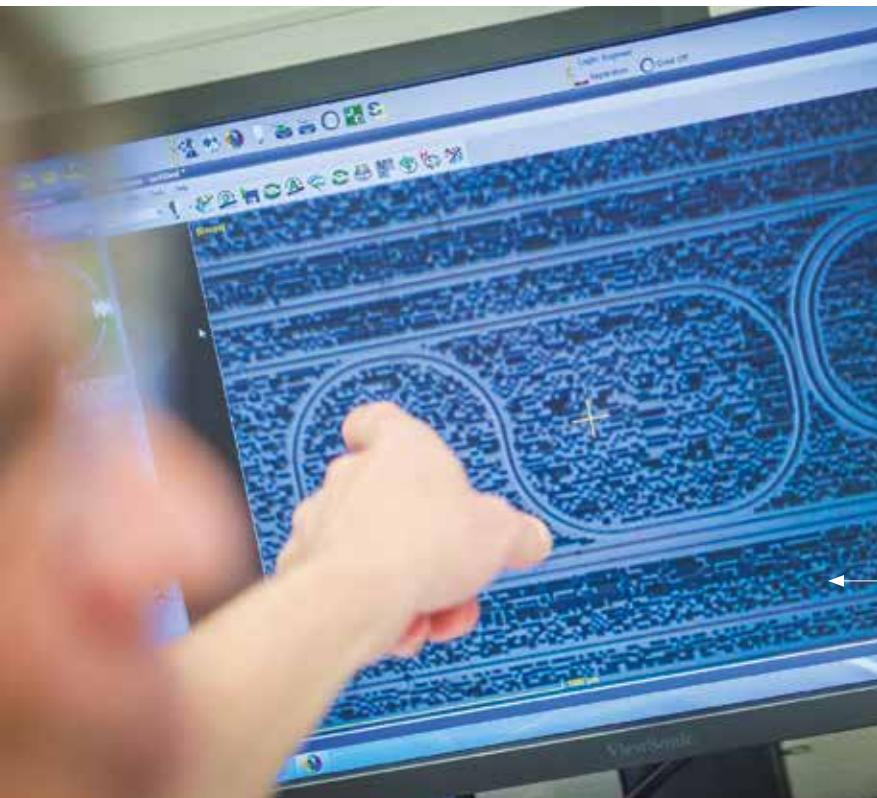

MICROSCOPE VIEW OF THE PHOTONIC MZI CIRCUIT DESIGNED AND PRODUCED AT CEA-LETI FOR ALCOHOL DOSE TITRATION

© O. Devise/CEA 2024

TESTING THE VERY FIRST PROTOTYPE OF A PHOTONIC SENSOR FOR ALCOHOL DOSE TITRATION

© O. Devise/CEA 2024

## Micro light-emitting diodes

### How to Enhance MicroLED Performance.

Within Nanoelec, a team from CEA, CNRS and the Public University of Navarre conducted a synoptic review of III-V Semiconductor Technology to enhance performance of micro light-emitting diodes (microLEDs).

III-V semiconductors, known for their optoelectronic properties and versatile engineering capabilities, play a crucial role in the fabrication of microLEDs. Recent advances in research underscore the fact that the optoelectronic performance of microLEDs can be significantly enhanced using various strategies, such as passivation and distributed Bragg reflectors (DBRs), the incorporation of metamaterials and plasmonics, and the integration of 2D materials. The study was published in Advanced Optical Materials.<sup>4</sup>

## Photonic interconnection for AI

### The LEAF Light product family.

The Scintil Photonics start-up, which uses technologies developed within Nanoelec, is focusing on a multi-wavelength laser source dedicated to co-packaged optics.

*"This circuit will in particular be used to ensure interconnections between routing (switch) and computing (GPU) components, and support the growing needs for communication between AI and Machine Learning chips,"* explains Matthew Crowley, CEO of Scintil Photonics, which is positioning itself on the artificial intelligence and super-computing markets.

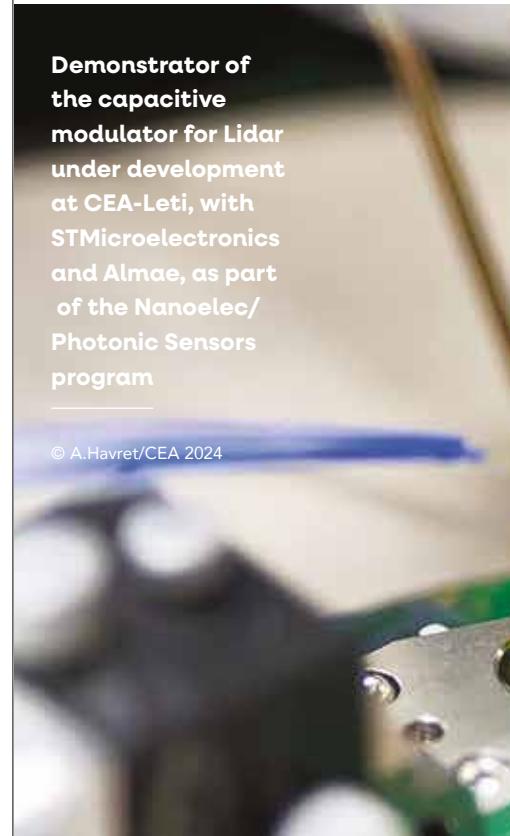

**Demonstrator of the capacitive modulator for Lidar under development at CEA-Leti, with STMicroelectronics and Almae, as part of the Nanoelec/Photonic Sensors program**

© A.Havret/CEA 2024

**Loic Sanchez, engineer at CEA-Leti, preparing to perform hybrid molecular bonding of wafers of III-V materials supplied by Almae on 300mm photonics wafers supplied by STMicroelectronics**

© A.Havret/CEA 2024

**4.**Mouloua, D., Martin, M., Beruete, M., Jany, C., Hassan, K., & Baron, T. (s. d.). Exploring Strategies for Performance Enhancement in Micro-LEDs : A Synoptic Review of III-V Semiconductor Technology. *Advanced Optical Materials*, n/a(n/a), 2402777. <https://doi.org/10.1002/adom.202402777>

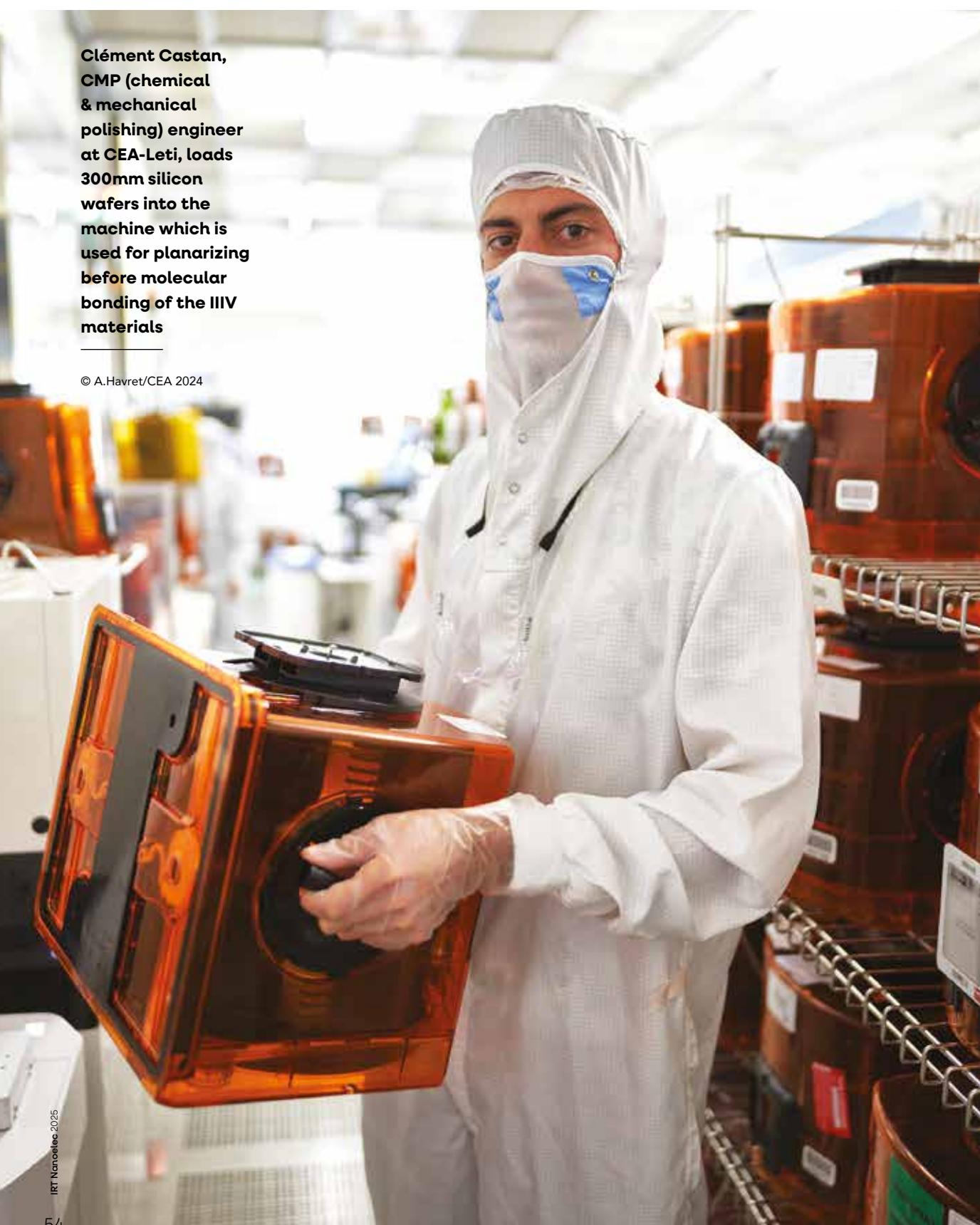

**Clément Castan,**

**CMP (chemical**

**& mechanical**

**polishing) engineer**

**at CEA-Leti, loads**

**300mm silicon**

**wafers into the**

**machine which is**

**used for planarizing**

**before molecular**

**bonding of the IIIV**

**materials**

© A.Havret/CEA 2024

**Tristan Faure,**

technician

at CEA-Leti,

supervises

the III-V

materials

lithography

step for the

capacitive

modulator

demonstrator

© A.Havret/CEA 2024

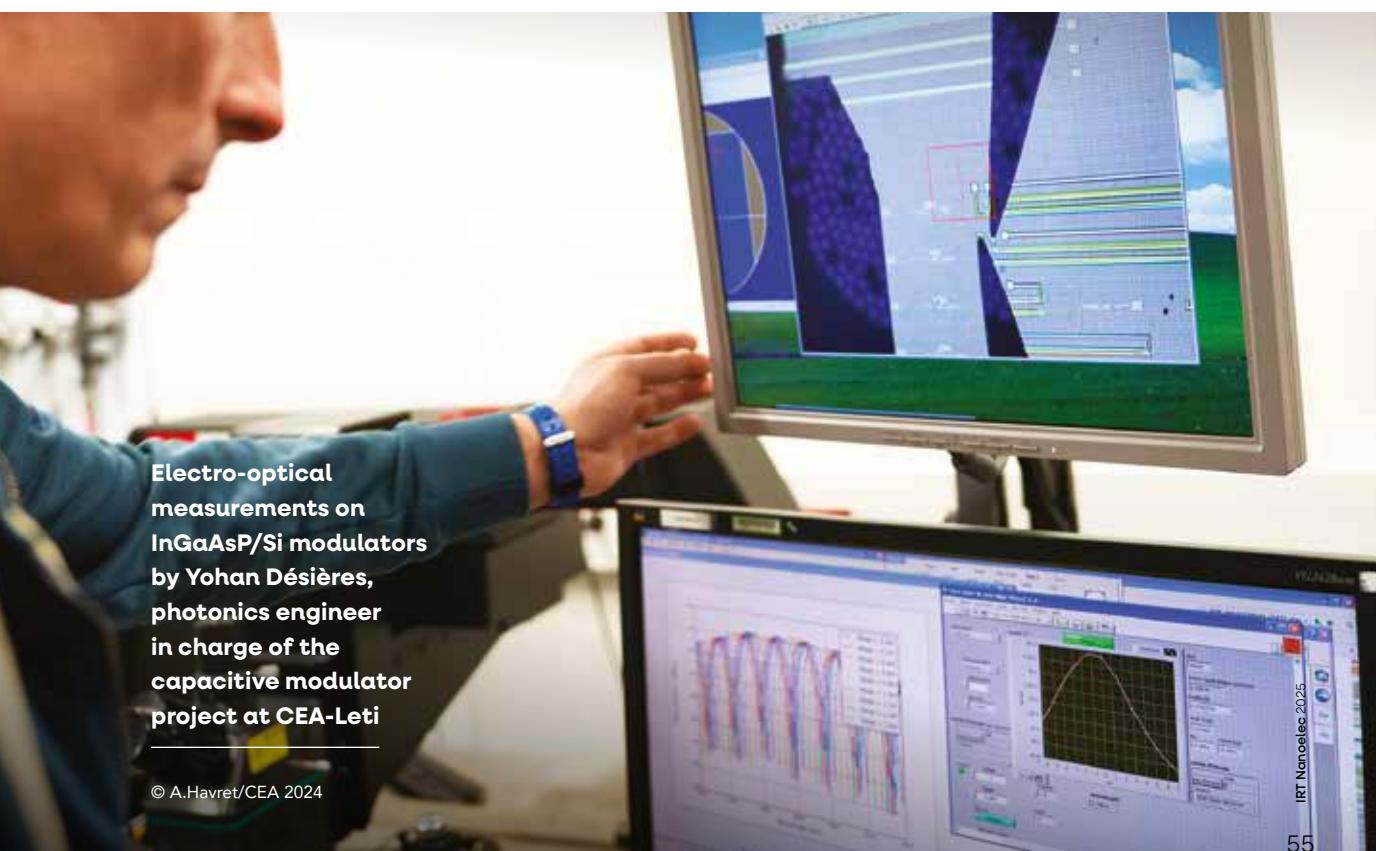

**Electro-optical

measurements on

InGaAsP/Si modulators

by Yohan Désières,

photonics engineer

in charge of the

capacitive modulator

project at CEA-Leti**

© A.Havret/CEA 2024

# The road to the quantum computer

Providing France with the value chain needed to produce scalable electronics for fault tolerant quantum computer.

AUDREY MARTINENT, QUANTUM TECHNOLOGIES PROGRAM MANAGER AT CEA-LETI AND CO-DIRECTOR OF THE NANOELEC/Q-LOOP PROGRAM

© Utapik/CEA, 2025

TANGUY SASSOLAS, QUANTUM COMPUTING PROGRAM MANAGER AT CEA-LETI AND CO-DIRECTOR OF THE NANOELEC/Q-LOOP PROGRAM

© CEA

**T**he Q-Loop program brings together a host of academic and industrial partners to speed up the creation of a universal quantum computer. The aim is to tackle the challenge of scaling up solid-state qubit control and readout systems. The program's actors are focusing on developing software and hardware technologies for the qubit control chain, covering both control electronics and real-time quantum error correction.

The Grand Défi LSQ (LSQ great challenge) was launched by the French Government as part of its National Strategy for quantum technologies, and aims to overcome the obstacles scale up the qubit count. Scaling up entails the ability to acquire industrial processes for mass production and control of standardized, reliable quantum computing qubits. To structure the technological value chain so that the actors needed for these industrial pro-

cesses can emerge, Nanoelec is starting an unprecedented program dedicated to LSQ and directly connected to the French National Quantum Strategy. The aim is to demonstrate a control and readout chain validating the future capability to control a quantum computer with a large number of qubits.

Nanoelec's Q-Loop program focuses on developing the necessary technologies to enable qubits control and readout at scale. It brings together a wide variety of complementary actors along the value chain needed to produce and eventually maintain quantum computer control and command components. It creates strong collaboration between key industrial players in the semiconductor sector, centers of R&D excellence in quantum electronics and emerging actors in the quantum field. The program was launched in 2024 and gathers 65 million euros of public and private funding over a six-year period. •

## Q-LOOP AT A GLANCE

### → Vision

The advent of Quantum computing is deemed to impact many application domains and especially compute intensive R&D tasks, making it a key technology to master at the French & European level to ensure future digital sovereignty

### → Ambition

Structure the technological value chain of actors necessary for the emergence of scalable technologies and industrial processes needed to produce fault-tolerant quantum computers

### → Mission

Take up the technological challenges, in particular for innovative solutions in electronics, integrated photonics and 3D stacking and packaging technologies compatible with operation at cryogenic temperatures, along with hardware acceleration for real-time error correction, and coupling them with accelerated capacity for transfer from R&D to industry

### → Partners

The project involves actors along the value chain including the main French research institutions in the domain, a CAD tools vendor, and a CMOS chips manufacturer, together with national startups specialized in solid-state qubits and enabling technologies

## Program kick-off

### Fruitful interaction

The kick-off meeting was successfully held on November 2024, demonstrating a high level of attendance with about 50 on-site attendees and 30 remote ones.

Technical workshops were organized the same day, dealing with different topics (architecture & system modelling / test needs / cryoelectronics / 3D integration / thermal simulation) and led to fruitful interaction between the attendees from the different entities.

Q-LOOP KICKOFF

© Metras / CEA

## First test vehicles for cryo TSV

### 24 wafers, with different TSV Aspect Ratios.