# III-V/Si Hybrid laser large scale integration in CMOS friendly process

Bertrand SZELAG 06/07/2020

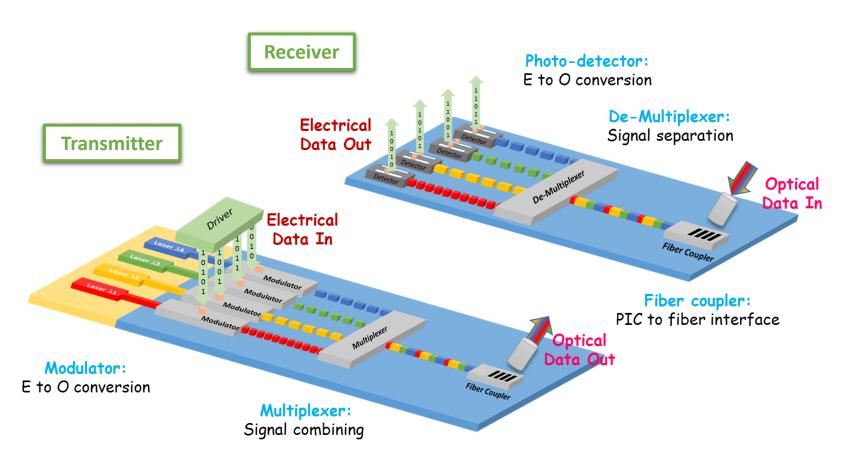

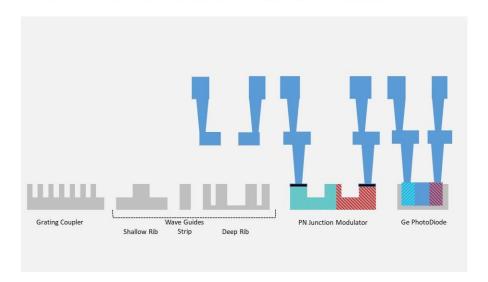

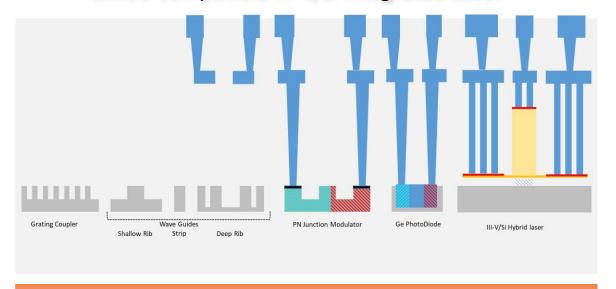

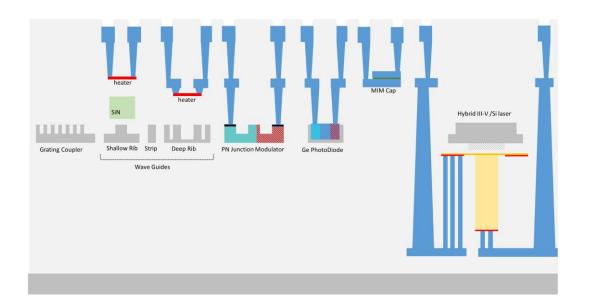

# Silicon Photonics Building Blocks

**Silicon Photonic Links**

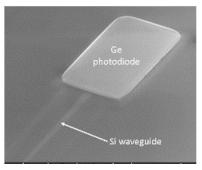

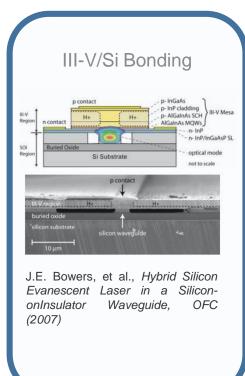

### Which light source on silicon?

Assembly of already processed III-V laser

Luxtera's silicon photonics Optical Engine (100G TX+RX PSM-4)

This work

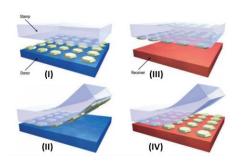

#### Transfer printing

M. A. Meitl, et al, *Transfer printing* by kinetic control of adhesion to an elastomeric stamp, Nature Materials **5**, 33–38 (2006)

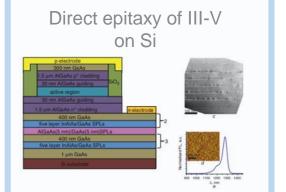

S.M. Chen, et al, 1.3 µm InAs/GaAs quantum-dot laser monolithically grown on Si substrates operating over 100°C, Electronics letters, Vol. 50 No. 20 pp. 1467–1468 (2014)

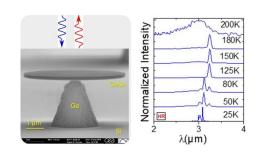

#### Ge(Sn) laser on Si

V. Reboud et al., Optically pumped GeSn micro-disks with 16% Sn lasing at 3.1 µm up to 180 K, Appl. Phys. Lett. 111, 092101 (2017).

Next talk

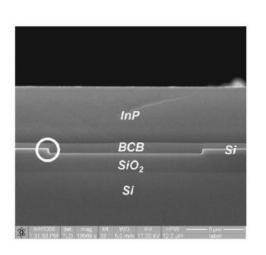

## Direct Bonding vs. Adhesive Bonding

#### **Direct Bonding**

- Fast bonding

- Electrical / optical transparency

- No bonding material (degradation, thickness issue)

- Compatible with CMOS BEOL thermal budget

- Surface roughness and cleanness

Direct bonding: **spontaneous** bonding without "thick" liquid material.

#### Based on:

- intermolecular interactions including Van der Waals forces,

- hydrogen bonds

- strong covalent bonds

#### Wafer bonding for silicon-on-insulator technologies

First reports of successful silicon direct bonding Cite as: Appl. Phys. Lett. 48, 78 (1986); https://doi.org/10.1063/1000 Submitted: 27 August 1985 . Accepted: 23 October 1

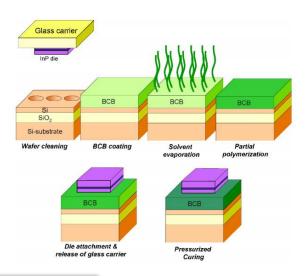

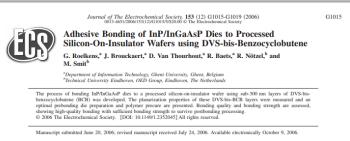

### **Adhesive Bonding**

- Surface roughness and cleanness relaxed requirements

- Post BCB deposition thermal budget < 400°C</p>

- BCB thickness control

- Standard CMOS fab compatibility

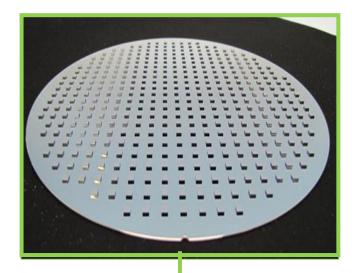

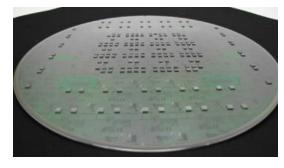

### Laser on Si large scale integration: Die Bonding

InP based photonics

Silicon photonics

Cost advantage of silicon photonics based the use of *CMOS* platforms and large wafer format is no more valid

- Die bonding to cover the full Si wafer

- Localize the III-V material only where it is needed

#### Collective die Bonding with adhesive film

- + Process validated for InP die

- Process compatible with die thickness variations up to 50 μm

- + Compatible with multidie bonding

- Minimum Die Size 1x1mm²

- + Die spacing 400μm

- + Scalable to 300mm wafers

# Technology—Laser integration impact

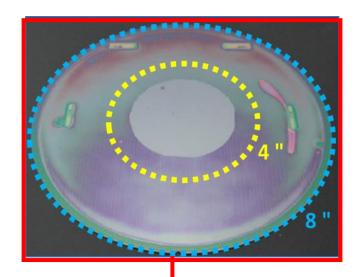

#### Si Photonic Plateform Core Process

- 310nm SOI 2μm BOX

- 193nm DUV lithography

- Multilevel silicon patterning

- 8 Implantations levels

- Selective Germanium epitaxy

- Silicide

- Metal heater

- Planarized BEOL

- 2 AlCu routing levels

- UBM for Cu pillar assembly

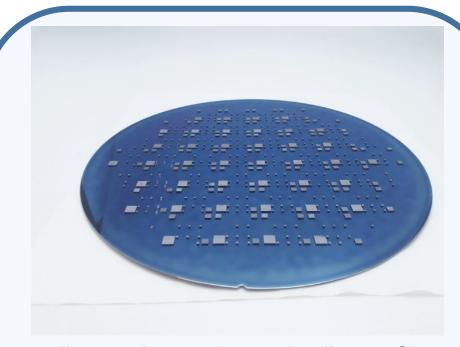

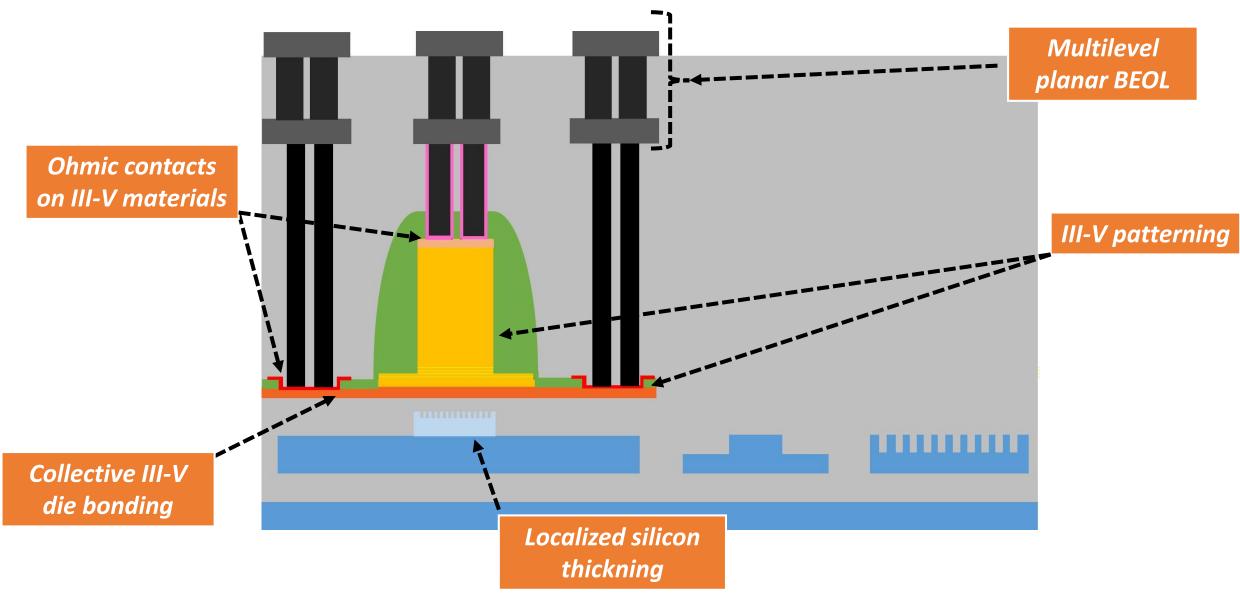

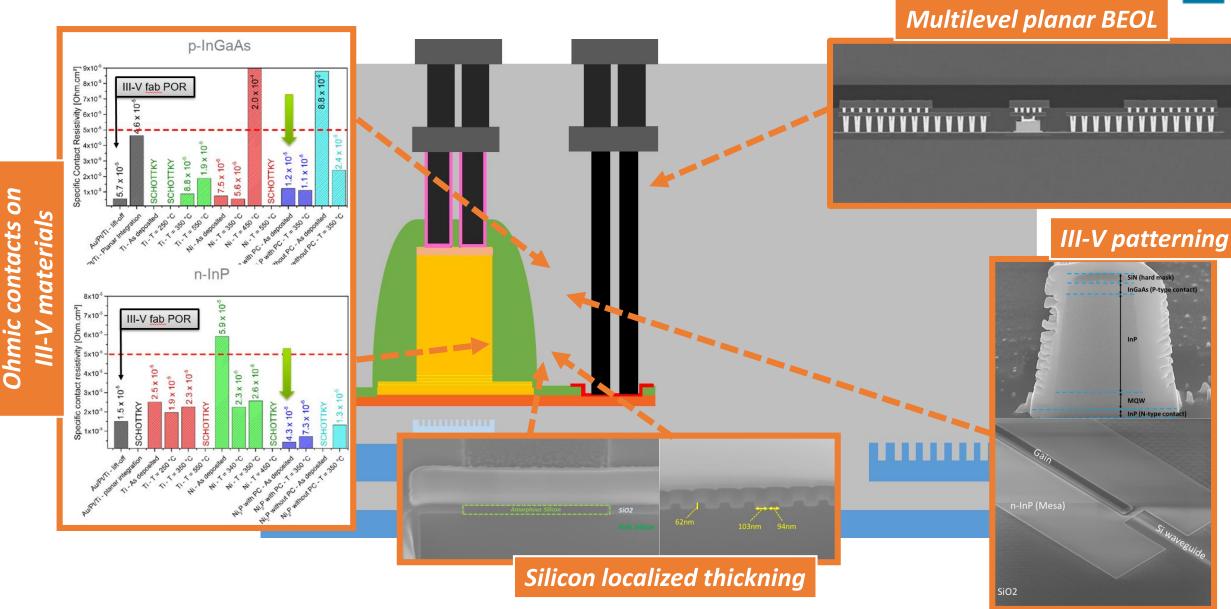

#### CMOS Compatible III-V/Si Integrated Laser

- Collective die bonding

- Additional Laser process steps cmos compatible:

- No noble metals for III-V contacts

- Conventional patterning steps (no lift-off)

- Thick M1 to Silicium contact module

- Localized Si thickening on 310nm SOI:

- Damascene process with Si-Amo or selective Si-epi

- Planarized multi-metal level BEOL

- Additional thermal budget due to laser integration < 600°C</li>

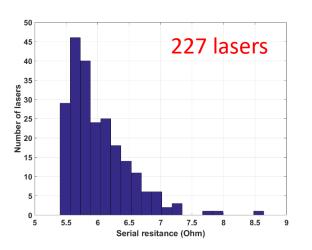

# Large scale integration CMOS friendly process

# Large scale integration CMOS friendly process

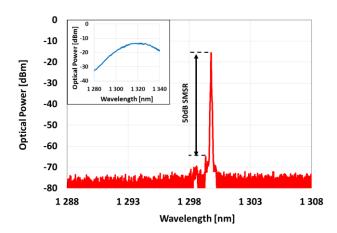

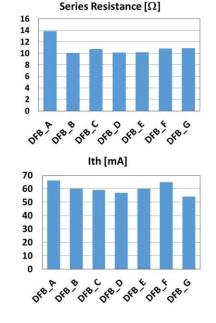

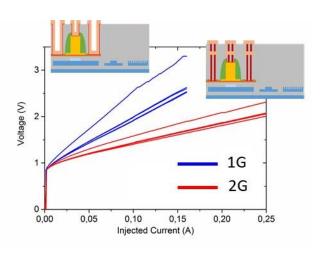

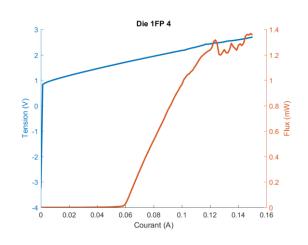

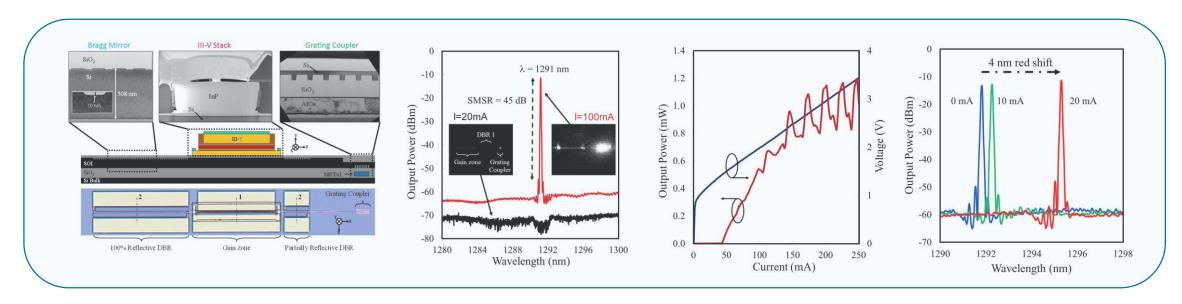

### Optical characterization

#### First generation with one metal level – DFB laser example

#### Second generation with two metal levels – FP laser example

# Hybrid laser back side integration concept

- Integration scheme compatible with any photonic platform

- No impact on the Silicon photonic platform

- Modular integration

- Si photonic platform and laser integration can be done in 2 different fabs

- Only way to have '3D photonic' (SiN or Si level on top of SOI) and laser on the same die

- EIC and Laser @ opposite sides of the PIC

- Demo: Passive + BSI DBR laser done with 100mm process (J. Durel et Al, IEDM 2016)

### Conclusion

- The monolithic integration of a fully CMOS compatible hybrid laser on a 200/300mm silicon photonics platform requires new process module developments.

- CEA-LETI have developed a collective die bonding process with adhesive film:

- Scalable to 300mm wafer

- Compatible with multi die bonding

- Specific cmos compatible metallization's can be used for large scale integration of laser in CMOS compatible process.

- III-V/Si hybrid laser integration on qualified silicon photonic platform has been demonstrated using CMOS compatible process with planarized BEOL.

- Back side integration is a way to integrate laser without any impact on base line silicon photonic platform.

### Acknowledgments

### Silicon Photonic Lab members

L. Adelmini

T. Bria

K. Ribaud

K. Hassan

L. Baud

### LETI's Silicon (and more) technological platform members

P. Brianceau

Ph. Rodriguez

E. Vermande

O. Pesenti

A. Schembri

R. Crochemore,

MC. Roure

S. Dominguez

C. Jany

B. Montmayeul

L. Sanchez

NANO ELEC. Last update in Photonics technology towards edge performance sensors

Live webinar July 6th 2020